### A new Auxiliary Converter Topology with SiC Components for Railway Applications WANG, LUYU

Published: 2016-06-08

Document Version Publisher's PDF, also known as Version of record

Link to publication

Citation for published version (APA):

WANG, L. Ú. Y. U. (2016). A new Auxiliary Converter Topology with SiC Components for Railway Applications (1 ed.) Lund

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

• You may not further distribute the material or use it for any profit-making activity or commercial gain

• You may freely distribute the URL identifying the publication in the public portal?

### Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

**LUND UNIVERSITY**

**PO Box 117** 221 00 Lund +46 46-222 00 00

# A new Auxiliary Converter Topology with SiC Components for Railway Applications

## Luyu Wang

Doctoral Thesis in Industrial Electrical Engineering

Division of Industrial Electrical Engineering and Automation

Department of Biomedical Engineering

2016

Division of Industrial Electrical Engineering and Automation Department of Biomedical Engineering Lund University Box 118 SE-221 00 LUND SWEDEN

http://www.iea.lth.se

ISBN 978-91-88934-70-3 LUTEDX / (TEIE-1078) / 1-119 / (2016)

© Luyu Wang, 2016 Printed in Sweden by Tryckeriet i E-huset, Lund University Lund 2016

### **Abstract**

Smaller size and lower weight are always the targets of the power electronic product development. This work introduces two new topologies of auxiliary converters which have the feature of fewer components and fewer number of energy conversion stages comparing with the conventional auxiliary converter used in railway applications.

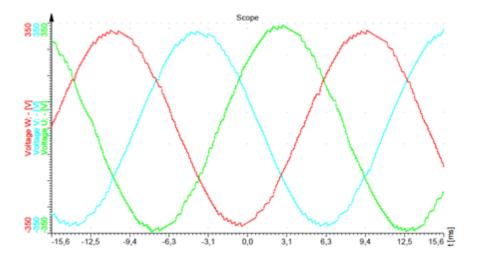

The initial proposal of the proposed new topology is based on the idea which converts the high frequency current pulses into low frequency AC voltages without rectification stages. This thesis starts with theoretical analysis of the initial ideas with the conclusion of two versions of new topology converter proposal: inductive link auxiliary converter and resonant link auxiliary converter. The modulation method strategy for both of those two versions of auxiliary converters are developed within this thesis, the equations for dimensioning the passive components are also given. Simulation shows that the output voltage waveform has very low THD (Less than 3%). The output waveform is similar to a multilevel converter with 'infinite' number of levels.

The inductive link auxiliary converter is able to deliver power with unsymmetrical load due there is no energy stored in the inductive link circuit between two adjacent current pulses. The semiconductor switches have to turn off at high current peaks which introduce high switching losses. To solve this issue the resonant link auxiliary converter is proposed. Due to the added resonant capacitor the resonant link converter is able to store energy in the resonant link circuit between two adjacent current pulses which reduce the total numbers of hard turn off in the semiconductor switches which will reduce the switching losses. On the other hand the resonant link auxiliary converter suffers with output voltage distortion with unsymmetrical load.

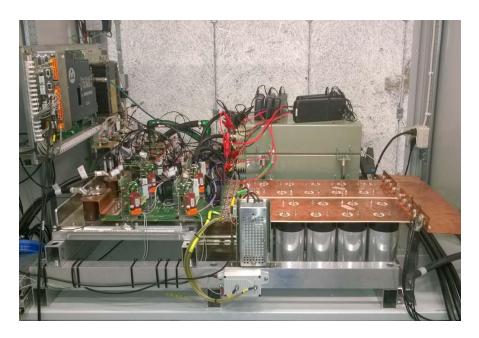

In order to verify the theory which is developed by the theoretical analysis step, prototypes are designed and tested for the inductive link auxiliary converter. A scaled down version prototype is designed to develop the

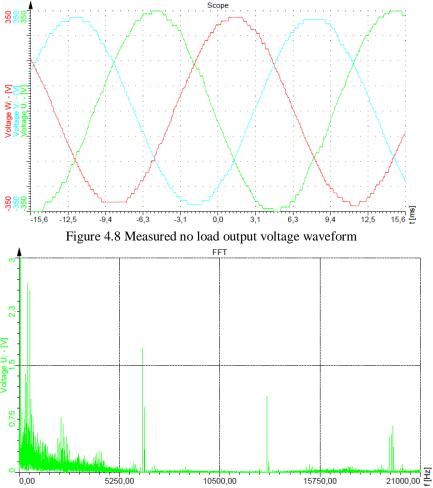

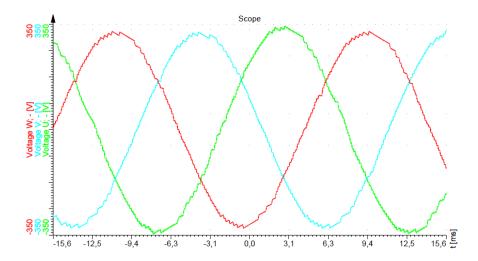

control software and validate the idea of generating low frequency AC voltage from high frequency current pulses. A three phase  $80~\rm kW$  inductive link auxiliary converter is designed and tested. The measured waveforms agree with the simulation model. The measured THD is less than 1% at all measured output power range. The measured efficiency on the complete system is 86% at  $50\rm kW$  output power.

# Acknowledgements

First of all, I would like to thank my supervisor Dr. Hans Bängtsson for all the help he provided during this period and for his trust and encouragement. His suggestions, guidance, advice and comments have been of major importance for me.

I would like to thank Professor Mats Alaküla for accepting me as a Ph.D. student and his encouragements during this period.

I would like also to thank all my colleagues at IEA LTH, Lund University for all the interesting discussions. Special thanks to Getachew Darge for helping me out in the lab. I am also grateful to Dr. Per Karlsson for answering all my power electronics related questions. I wish to express my sincere gratitude to my office mate Conny Högmark for the friendly atmosphere he created and the interesting discussions.

I also would like to thank Tommy Lundberg and Ulf Baly at Bombardier Transportation AB for their kind support during the prototype development. I am also grateful to Tommy Andersson at Infineon for the support of component samples.

Finally, I want to dedicate this thesis to my wife Sijia and to my parents.

Mölndal, March 2016 Luyu Wang

# **Notation**

Frequently used acronym and with name and definition is shown in list below. Acronyis only presented in one chapter are not included in this list.

PF Pulse frequency, The frequency of current pulses

HFAC High frequency AC

FPGA Field Programmable Gate Array

SiC Silicon Carbide HF High Frequency

# **Contents**

| CHAPTE | ER 1 INTRODUCTION                           | 1  |

|--------|---------------------------------------------|----|

| 1.1    | BACKGROUND AND OBJECTIVE                    | 1  |

| 1.2    | Previous work                               | 2  |

| 1.3    | MAIN CONTRIBUTIONS                          | 4  |

| 1.4    | OUTLINE OF THE THESIS                       |    |

| 1.5    | PUBLICATIONS                                | 5  |

| СНАРТИ | ER 2 PROPOSED INDUCTIVE LINK AUXILIARY      |    |

|        | CONVERTER                                   | 7  |

| 2.1    | INTRODUCTION                                | 7  |

| 2.2    | CONTROL ALGORITHM AND MODULATION            |    |

| 2.3    | ANALYSIS AND DESIGN CONSIDERATION           | 19 |

| 2.4    | SIMULATIONS AND CALCULATIONS                | 23 |

| 2.5    | SUMMARY                                     | 35 |

| СНАРТЕ | ER 3 PROPOSED RESONANT LINK AUXILIARY       |    |

| 022.22 | CONVERTER                                   | 37 |

| 3.1    | INTRODUCTION                                | 37 |

| 3.2    | LOAD RESONANT CONVERTERS                    |    |

| 3.3    | PROPOSED RESONANT AUXILIARY CONVERTER       | 42 |

| 3.4    | MODULATION AND CONTROL ALGORITHM            | 43 |

| 3.5    | SIMULATION                                  | 58 |

| 3.6    | SUMMARY                                     | 66 |

| СНАРТІ | ER 4 PROTOTYPE DEVELOPMENT                  | 67 |

| 4.1    | FIRST PROTOTYPE                             | 67 |

| 4.2    | THREE PHASE PROTOTYPE WITH INCREASED POWER  | 72 |

| СНАРТІ | ER 5 HIGH EFFICIENCY DRIVE CIRCUIT OF SIC B | ТT |

|        | SWITCHES                                    |    |

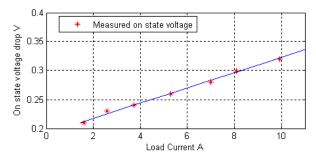

| 5.1    | INTRODUCTION OF SIC BJT                     | 83 |

| 5.2    | Analysis                                    |    |

| 5.3    | IMPLEMENTATION                              |    |

| 5.4    | EXPERIMENTAL RESULTS                        |    |

| 5.5    | SUMMARY                                     | 93 |

| CHAPTER ( | 6 CONCLUDING REMARKS AND FUTURE WORK | 95   |

|-----------|--------------------------------------|------|

| 6.1       | SUMMARY OF FINDINGS                  | 95   |

| 6.2       | FUTURE WORK                          | 96   |

| REFERENC  | ES                                   | . 99 |

| APPENDIX  | A POPULÄRVETENSKAPLIG BESKRIVNING AV |      |

|           | LUYU WANGS DOKTORSAVHANDLING SOM     |      |

|           | SKALL FÖRSVARAS VID LUNDS TEKNISKA   |      |

|           | HÖGSKOLA                             | 107  |

# **Chapter 1 Introduction**

### 1.1 Background and Objective

Public railway transportation is playing an important role in people's daily life in several ways. Especially high speed train is changing people's life. Reduced travel time, town center to town center connection expand people' living area. The author has an experience with high speed trains from Beijing China to his hometown (more than 400km), and the travel time now is one and half hours which was 4 hours before and 3 hours if we chose airplane. At present the highest wheel-rail speed, which is recorded by TGV is 574.8 km/h [1] (Figure 1.1).

Figure 1.1 Example of TGV

The development of modern train is not only focused on the speed but also on the comfortable levels. Lots of auxiliary equipment is needed, such as lighting, fans, air condition machine, and passenger's own devices etc. All these lead to increased power requirement of the auxiliary converter, which normally is a three phase 230/400V 50 Hz power supply.

The function of the auxiliary converter is to generate three phase 230/400V

2 **1.2**. Previous work

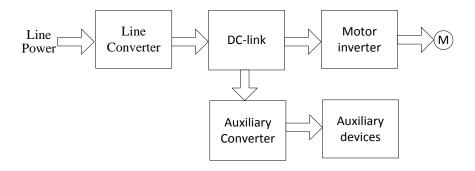

50 Hz power from the train internal DC links, and to provide isolation between the train high voltage side and the consumer side. The power rating of the auxiliary converter can normally vary in several tens of kW. Figure 1.2 shows the position of the auxiliary converter in trains.

Figure 1.2 Position of Auxiliary Converter in Trains

Conventional auxiliary converter needs a 50 Hz transformer and output filters for isolation and for sinusoidal output respectively, which both are bulky components. Reducing volume and weight of the transformer means cost reduction both for the train manufacturer and for their customers. This work focuses on developing a new auxiliary converter topology to reduce the weight and volume of the auxiliary converter.

### 1.2 Previous work

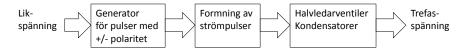

### **Conventional Auxiliary converter**

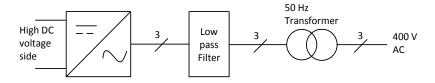

Current design of an auxiliary converter for railway traction application is to use a two level, hard switching three phase inverter [38 39]. The output from the three phase inverter is filtered with a low pass filter to generate sinusoidal output voltage. After the filter a low frequency transformer is used to adapt the voltage and for isolation purpose. Figure 1.3 is the block diagram of conventional Auxiliary Converter.

**1.2**. Previous work

Figure 1.3: Conventional Auxiliary Converter

The low frequency transformer is a bulky component which needs to be replaced.

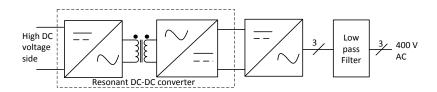

### DC-DC type auxiliary converter

Newer supply system [2-4] [40-42], consisting of redundant resonant DC-DC converter as input and diverse output modules supplied by a common dc intermediate circuit. The input and output side are electrically separated by a light weight high frequency (HF) transformer. See Figure 1.4. Similar activities have been going on to remove the low frequency transformers [5][6] from trains.

Figure 1.4: DC-DC type Auxiliary Converter

This type of converter has 3 energy conversion stages (DC-AC-DC-AC) which results in reduced system efficiency due to the additional losses caused by redundant energy conversions. High frequency link cycloconverters [7, 28-35] have been developed for different supply applications which try to omit redundant energy conversion stages and increase efficiency. The work in [7, 28-36] generates output AC voltage directly from a high frequency AC voltage, which is the output from an H-bridge. The output stage contains 12 transistors and diodes and will have an increased cost on semiconductor devices.

### 1.3 Main contributions

The results and contributions of this thesis are presented in chapter 2 to 4 and discussed in chapter 6. The main contributions of the thesis can be summarized as follow:

- A hard switched new topology of auxiliary converter with reduced number of components is presented.

- ➤ A control method for controlling the hard switched new topology converter is developed. The possibility to implement the control algorithm in FPGA is verified.

- ➤ The energy balance method for controlling the proposed resonant auxiliary converter is given and analyzed and the control algorithm is implemented in simulation model.

- Prototypes are designed and implemented for studying the proposed auxiliary converter.

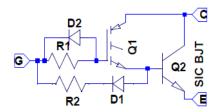

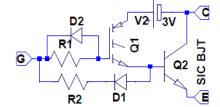

- A new base drive topology for SiC BJT are developed.

### 1.4 Outline of the thesis

Chapter 1 is devoted to a brief outline of this thesis and a short introduction to each chapter is given. This thesis focuses on developing new auxiliary converter topologies for railway applications, which covers concept validation with circuit simulation, hardware implementation and laboratory test.

In this thesis two new topologies are introduced. Chapter 2 introduces the proposed hard switched auxiliary converter. The control method, selection of passive components and losses estimations are included in chapter 2

To reduce the switching losses, one way is to reduce the number of switching times or introducing zero current/voltage switching. The possibility to implement soft switching technique is investigated in chapter 3, and as a result a resonant version of the proposed auxiliary converter is presented. The development is based on simulation. The controlling method is thoroughly investigated in this chapter, and the converter concept is

**1.5**. Publications 5

validated by circuit modeling in LTspice [10].

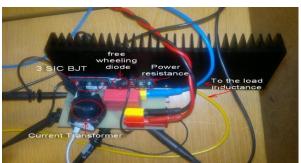

Development of converter prototypes is the next steps after modeling in the simulation software. In this thesis two converters prototyped are presented. A small down sized prototype are implemented for developing the control software for the proposed hard switched converter. Then a bigger prototype is implemented to study how the new topologies converter behaves in practice. This part of the work is included in chapter 4

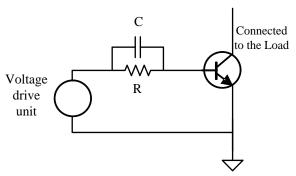

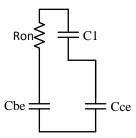

Chapter 5 has investigated how to control Silicon carbide BJT with high efficiency. A new drive circuit topology is developed in chapter 5.

The thesis ends with some concluding remarks and suggestions for future research in Chapter 6.

### 1.5 Publications

Part of the work presented in this thesis has been presented in the following publications:

Wang, L., Karlsson, P, Bängtsson, H. (2013), "A new isolated, output filter free DC-AC converter topology". 15th Conference on Power Electronics and Applications (EPE13), Lille, France, Sept. 3-5, 2013.

Wang, L., Bängtsson, H. (2012), "How to control SiC BJT with high efficiency?". 7th International Conference on Integrated Power Electronics Systems (CIPS2012), Nuremberg, Germany, March 6-8, 2012.

Ottosson, J., Wang, L. (2012), "Comparison of cooling requirements for Si and SiC based inverters in a hybrid vehicle application". International Conference and Exhibition for Power Electronics, Intellegent Motion, Renewable Energy and Energy Management, Power Electronics South America 2012, Sao Paulo, Brasil, Sept. 11-13, 2012

# Chapter 2 Proposed Inductive Link Auxiliary Converter

### 2.1 Introduction

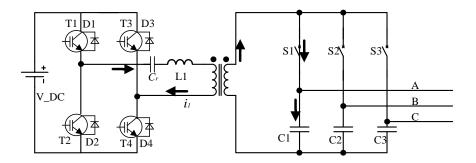

As stated in the previous chapter the DC/DC type auxiliary converter has 3 energy conversion stages: A full bridge converts the DC link voltage to a HFAC (high frequency AC), this conversion provides isolation between input and output. The HFAC is converted to a DC voltage by a rectifier circuit. The DC voltage is then converted in a three phase inverter to an AC voltage with the 50 Hz fundamental frequency. These three stage energy conversion are considered as redundant. Redundant energy conversions not only cause more losses but also require additional components, the system becomes bulky. The idea of this work is to omit the redundant conversion stage and to generate the 50Hz AC output voltage directly from the intermediate product HFAC.

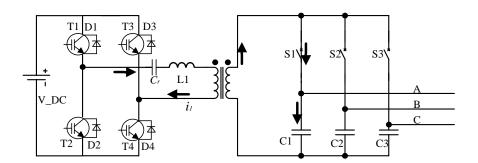

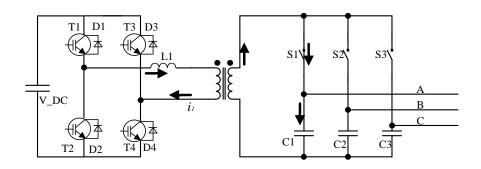

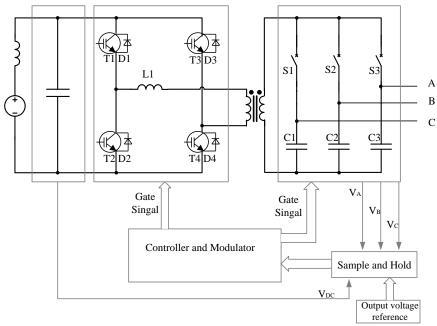

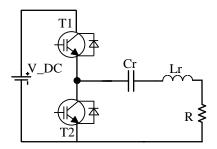

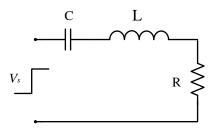

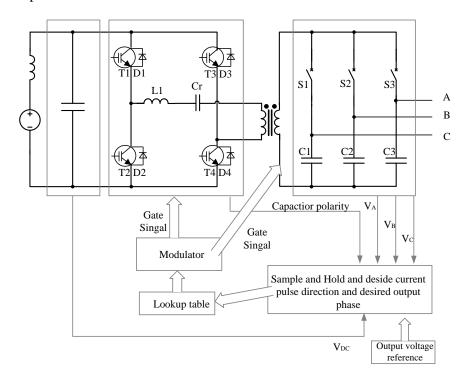

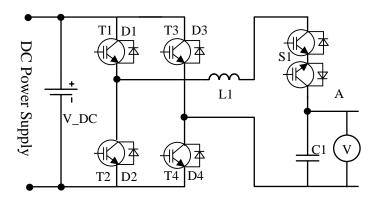

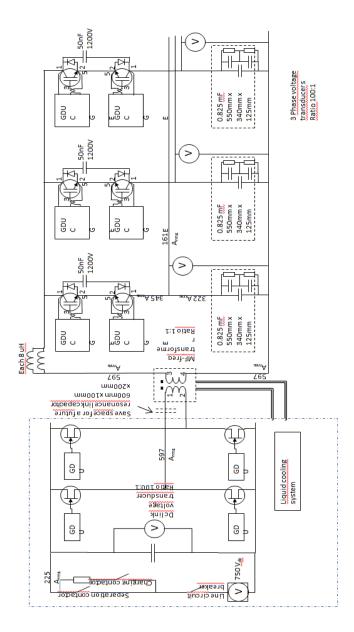

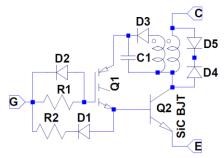

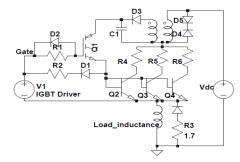

Figure 2.1a Proposed resonant auxiliary converter topology

**2.1**. Introduction

Figure 2.1b Proposed inductive link auxiliary converter topology

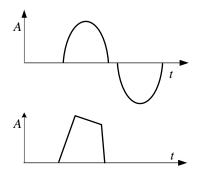

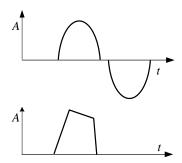

Figure 2.1c Example of current pulses

The proposed auxiliary converter topologies are shown in Figure 2.1a&b. The input stage is a 4-quadrant converter and is connected with either an inductor (inductive link) or series resonant circuit (resonant link). A high frequency transformer is used for galvanic isolation. The output stage is formed by bidirectional switches and output capacitors. The function of the input stage is generating high frequency current pulses; either positive or negative depending on the need of the output stage. The current pulses can be selected by the bidirectional switches to charge/discharge the output capacitors. Arrows in Figure 2.1a&b is an example showing the current path when the output capacitor of phase A is charged.

There are several ways to generate the HFAC pulses. The first thought is using a series resonant circuit to generate the resonant current pulses which is shown in the upper part of Figure 2.1c. The working principle of the

**2.1**. Introduction 9

resonant link for creating current pulses is similar to a load resonant converter [8][9], and it has a potential to reduce losses by using soft switching technique. However, this method cannot be applied directly to our application since the voltage over the series resonant circuit and especially the voltage on the output side, both are AC voltages, which is different from load resonant converters. A dedicated modulation method is needed for controlling the resonant circuit. One drawback of the resonant circuit is that there is always a negative current pulse followed by a positive pulse since the polarity of the current pulse are related to the polarity of the resonant capacitor. This limits the freedom for selecting the polarity of the required current pulses, thereby creating problems when the three phase loads are not symmetrical.

By removing the resonant capacitor of the series resonant circuit, the HFAC pulses could be generated by the inductive link method. With the inductive link method, the polarity of the current pulses can be either way. This feature guarantees that the converter can work with unsymmetrical loads. The drawback of this method is that hard switching at peak current might cause more losses. The inductive link method is thoroughly investigated in this chapter, and the resonant method will be analyzed in chapter 3.

The proposed auxiliary converter topologies require less components both active and passive compare to the DC-DC type auxiliary converters since it has lower number of energy conversion stages. The saved components and added components are summarized in Table 2.1.

| Table 2:1: Baved and added components |                          |  |  |

|---------------------------------------|--------------------------|--|--|

| Saved components                      | Added components         |  |  |

| 4 rectifier diodes                    | 3 bidirectional switches |  |  |

| 2 DC link capacitors                  | 3 output capacitors      |  |  |

| Three Phase IGBT module               |                          |  |  |

| Three phase output filter             |                          |  |  |

Table 2.1: Saved and added components

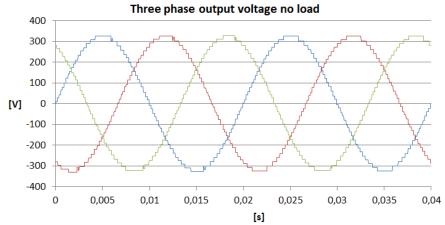

The calculated output voltage is shown in Figure 2.2. This is to verify the possibility to generate the requested output ac voltages with current pulses. This verification is using simplified resonant current packages (Figure 2.1c) which are formed from a constant resonant current source and without load (Figure 2.2a) and with resistive loads (Figure 2.2b) on the three phase side.

10 **2.1**. Introduction

Sinusoidal output voltage with a reduced amount of low order harmonics is a feature of our proposed topology.

Figure 2.2a Calculated no-load output voltage

Figure 2.2b Calculated full load output voltage

### 2.2 Control Algorithm and Modulation

This section focuses on developing the control algorithm and modulation method for the inductive link version auxiliary converter. The generation of current pulses, the calculation of the transistor duty ratios based on the need from the outputs, are investigated. The modulation and the control algorithm are also thoroughly discussed.

### The current pulses

The intermediate product HFAC is the high frequency current pulses (see Figure 2.3). The current pulses can be considered as discrete charge carriers. These discrete charge carriers are selected and delivered to the output capacitors via bidirectional switches to generate the sinusoidal output voltages.

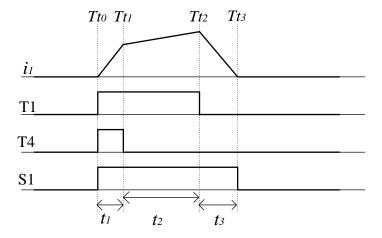

Figure 2.3 Operational waveform

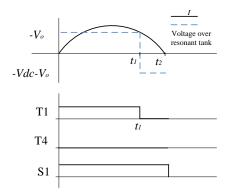

Figure 2.3 gives the operational key waveform for generating the current pulses. Assume a positive charge is required for  $C_I$ , the transistors T1 T4 and S1 in Figure 2.1b shall be switched on to start generating the current pulse. One switching period T is divided into 3 time intervals labeled  $t_I$ ,  $t_2$  and  $t_3$ , respectively. At  $t_0$  transistors T1, T4 and S1 are turned on. The current  $i_I$  starts to increase from zero. During this time interval the energy is fed from dc-link to the inductor L1 and to the output capacitor

C1.Transistor T4 is switched off at time  $Tt_1$  and the current starts freewheeling via T1 and D3. During this time interval the energy is transferred between L1 and the output capacitor C1. After  $Tt_2$  transistor  $T_1$  is turned off, the current starts to decrease via D3 and D2 until it reaches zero at  $Tt_3$ . In this period the energy is fed from  $L_1$ to the DC-link and the capacitor  $C_1$ .

The current pulses are charge carriers, it is essential to study the charge carry ability of a single current pulse. Figure 2.4 shows examples of 3 types of current pulses. The charge Q that is carried by the current pulses is equal to the area of the current package.

Here are the inputs to calculate the charge Q:

- I) The current pulse interval has a length of *T*, *T* is the same for all current pulses and *T* is defined as the pulse period in this work.

- II) Assuming the variation of the output voltage and the DC link voltage during one current pulse interval is small and can be neglected. The current derivatives *a*, *b* and *c* can be considered as constant during one current pulse.

- III)  $V_{dc}$ ,  $V_{out}$ , and L are the DC-link voltage, the output voltage and the inductance of L1respectively.

- IV) Assuming a positive charge is needed from an output phase *A* as shown in Figure 2.1b.

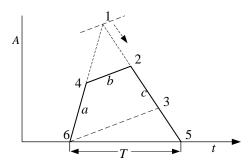

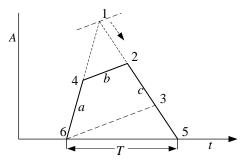

There are three types of current pulses, shown in Figure 2.4, depending on when the transistors are turned off and turned on:

- 1) If two transistors in Figure 2.3 and 2.1 are turned off at the same time (*tz* is zero), the shape of the current pulse is a triangle (triangle 1-5-6) and the area within the current envelope is the largest in all those three type of current pulse described in this section. This type of current pulse carries the most charge among those three type of current pulses.

- 2) If only one transistor has been turned on at the beginning (*ti* is zero), the shape of the current pulse is a triangle (triangle 3-5-6) and has

the smallest area. This type of current pulses carries the least charge among those three types of current pulses.

3) If two transistors are not turned off at the same time as shown in Figure 2.3. The current pulse has a shape of quadrilateral (2-5-6-4). The size of the area is between type 1 and 2.

The maximum value  $Q_{max}$  can be given by calculating the area of triangle from type 1) which gives (2.1). The minimum charge  $Q_{min}$  is more complex than the calculation of  $Q_{max}$ . In the situation which is shown in Figure 2.4a, the  $Q_{min}$  can be calculated by (2.2).

Figure 2.4a Example of a current pulse

$$Q_{max} = \frac{V_{dc}^2 - V_{out}^2}{4V_{dc}L}T^2$$

(2.1)

$$Q_{min} = \frac{-bc}{2(b-c)}T^2 \tag{2.2}$$

(2.2) gives the equation of how to calculate the minimum charge of the inductive link topology. However (2.2) is only applicable for one special condition. Actually the current pulses can be classified in two conditions as described below:

Figure 2.4b Example of a current pulse

Figure 2.4b shows a current pulse, which has the same polarity as the output voltage. In this case  $Q_{min}$  equals to the area of the triangle and the value is given by.

$$Q_{min} = \frac{-bc}{2(b-c)} T^2$$

(2.18)

Figure 2.4c shows the case when the current pulse has the opposite polarity as the output voltage.  $Q_{min}$  can be calculated as (2.19)

Figure 2.4c Example of a current pulse

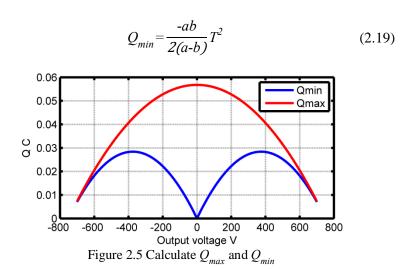

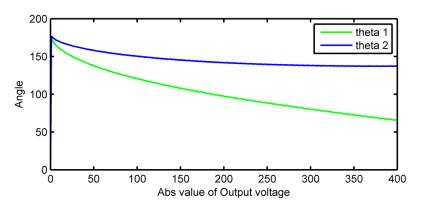

Figure 2.5 shows the calculated  $Q_{\rm max}$  and  $Q_{\rm min}$  for a 100 kW auxiliary converter The  $Q_{\it max}$  reaches its peak when the output voltage is zero and drops with increased absolute value of the output voltage. The charge carry ability is related to the voltage difference between the DC-link voltage and the absolute value of output voltage according to (2.1). The output voltage must be lower than the DC link voltage to transfer power from input to outputs.

### Calculating transistor duty ratios

The duty ratio of each transistor is calculated from t1 t2 and t3 which is shown in Figure 2.3. The duty ratios of transistor  $T_1$ ,  $T_4$ /  $T_2$ ,  $T_3$  are given in (2.3) and (2.4) respectively

$$D_I = \frac{t_I}{T} \tag{2.3}$$

$$D_{I} = \frac{t_{I}}{T}$$

$$D_{2} = \frac{t_{I} + t_{2}}{T}$$

(2.3)

The calculation of  $t_1$ ,  $t_2$  and  $t_3$  is described here. Assuming that the current pulse period is T; a, b and c are the current derivatives during the time intervals  $t_1$ ,  $t_2$  and  $t_3$ , respectively. Q is the charge which is required by capacitor  $C_1$  from the load. The sum of  $t_1$ ,  $t_2$  and  $t_3$  should be equal to T which gives (2.5). The current  $i_1$  starts at zero and ends at zero which gives (2.6). The time integration of the current pulse equals to the required charge Q which is shown in (2.7).

$$t_1 + t_2 + t_3 = T \tag{2.5}$$

$$at_1 + bt_2 + ct_3 = 0$$

(2.6)

$$\frac{1}{2}at_1^2 + \frac{1}{2}ct_3^2 + \frac{1}{2}(at_1 - ct_3)t_2 = Q$$

(2.7)

Table 2.2 gives the solutions of these second order equations. According to Table 2.2, at least one square root function is needed by the controller, which requires more computation resource to implement the control algorithm. A pre-calculated look-up table might be a good way to reduce the requirement on the micro controller side.

Table 2.2 Solutions of switching profiles

|    | Solution 1                        | Solution 2                   |  |  |

|----|-----------------------------------|------------------------------|--|--|

|    | <i>Q</i> >0                       | Q<0                          |  |  |

| t1 | $t_{I} = -\frac{F + Tc}{a - c}$   | $t_1 = \frac{F - Tc}{a - c}$ |  |  |

| t2 | $t_2 = \frac{F}{a - b}$           | $t_2 = -\frac{F}{a-b}$       |  |  |

| t3 | $t_3 = -\frac{F - Ta}{a - c}$     | $t_3 = \frac{F + Ta}{a - c}$ |  |  |

|    | $F = \sqrt{-(acT^2 + 2Qa - 2Qc)}$ |                              |  |  |

### **Control algorithm**

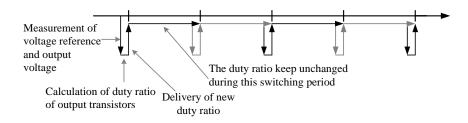

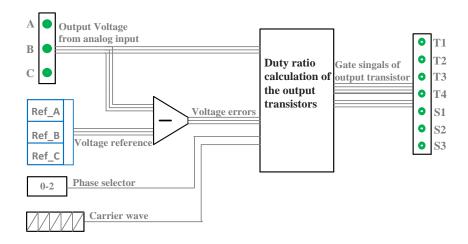

Figure 2.6 shows a simplified control chart. The output voltage and the voltage reference are measured and sampled prior to the beginning of each switching period. Calculation of the new duty ratios is done in a short time interval. New calculated duty ratios are updated to the transistors and are kept unchanged in the coming switching period. The calculation time shall be kept as short as possible to reduce the delay time which requires a fast micro controller. If the controller is slow, a compensation for the calculation time delay shall be taken in to account.

Computer technique has developed substantially in the last decades. With powerful micro controllers, and fast control algorithm can be implemented for today power electronic converter. Reference [9] is an example of direct current control implemented in Field Programmable Gate Array (FPGA).

Figure 2.6 Time chart of control algorithm

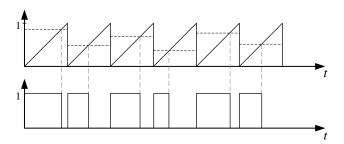

Figure 2.7 Carrier waveforms and transistor gate signals

The generation of a current pulse is shown in Figure 2.1c, transistors T1 and

T4 shall be turned on at the same time but be turned off at different time. Saw tooth carrier with positive slope is selected for this purpose. Figure 2.7 explains how the gate signal is generated by carrier waves and transistor duty ratios.

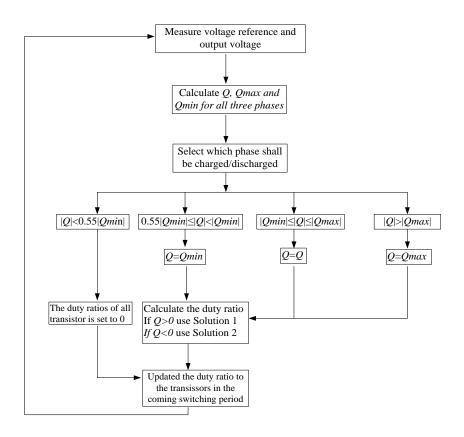

Until now we have collected enough information to control our proposed hard switched auxiliary converter. Prior to each switching period, voltage references and output voltages of three output phases are measured and sampled. Based on the sampled data, the required charges Q,  $Q_{max}$  and  $Q_{min}$  can be calculated afterwards for all three phases.

There are mainly two ways to decide which phase that shall be charged. It is a nature thought to treat output phases equally and each output phase is charged/discharged every third switching period. A more optimal way is to charge/discharge the phase that has the largest voltage error. In our simulation models the first method is chosen to reduce system complexity.

The next coming step is to define the input for calculation of the duty ratios of the output transistors. The details of how to define Q based on the sampled data is shown in Figure 2.8.

Calculation of the duty ratio is done in the next step by using the equation from Table 2.2 and (2.3) and (2.4). After that the duty ratio is calculated and applied to the transistor.

Figure 2.8 Control flow chart for inductive link auxiliary converter

### 2.3 Analysis and Design Consideration

### Value of passive components

The function of the output capacitor is similar to an output filter and an energy buffer. It converts the current pulses to sinusoidal voltages. The capacitance of the capacitor is related to the maximum output voltage ripple and the THD (total harmonic distortion). Larger output capacitor reduces the output voltage ripple and the THD. For a three phase converter as shown in Figure 2.1b, three output phases share the current pulses, in average for

one output phase the capacitor is charged every third pulse period. Assuming the output capacitor is charged every third pulse period. In most severe conditions which correspond to the moment when the load current reaches its peak value, the output capacitor should keep the output voltage neither to drop or increase more than the maximum allowed voltage ripple between two current pulses. Assuming  $Current_{amp}$ ,  $T_{charge}$ ,  $\Delta V$  and  $V_{rms}$  is the maximum output current amplitude, the charging period of each single output phase, the maximum allowed voltage ripple and the nominal output voltage respectively. The value of the output capacitor can be calculated as below.

$$\Delta V \ge \frac{Current_{amp} \times T_{charge}}{C} \tag{2.8}$$

Rewriting (2.8) gives (2.9)

$$C \ge \frac{Current_{amp} \times T_{charge}}{\Delta V}$$

(2.9)

Since:

$$Current_{amp} = \sqrt{2} \frac{P_{max}/3}{V_{rms}}$$

(2.9a)

$$T_{charge} = \frac{3}{F} \tag{2.9b}$$

The output capacitance is given by (2.10)

$$C \ge \frac{\sqrt{2} \frac{P_{max}}{V_{rms}}}{\Lambda V \times F} \tag{2.10}$$

The inductance of inductor  $L_1$  in Figure 2.1 is related to the amplitude of the current pulses. Larger inductance reduces the amplitude of the current pulse for the same pulse period. Considering the most severe conditions, which are when the output current reaches its peak value, the charge removed by the output current shall be compensated by the charge delivered by current pulse which gives (2.11)

$$Q_{max} \ge Current_{amp} \times T_{charge}$$

(2.11)

Substitute (2.1) into (2.11) will give:

$$L \le \frac{(V_{dc}^2 - V_{out}^2)V_{rms}}{4\sqrt{2}V_{dc}P_{max}F}$$

### **Reactive current**

There are current pulses circulating between output capacitor and DC-link capacitor to maintain the output voltages. The output capacitor can be considered as a capacitive load of the converter, the corresponding load current can be calculated by (2.13), where V and f are the amplitude and the frequency of the output voltage respectively. The current is 90 degree heading the output voltage. This reactive current is the main root causes losses of the proposed auxiliary converter during standing still. It is essential to keep the output capacitance as low as possible to reduce the reactive current and the losses.

$$I_{rea} = V \times 2\pi fC \tag{2.13}$$

### Amplitude of current pulses

Current pulses are the intermediate product in the proposed auxiliary converter energy conversion stage. The amplitude of the current pulses affects the total switching loss and the rms value of the current pulses affects total conduction loss. Those two parameters are essential for dimensioning the semiconductor power module and the transformer.

See (2.14), assuming that the reactive current we have discussed in last subsection is smaller than the amplitude of the load current and thus can be neglected. The current pulses compensate the charge which is removed by the load current.

$$\int_{0}^{T} I_{pulse} dt = \int_{0}^{3T} I_{load} dt$$

(2.14)

The shape of a current pulse is either a triangle or a trapezoid. The load current  $I_{load}$  is a low frequency current, it can be considered as constant during one switching period. (2.14) can be rewritten as (2.15) and (2.16). (2.15) and (2.16) correspond to a triangle shaped current pulse and a trapezoid shaped current pulse respectively, where  $I_{amp}$  is the amplitude of the current pulse. Combining these two equations together gives (2.17).

$$I_{amp} = I_{load} \times 6 \tag{2.15}$$

$$I_{amp} > I_{load} \times 3$$

(2.16)

$$I_{load} \times 3 < I_{amp} \le I_{load} \times 6 \tag{2.17}$$

According to (2.17) the amplitude of the current pulses is much larger than the amplitude of the output current. In the proposed inductive link auxiliary converter the transistor needs to switch off at peak current of the current pulses. The switching losses are one of the main loss sources of the proposed inductive link auxiliary converter.

For delivering the same amount of charge, a current pulse with high big peak

value has higher rms value comparing to continuous constant current. For the same principle, narrow current pulse with bigger peak value has higher rms value than a wide current pulse but with low peak value. So the amplitude of current pulses shall be kept as low as possible to reduce the conduction losses. In other words, for transfer the same amount of charge, several small current pulses with low current peaks are better than single pulses with high peak in order to reduce the conduction losses.

### 2.4 Simulations and Calculations

Simulations are used to evaluate the control algorithm which is discussed in section 2.2. Parameters of passive components are calculated by using the equation developed in section 2.3. The Simulations are used to simulate the spectrum of output waveform and to optimize the dimension of the output capacitors and the inductor. The simulation is implemented in LTspice [10]. The Calculation which is done in Matlab is used to estimate the semiconductor losses based on silicon IGBTs.

#### General simulation model

The general simulation model used throughout in all simulations is shown in Figure 2.9. Note that the loads is not included in this circuit, they are formed by three sinusoidal current sources which are connected to nod A, B and C respectively. The amplitude and the phase of the load is adjustable and can simulate different load conditions.

To reduce the complexity of the model, ideal switches and diodes are used for all transistors and diodes. Since ideal components are used, simulation of the converter losses is not included in this simulation model. The losses estimation of the semiconductor devices is carried out by using Matlab.

The function of the sample and hold block is to sample the output voltages, the voltage references and the DC link voltage with a sample frequency equal to switching frequency. It guarantees that the inputs of the controller and the modulation block are not changed during the entire switching period. It is important since the duty ratios for all transistors shall be kept unchanged during one switching period, as stated in section 2.3.

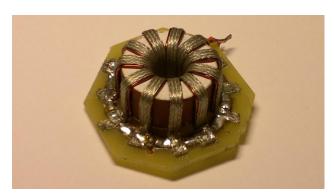

The capacitors in this simulation model are also ideal components. The

value is defined by the equation developed in section 2.3. The parameters of the transformer used in the simulation are from an HF transformer of an auxiliary converter. The inductor is formed of the leakage inductance of the transformer and an ideal inductor L1.

Figure 2.9 Simulation model

### **Pulse Frequency**

The pulse frequency is an essential parameter and is defined as 1/T, where T is the current pulse period. In one pulse period only 2 transistors out of four in the 4-quadrant converter, and 1 bidirectional switch out of 3 in the output phases have switched.

(2.10) and (2.13) tell that higher pulse frequency will result in a reduced output capacitor and a reduced reactive current. Higher pulse frequency also has advantages like the transformer will be lighter and smaller. On the other hand, higher pulse frequency causes higher switching losses, and

commercial semiconductor devices have their own limitation on switching frequency [11]. The maximum switching frequency for a 1200V Silicon IGBT is around 10/20 kHz. For Silicon Carbide (SiC) transistors: JFET, MOFET, BJT, up to 100 kHz switching frequency is reported [12].

Table 2.3 shows the selected pulse frequency (PF) and the corresponding capacitance of the output capacitor and the inductance of the inductor  $L_1$  for a converter with 100kW peak power and 750V DC link voltage. At 10 kHz the output capacitor is 1.53 mF, the reactive current has amplitude of 156A which is 75% of output peak current, this is a high value and leads to high no load losses. With a doubled pulse frequency, the reactive current is reduced to 78A and the value is 39A at 40k Hz, Another way to reduce the reactive current is to reduce the quality of output voltage by using a smaller output capacitor. This will be discussed in next sub section.

components

Table 2.3 Pulse frequency (PF) vs passive

| PF     | Output capacitor | Inductor | Reactive current | Output<br>Current |

|--------|------------------|----------|------------------|-------------------|

| 10 kHz | 1.53 mF          | 17.3 μΗ  | 156A             | 204 A             |

| 20 kHz | 768 μF           | 8.67 μΗ  | 78A              | 204 A             |

| 40 kHz | 384 μF           | 4.33 μΗ  | 39A              | 204 A             |

### Output wave form vs output capacitances

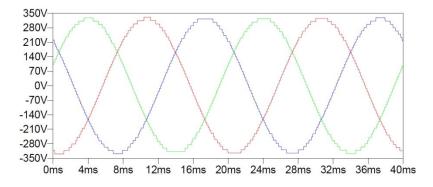

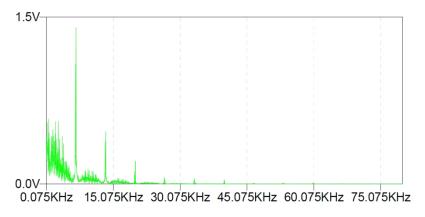

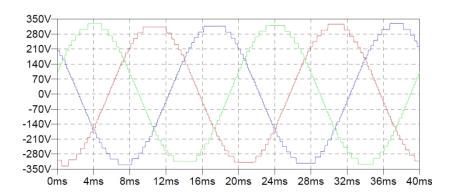

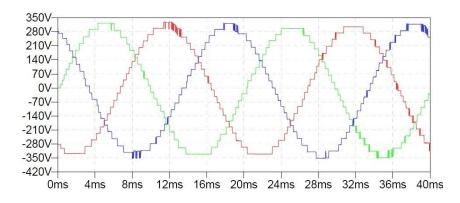

The output voltage supposes to have sinusoidal waveform with a high frequency voltage ripple as shown in Figure 2.2. The amplitude of the high frequency voltage ripple shall increase with a decreased output capacitance. This high frequency voltage ripple has harmonics with a fundamental frequency of PF/3. In this sub sections simulated output waveforms with different output capacitors value are shown. The capacitance is calculated by (2.10) with different  $\Delta V$ .  $V_{rms}$ ,  $P_{max}$  and PF is select as 230V, 100 kW and 20 kHz respectively.

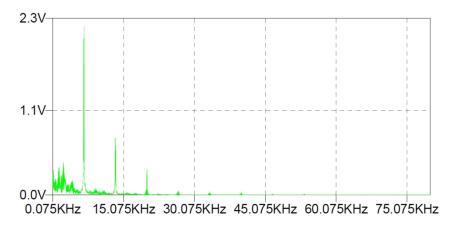

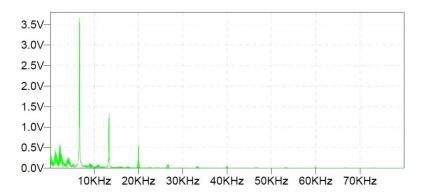

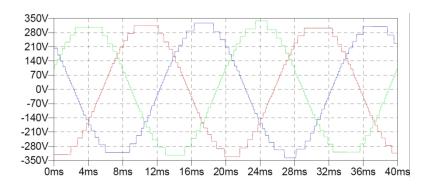

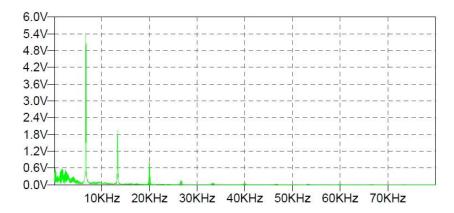

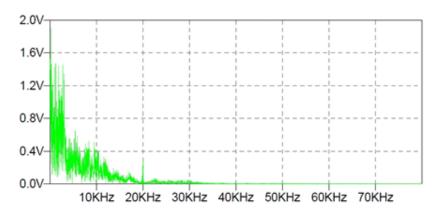

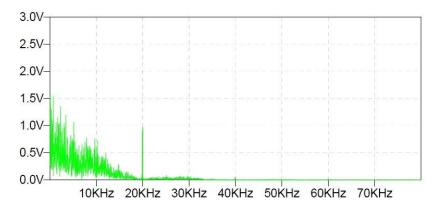

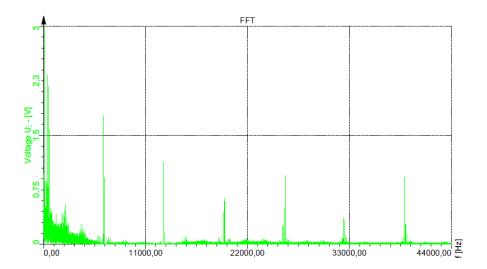

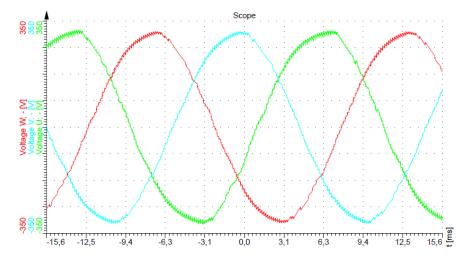

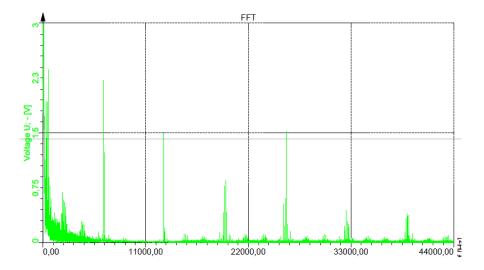

If  $\Delta V$  is selected to 20V the output capacitor will have a value of 1.53 mF. The no load output waveform looks like the output from a multilevel converter with lots of levels as shown in Figure 2.10. Figure 2.11 shows the main harmonic. The amplitude of the harmonics is much lower comparing to 230V 50 Hz fundamental frequency (not shown in Figure 2.11). There are also low frequency harmonics below 6 kHz as shown in the Figure 2.11.

Figure 2.10 No load output wave form with 1.53 mF output capacitors

Figure 2.11 No load output harmonics with 1.53 mF output capacitors

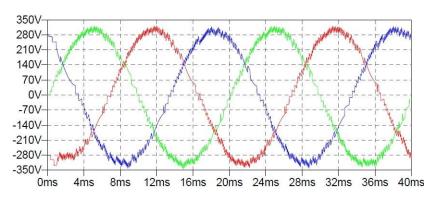

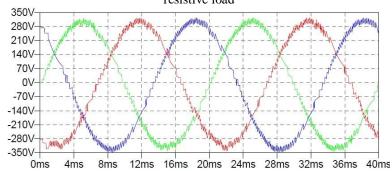

Figure 2.12 and Figure 2.13 show the output waveform with 100 kW resistive load. The output voltage is sinusoidal shaped plus small high frequency saw tooth signals. In frequency domain comparing to no load waveforms, low frequency harmonics has a decreased value, but high frequency harmonics above 6 kHz are increased. High output current requires more high frequency current pulses, which increases the high frequency harmonics.

Figure 2.12 Full load output waves with 1.53 mF output capacitors

Figure 2.13 Full load harmonics with 1.53 mF output capacitors

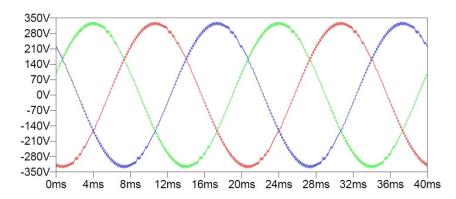

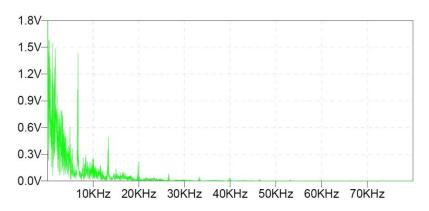

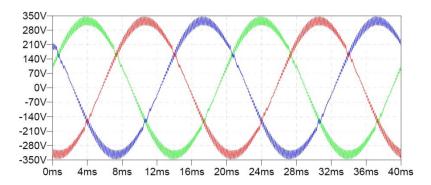

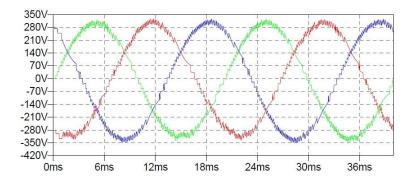

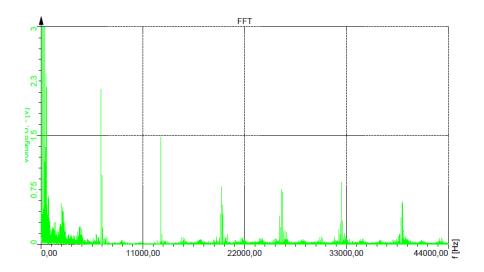

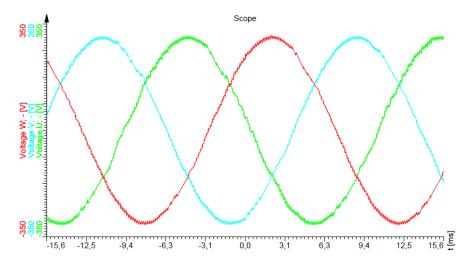

It is beneficial to use smaller output capacitors: Lower cost, smaller reactive current, lower weight and volume. Especially the capacitors in mF range are bulky components. It is essential to use optimal output capacitors. The capacitance of the output capacitor will decrease to half, to 768  $\mu F$ , if  $\Delta V$  is selected to 40V. The no load and full load waveform are shown from Figure 2.14 to 2.17. Compare Figure 2.10 to Figure 2.13, in frequency domain with reduced output capacitances. For the no load case, harmonics below 6 kHz have increased dramatically, the high frequency component above 6 kHz has similar amplitude. For the full load case, the high frequency harmonics above 6 kHz is increased dramatically.

Figure 2.14 No load output wave form with 768  $\mu F$  output capacitors

Figure 2.15 No load harmonics with 768  $\mu F$  output capacitors

Figure 2.16 Full load output wave form with 768 µF output capacitors

Figure 2.17 Full load output harmonics with 768 µF output capacitors

The output capacitance can be further decreased to 512  $\mu$ F, if  $\Delta V$  is chosen to 60V. Figure 2.18 to Figure 2.21 shows the output curves. The voltage step in Figure 2.18 is high with high output voltage. This phenomenon can be explained by Figure 2.5: at low output voltage,  $Q_{min}$  is lower than in the high output voltage cases which results in smaller output voltage steps. This phenomenon can also be found in full load cases, the saw tooth signal has smaller voltage ripple with low output voltage. In frequency domain, the no load trend is that the harmonics below 6 kHz are increased, due to that the step chair curve has higher voltage steps. For the full load conditions, higher frequency harmonic is increased because the saw tooth voltage ripple has higher value.

Figure 2.18 No load output wave form with 512  $\mu F$  output capacitors

Figure 2.19 No load harmonics with 512  $\mu F$  output capacitors

Figure 2.20 Full load output wave form with 512 µF output capacitors

Figure 2.21 Full load output harmonics with 512 μF output capacitors

## Simulated high frequency pulses

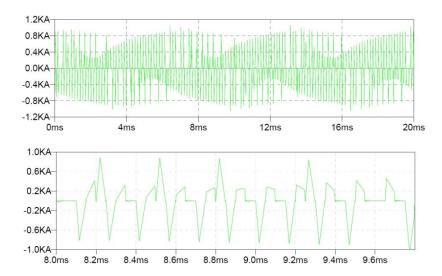

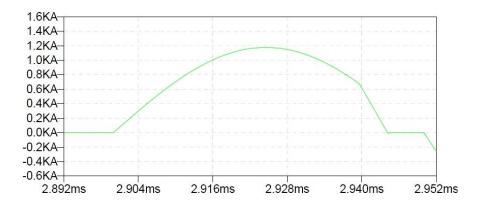

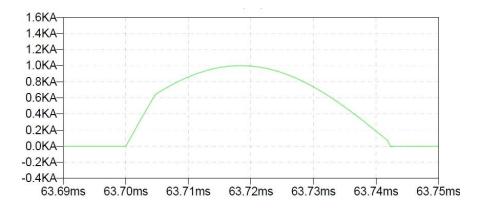

Figure 2.17 shows that the full load amplitude of the high frequency current pulses are high and it results in high rms value of the current pulses. Figure 2.22 is the simulated current of the transformer primary. The upper side figure is the current pulses in one electrical period (50 Hz); the lower side figure is the zoom in time domain to show the details of the current pulses. The amplitude of the current pulses agrees with the result from figure 2.17, the rms value of the current pulses is simulated as 535A.

Figure 2.22 Current wave form of transformer primary.

#### Losses calculation

Losses are always an important issue in converter design. In this sub section, semiconductor losses are calculated based on the commercial available components. The purpose of this losses calculation is to have a figure to show how the losses are generated and how the losses are distributed between different parts of the converter main circuit. The losses that are generated by the output capacitors, the transformer, and the cable copper are not included in this investigation. The losses calculation is carried out by a Matlab m.file. The main reason not including the losses estimation in LTspice is that it is difficult to find spice model for most IGBTs, and the system will become complex with real semiconductor models.

The turn-on losses of the transistors in the input 4-quadrant converter are neglected since they are turned on at zero current. Switching losses of the diodes in the 4-quadrant converter can also be neglected due to the zero current switch-off of the diodes. The switching losses of the transistors and diodes in the output transistor are neglected since all these components are zero current switching.

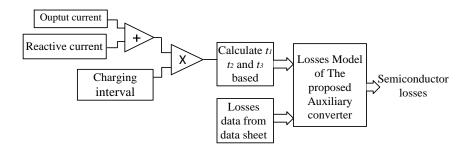

The losses included in this calculation are: Conduction losses of all the transistors and diodes and turn off losses of the transistor in the input 4-quadrant converter. Figure 2.23 shows the simplified key steps of the losses calculation for one output phase. The load current contains two parts: output current and reactive current that circulates between the output capacitors. The sum of these two current times the charging interval will be the required charged Q. Using Q the switching profiles  $(t_1,t_2,t_3)$  in the Figure of the transistor can be calculated. The next step is to calculate the losses based on the losses data and the losses model of the proposed auxiliary converter. The input parameters for calculation of the semiconductor losses are shown in Table 2.3.

Figure 2.23 Simplified losses calculation model

Table 2.3 Parameters of calculation and key components

| DC link voltage      | 750 V        |

|----------------------|--------------|

| Maximum power        | 100 kW       |

| Switching freq.      | 20 kHz       |

| Output voltage       | 230 Vrms     |

| Output capacitor     | 768µF        |

| Inductor $L_1$       | 9.9 μΗ       |

| Bidirectional switch | FS600R07A2E3 |

| H-Bridge             | FF600R12IP4  |

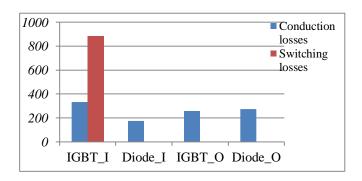

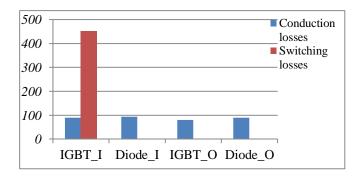

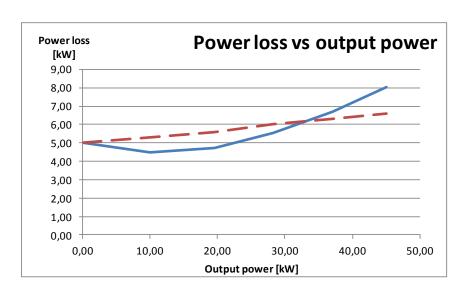

Figure 2.24a Calculated full load losses

Figure 2.24b Calculated no load losses

See Figure 2.24 for the calculated semiconductor losses. IGBT\_I and Diode\_I means IGBT and diode that belongs to the input stage. IGBT\_O and Diode\_O means IGBT and diode that belongs to the output stage. The switching losses are around 50% of the total losses, even if only the turn off losses of the transistors in the input stage is involved. One reason for high switching losses is that the transistors are always turned off when the current is high. The total semiconductor loss is 5.77 kW for 100 kW resistive loads with silicon IGBTs. The no-load losses are calculated to 2.41 kW (see Figure 2.24b).

**2.5**. Summary 35

# 2.5 Summary

In this chapter an inductive link auxiliary converter topology is introduced. The calculation of passive components values are given. Methods for generating current pulses and modulation method are investigated. The control algorithm are given and implemented in LTspice. The simulated output voltages are sinusoidal shaped with very low amount of harmonics. The calculation of the semiconductor losses is given for estimating the losses distribution with active devices.

# Chapter 3 Proposed Resonant Link Auxiliary Converter

## 3.1 Introduction

A resonant converter topology is introduced to reduce switching losses which are caused by simultaneous high voltage across and high current through the semiconductor devices, when the device changes from conducting to blocking state or vice versa. Another feature of resonant converters is the ability to control the time derivative of the voltage and/or the current. According to the results from the end of chapter 2 switch losses contribute around 50% of total semiconductor losses. Reduction of the switch losses is the main purpose to investigate the resonant version of the proposed auxiliary converter. This chapter starts with a study of the series load resonant converter, and then investigate the proposed resonant auxiliary converter thoroughly.

## 3.2 Load resonant converters

Three types of resonant converters have the feature of zero voltage or zero current switching [13]: load resonant converters, resonant switch DC/DC converters, resonant dc link and forced commutated converters. The proposed resonant DC ac converter has a similar operation principle as load resonant converter (The load is part of the resonant tank). In this sub section, the basic operation principle of the load resonant converter is investigated. In the following sections, the resonant DC/DC converter and resonant DC/AC converter are referring to as series load resonant DC/DC converter and series load resonant dc ac converter respectively.

Figure 3.1a Resonant DC/AC converter

Figure 3.1b Resonant DC/DC converter

Load resonant converter contains either one/two phase legs. The output of the phase leg is connected to a series/parallel resonant tank which contains a capacitor, an inductor and the load. Normally the load is a resistor and may contain part of the inductor and the capacitor. This type of converter is delivering only ac current to the load, and with this feature it is also called a resonant dc ac converter (See Figure 3.1a). This type of converter is used in induction heating applications [13]. If a DC output voltage is needed, a rectifier is connected at the output. The converter then becomes a resonant DC/DC converter. In some applications a transformer is connected between the rectifier and the rest of the converter for galvanic isolation.

### Control of the resonant DC/DC converter

Frequency control and phase shift control are the two common methods for controlling the load resonant converter. Frequency control: the resonant current is controlled by changing the impedance of the resonant tank. This is achieved by changing the switching frequency. The second method is phase shift control: the resonant current is controlled by changing the input voltage of the resonant tank. This is done by changing the phase shift angle between the converter phase legs.

When using varying frequency for controlling the resonant current, the frequency is mainly operating at two areas [14]: either above or below the resonant frequency of the resonant tank. The resonant frequency is calculated as

$$\omega_r = 2\pi f_r = \frac{1}{\sqrt{L_r C_r}} \tag{3.1}$$

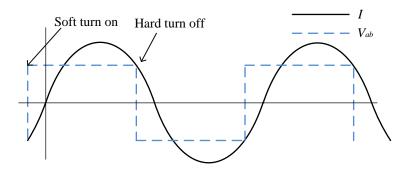

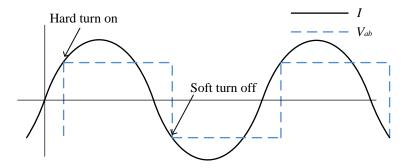

If the converter operates above the resonant frequency, the resonant tank will appear inductive due to the inductor reactance dominates. The resonant current lags the output voltage of the phase terminals. As shown in Figure 3.2 transistors are turned on at zero current and zero voltage since the current is fed through the anti-parallel diode during turn on of the transistor. While the turn off of the transistor is hard turn off with inductive load. By adding a capacitor snubber between the transistor collector and the emitter makes the turn off of the transistor a zero voltage switching in heavy load conditions [15]. On the other hand at lower load condition it introduces additional losses at turn on of the transistor [15]. By changing the switching frequency the impedance of the resonant tank varies thereby the resonant current varies, and this is the principle to control the resonant current.

If the converter operates below the resonant frequency (See Figure 3.3), the resonant tank appears as a capacitive load. The resonant current is leading the output voltage of phase legs. The transistor experiences hard turn on with capacitive load and zero current/voltage turn off. Capacitor snubber is not suitable in this case since it introduces high collector current peak during turn on of the transistor.

Figure 3.2 Current lagging the converter output voltage

Figure 3.3 Current leading the converter output voltage

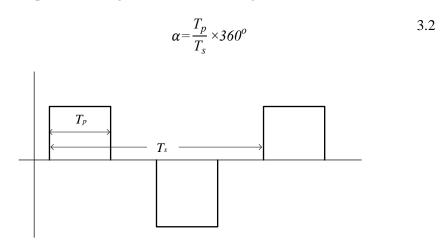

The basic principle of phase shift control is described here. The output voltage from an H-bridge  $V_{ab}$  is the voltage difference between phase output voltage  $V_a$  and  $V_b$ . It relates to the state of the switch in the H-bridge. If T1 is on T2 is off, T3 is off and T4 is on,  $V_{ab}$  will equal to  $V_{dc}$ . If T1 is on and T3 is on,  $V_{ab}$  will be equal to zero. Assume the two bridge legs are operating at the same switching frequency and the duty ratio is 50%. The waveform of  $V_{ab}$  with phase shifted angle is shown in Figure 3.4. The  $V_{ab}$  is increasing with increased phase shifted angle, by changing the phase angle,

the output voltage is changed, and thereby the resonant current is controlled. The phase shift angle is defined according to (3.2)

Figure 3.4 Input voltage of a phase shift control

## Energy analysis of resonant DC/DC converter

Assuming a resonant DC/DC converter is operating at steady state with frequency control and the switching frequency is above the resonant frequency. In steady state for the same output voltage and output current, the amplitude of the resonant current and the switching frequency shall also be in steady state. In a half switching period, the resonant current starts from zero and ends with zero ampere, the voltage over the resonant capacitor varies from  $-V_r$  to  $V_r$ . After this half electrical period, the energy which is stored in the resonant tank is not changed. And this means that the input energy of the resonant tank equals the output energy of the resonant tank, see (3.5). The input energy and the output energy are calculated with (3.3) and (3.4) respectively. If the switching frequency is increased, which causes an increased phase shift angle between  $V_{ab}$  and  $I_r$ . This leads to  $E_{in} < E_{out}$ , which leads to that the energy stored in the resonant tank decreases and the amplitude of resonant current decreases.

For phase shift control in steady state operation, the same principle applies,

when the phase shift angle varies, the input power of the resonant tank varies, thereby the energy that is stored in the resonant tank varies, and this leads to that the output power also varies.

$$E_{in} = \int_0^{t_I} (V_{dc} - V_{out}) \times I_r dt$$

(3.3)

$$E_{out} = \int_{t_I}^{t_2} (-V_{dc} - V_{out}) \times I_r dt$$

(3.4)

$$E_{in} = E_{out} \tag{3.5}$$

Figure 3.5 Simplified circuit of a resonant DC/DC converter

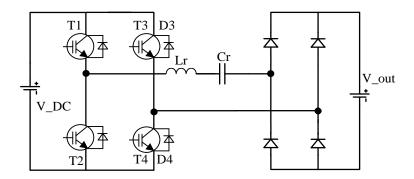

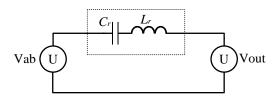

# 3.3 Proposed resonant auxiliary converter

The schematic circuit of the proposed resonant auxiliary converter is shown in Figure 3.6. Comparing to the resonant DC DC converter, the rectifier is replaced by three phase bidirectional switches and the output capacitors. The function of the proposed resonant auxiliary converter is providing an output filter free DC to AC conversion, galvanic isolation between input voltage and output AC voltage and omitting the redundant energy conversion stage to reduce components.

Similar to the proposed inductive link auxiliary converter presented in previous chapter, there are two energy conversions in the proposed resonant

auxiliary converter. The first energy conversion is from input DC voltage to high frequency AC current pulses. This is done by the resonant tank and the H-bridge. The second one, which converts the high frequency AC current pulses to three low frequency AC voltages, is done by the bidirectional switches and the output capacitors. The high frequency current pulses are selected by bidirectional switches to charge/discharge the output capacitors to form sinusoidal output voltages.

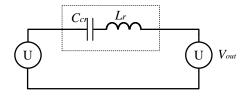

Figure 3.6 Proposed resonant auxiliary converter

Controlling the resonant current pulses is different from controlling the resonant current of the resonant DC/DC converter. See Figure 3.5, for the resonant DC/DC converter the excitation voltage over the resonant tank contains two parts: the converter output voltage and the output voltage of H-bridge. In steady state operation the converter output voltage can be considered as a constant voltage, and the input voltage is changing by phase shift control or frequency control, as stated in previous chapter.

For the proposed resonant auxiliary converter the output voltage is varying all the time and this introduce additional difficulties for controlling the energy of the resonant tanks.

## 3.4 Modulation and Control Algorithm

As stated in section 3.3, controlling the proposed resonant auxiliary converter has more difficulties than controlling the resonant DC/DC converter. The challenges are caused by the continuously changing output voltages of the converter and the connection between the resonant tank and the converter outputs which is switched between different output phases via

bidirectional switches. Between different switching period, the output voltages of the resonant tank is different from each other, in order to keep the energy stored in the resonant tank stable and to fulfill equation (3.5), the input voltage of the resonant tank have to change accordingly (the input voltage of the resonant tank is the output voltage of the H-bridge, and the output voltage of the resonant tank is the output phase voltages).

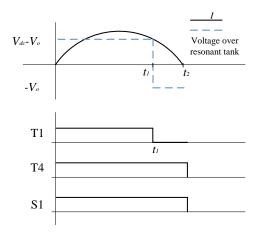

The output voltages of the H-bridge is  $+V_{dc}$ ,  $-V_{dc}$  and zero. Consider a condition which is shown in Figure 3.6. A positive current pulse is needed by phase A and the output voltage of phase A is larger than zero. First the transistor T1 and T4 shall be turned on. The current starts to increase from zero, during this time the voltage over the resonant tank is  $V_{dc}$ - $V_{out}$ , and the energy that flows into the resonant tank is given by equation (3.3). After a while, at time  $t_1$  in Figure 3.9 in order to keep the stored energy of the resonant tank stable, another voltage over the resonant tank shall be applied. Two different voltages can be applied by turning off either T1 and T4, or T1 only. These two voltages are  $-V_{dc}$ - $V_{out}$  and  $-V_{out}$  respectively. Turn off T1 and T4 cause hard turned off of two transistors while Turn off T1 only requires one hard turn off. The switching time  $t_1$  is chosen according to (3.5).

#### Series resonant circuit

In order to find the  $t_1$  to fulfill the (3.5), it is necessary to investigate the series resonant L-C-R circuit. The series L-C-R circuit is shown in Figure 3.7. The capacitor voltage for a step voltage  $V_s$  with initial current  $i_o$  and initial capacitor voltage  $V_{cr}$  is given by [13].

$$i(\omega t) = \frac{V_s - V_{cr}}{\omega l} e^{-\alpha t} \sin(\omega t) + i_o e^{-\alpha t} \frac{\omega_o}{\omega} \cos(\omega t + \Phi)$$

(3.6)

$$V_c(\omega t) = V_s - (V_s - V_{cr}) \frac{\omega_o}{\omega} e^{-\alpha t} \cos(\omega t - \Phi) + \frac{i_o}{\omega C} e^{-\alpha t} \sin(\omega t)$$

(3.7)

Where the

$$\omega^2 = \omega_o^2 (I - \xi^2) = \omega_o^2 - \alpha_o^2$$

,  $\omega_o = \frac{1}{\sqrt{LC}}$ ,  $\alpha = \frac{R}{2L}$ ,  $\xi = \frac{R}{2\omega_o L}$ ,  $\tan \Phi = \frac{\alpha}{\omega}$ .

Figure 3.7 Series L-C-R circuit

Assuming the resistor R to be small and that it can be neglected, (3.6) and (3.7) can be rewritten as:

$$i(\omega_o t) = \frac{V_s - V_{cr}}{\omega_o l} \sin(\omega_o t) + i_o \cos(\omega_o t)$$

(3.8)

$$V_c(\omega_o t) = V_s - (V_s - V_{cr})\cos(\omega t) + \frac{i_o}{\omega_o C}\sin(\omega t)$$

(3.9)

At the beginning of each half cycle the initial value of  $i_o$  is zero (3.8) and (3.9) can be rewritten as

$$i(\omega_o t) = \frac{V_s - V_{cr}}{\omega_o l} \sin(\omega_o t)$$

(3.10)

$$V_c(\omega_o t) = V_s - (V_s - V_{cr}) \cos(\omega_o t)$$

(3.11)

## Energy balance of proposed resonant auxiliary converter

The voltage over the resonant tank is the converter output voltage plus the output voltage from the H-bridge. The converter output voltage is a 50 Hz AC voltage; during the one pulse period the converter output voltage can be considered as a constant voltage since variation of the voltage in one pulse period is small comparing to output voltage amplitude. The output voltage of the H-bridge has three values:  $V_{dc}$ ,  $-V_{dc}$  and 0. The combination of those three value results in variation of the H-bridge output voltages. The voltage transition between  $V_{dc}$  and  $-V_{dc}$  results in a hard turn off of two transistors

and the voltage transition from either  $V_{dc}$  or  $-V_{dc}$  to zero results in a hard turn off of only one transistor. In order to reduce the switch losses and the stress on the switches, the transition between  $V_{dc}$  and  $-V_{dc}$  should be avoided.

To fulfill the equation (3.5),  $V_{ab}$  and  $V_{out}$  in Figure 3.8 shall have the same polarity which indicates that for example when the output voltage  $V_{out}$  is larger than zero, the voltage  $V_{ab}$  should be a combination of  $V_{dc}$  and 0. Calculation of the transition time  $t_1$  in Figure 3.9 is the key. The initial state of the resonant capacitor defines the polarity of the current pulses. For example, the resonant capacitor initial voltage has a polarity that is as shown in Figure 3.8, the current pulse polarity is from the input side to the output side, after half the electrical period the resonant capacitor voltage has the same absolute value but the polarity has been changed, the next current pulse will have a reversed polarity.

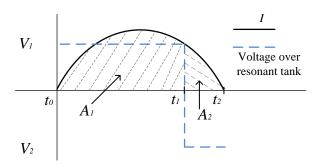

Calculation of the voltage transition time  $t_I$  is given here. Consider a general condition that is shown in Figure 3.8 and in Figure 3.9. At the initial state the polarity of the resonant capacitor voltage  $V_{cr}$  is shown in Figure 3.8. The current start to increase at  $t_0$  when  $V_I$  is applied over the resonant tank, and at  $t_I$  the voltage over the resonant tank is transferred to  $V_2$ , The input energy and the output energy of the resonant tank can be easily calculated with (3.12) and (3.13), where A1 and A2 are the area that is covered by the current pulses before and after the transition time  $t_I$ .

Figure 3.8 Simplified circuit of the proposed resonant auxiliary converter

Figure 3.9 Current pulses of half the electrical period.

$$E_{in} = V_1 \times A_1 \tag{3.12}$$

$$E_{out} = V_2 \times A_2 \tag{3.13}$$

At  $t_0$  the initial current of the resonant inductor is zero and the initial voltage of capacitor is  $V_{ci}$ . The resonant current between  $t_0$  and  $t_1$  can be given by (3.14)

$$i_t = \frac{V_1 - V_{ci}}{\omega_o l} \sin(\omega_o t) \tag{3.14}$$

The integration of  $i_t$  from  $t_\theta$  and  $t_I$  is given by (3.15) where  $\theta_1$  is given by  $\omega_o t_I$

$$A_{I} = \int_{t_{0}}^{t_{I}} \frac{V_{I} - V_{ci}}{\omega_{o} l} \sin(\omega_{o} t) dt = \frac{V_{I} - V_{ci}}{\omega_{o}^{2} l} (1 - \cos\theta_{1})$$

(3.15)

After  $t_1$  the voltage over the resonant tank is changed to  $V_2$  and the initial condition of the resonant tank at  $t_1$  is given by equation (3.16) and (3.17).

$$V_{tl} = V_l - (V_1 - V_{ci})\cos(\omega_o t_1)$$

(3.16)

$$i_{tl} = \frac{V_1 - V_{ci}}{\omega_o l} \sin(\omega_o t_1)$$

(3.17)

Substitute (3.16) and (3.17) into (3.8) gives the current during the time

interval  $t_1$  and  $t_2$  as shown in equation (3.18).

$$i_{t} = \frac{(V_{2} - V_{1}) + (V_{1} - V_{ci})\cos(\omega_{o}t_{1})}{\omega_{o}l}\sin(\omega_{o}(t - t_{1})) + \frac{V_{1} - V_{ci}}{\omega_{o}l}\sin(\omega_{o}t_{1})\cos(\omega_{o}(t - t_{1}))$$

(3.18)

The integration of  $i_t$  from  $t_1$  and  $t_2$  is given by (3.19) where  $\theta_2$  is given by  $\omega_o t_2$ .

$t_2$  is the time when the resonant current becomes zero. And the relation between  $t_2$  with a given  $t_1$  is given by (3.20)

$$A_{2=} \int_{t_{1}}^{t_{2}} i_{l} dt = \frac{(V_{2} - V_{l}) + (V_{l} - V_{ci}) \cos \theta_{1}}{\omega_{o}^{2} l} (1 - \cos(\theta_{2}) - \theta_{1}) + \frac{(V_{l} - V_{ci})}{\omega_{o}^{2} l} \sin \theta_{1} \sin(\theta_{2} - \theta_{1})$$

(3.19)

$$\tan(\theta_2 - \theta_1) = \frac{-(V_l - V_{ci})\sin\theta_1}{(V_2 - V_l) + (V_l - V_{ci})\cos\theta_1}$$

(3.20)

Substitute (3.19) (3.15) into (3.12), (3.13) and (3.5), the voltage transition time can be calculated together with (3.20). Solving such equations involves trigonometric functions is complicated!

For any given  $\theta_1$  there is a corresponding  $\theta_2$  that can be calculated by (3.20) in the interval [0, 180], and with this given  $\theta_1$  and calculated  $\theta_2$  the corresponding input energy and output energy of the resonant tank can be calculated by (3.15), (3.19), (3.12) and (3.13). If we chose all the possible  $\theta_1$  from 0 to 180 degree and calculate all the corresponding input energy and output energy of the resonant tank, there should be a pair of input energy and output energy that have the closest value to each other and fulfills (3.5). By using this method the solving of the equations with trigonometric functions is avoided. This method requires quite a lot computation resources and long computation time for the controller. A pre-calculated look-up table

is a good solution for this.

## Look-Up Table

To generate the lookup table more details of the resonant behavior shall be investigated. According to (3.12), (3.13), (3.15), and (3.20) the input parameters for finding  $\theta_1$  and  $\theta_2$  are the DC-link voltage, the output voltage of the converter and the initial voltage of the resonant capacitor.

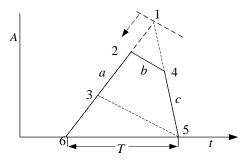

For the same resonant current direction, the direction of the energy flow depends on the polarity of the output voltages. For an output voltage with a polarity is shown in Figure 3.8, if the current pulse flows from the input Hbridge to the output, the energy is flowing from H-bridge to the output. The main operating curve is plotted in Figure 3.10. Transistor T1 and T4 and S1 is turned on at the beginning of the switching period, the voltage over the resonant tank is  $V_{dc}$  - $V_o$ . The current starts to increase from zero, after a while when t1 is reached either transistor T1 or T4 is switched off. During this time interval the voltage over the resonant tank is -Vo. The current becomes zero at the time t<sub>2</sub> and after t<sub>2</sub> the other transistors are turned off. In the case when the output voltage has a different polarity other than the case that is shown in Figure 3.8, with the same direction of the current pulse the energy is flowing from the load to the DC-link. In this case only one transistor of T1 and T4 is turned on together with S1 at the beginning, and the transistor T1 or T4 is turned off at t1 and the current becomes zero at  $t_2$ , S1 is switched off at  $t_2$ .

In the case that the initial state of resonant capacitor is changed to another polarity, other than the case that is shown in Figure 3.8, the direction of current pulse is flowing from the load to the DC-link. Instead of turning on T1 and T4 to conduct the current pulse, the transistors T2 and T3 are involved. The main operating waveform of T2 and T3 is similar to T1 and T4.

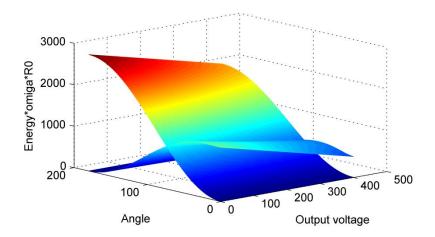

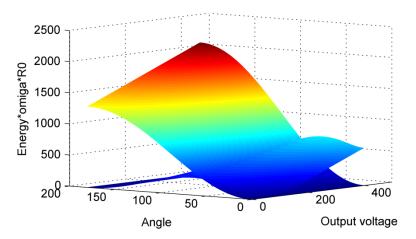

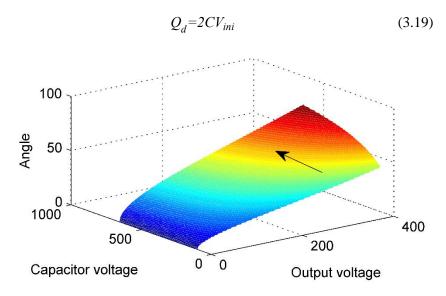

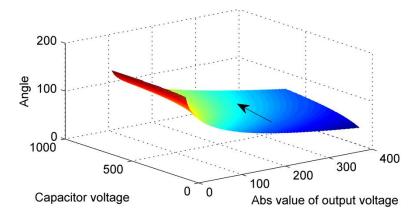

To generate the look up table, the calculation of the input/output energy and the  $\omega_o^2 l$  product vs  $\theta_1$  and output voltage is calculated and plotted according to Figure 3.12 and 3.13. Figure 3.12 is the case when the output voltage is larger than zero and Figure 3.13 is the case when the output voltage is smaller than zero. The input parameters are  $V_{dc}$ =750,  $V_c$ =600 where  $V_{dc}$  and  $V_c$  are the dc link voltage, the initial voltage of the resonant capacitor

respectively.

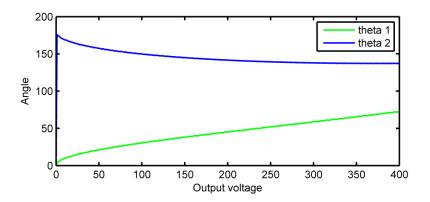

The two curved surface is corresponding to the input energy and the output energy. The crossing line between these two curved surfaces is the line along which the input energy equals the output energy. The  $\theta_1$  and  $\theta_2$  which fulfills the (3.5) can be extracted from these crossing lines. Figure 3.14 shows the extracted  $\theta_1$  and  $\theta_2$  vs output voltages.

Figure 3.10 Operating waveform

Figure 3.11 Operating waveform

Figure 3.12 Input and output energy when output voltage is larger than zero

Figure 3.13 Input and output energy when output voltage is smaller than zero

Figure 3.14a Extracted  $\theta_1$  and  $\theta_2$  ( $V_0 > 0$ )

Figure 3.14b Extracted  $\theta_1$  and  $\theta_2$  (Vo<0)

In the case when the output voltage is larger than zero (Figure 3.14a),  $\theta_1$  is low when the output voltage is close to zero, and close to half of  $\theta_2$  when the output voltage is high. Higher output voltage cause higher energy to be delivered to the output in one switching period, and thus requires more input energy to compensate the energy loss of the resonant tank. Thereby  $\theta_1$  increases with an increased output voltage. When  $\theta_1$  is larger the transistor T1/T4 needs to turn off at a higher current peak.

In the case when the output voltage is smaller than zero. The output voltage is the source of input energy of the resonant tank in a half resonant cycle. When the absolute value of the output voltage is low,  $\theta_1$  has to be large to compensate the energy loss of the resonant tank. And  $\theta_1$  decreases to almost

half of  $\theta_2$  when the abs value of the output voltage is 400 V. In this case when  $\theta_1$  is close to  $\theta_2$  either transistor T1/T4 needs to turn off at higher current.

## Stability investigation

The method that has been discussed in this section for finding  $\theta_1$  is based on the assumption that the amplitude of the voltage over the resonant capacitor is not changing between different electrical cycles. In reality the amplitude of the voltage over the resonant capacitor may vary, and it is important that, the control algorithm itself can push the amplitude of the resonant voltage back to the desired value when there are variations in the amplitude of the resonant capacitor voltage. In other words the control algorithm should be stable regarding to the controlling of the resonant energy inside the resonant tank. For example the initial value of the amplitude of the resonant voltage is zero at the initial state, the control algorithm shall have the ability that to increase the amplitude of the resonant voltage to the desired value after several pulse period. See Figure 3.15 for  $\theta_1$  vs output voltage and the amplitude of the resonant capacitor voltage. For the same output voltage, as shown in Figure 3.15, with increased capacitor voltage, the angle  $\theta_1$  is also increased. In other words, a higher resonant capacitor voltage requires higher input voltage to fulfill (3.5).

For each current pulse, the charge delivery ability can be calculated with (3.19). With increased resonant voltage, the charge delivery ability is also increased. This requires more energy in order to deliver more charge. If the charge is delivered from input DC-link to the output side which corresponds to Figure 3.15a,  $\theta_1$  shall be larger than before to deliver more energy to the output side. If the charge is delivered from output to the DC-link,  $\theta_1$  shall also be larger to deliver more energy back to the DC-link side. To fulfil (3.5)  $\theta_1$  has a positive coefficient with the resonant voltage.

This is a very nice feature: for example at the initial state of the converter, the amplitude of the resonant voltage is zero, if the look-up table is made based on the assumption that the resonant voltage is 600 V, for the first several periods, the  $\theta_1$ does not fulfill (3.5) and  $E_{in} > E_{out}$ , and this situation will continue until the desired resonant capacitor voltage is build up to the desired value. It is also helpful to reduce the requirement for monitoring the resonant voltage of the resonant capacitor. The control method itself, as we

have mentioned, can ensure that the resonant voltage comes back to the desired value. In other words, the accuracy of the voltage sensor of the resonant capacitor is not important, only the polarity of the resonant voltage is needed.

Figure 3.15a  $\theta_1$  vs output voltage and resonant voltage

Figure 3.15b  $\theta_1$  vs output voltage and resonant voltage

Based on the discussion in this section, the input data for generating a lookup table are, the DC-link voltage, the amplitude of the resonant capacitor voltage and the output voltage range. The outputs are 1-D

s of  $\theta_1$  and  $\theta_2$  vs output voltages. It does not need the details of the parameters like the capacitance of resonant capacitor and resonant inductance which gives a large freedom for setting the parameter of resonant components.

## Parameters of passive components

The selection of output capacitor is similar to the proposed hard switched auxiliary converter. The value of output capacitor can be calculated by using (2.10)

The capacitance of resonant capacitor is related to the charging carry ability according to (3.19). Substituting (2.9a) and (2.9a) into (3.19) gives the capacitance of resonant capacitor

$$C_{ron} = \frac{P_{max}}{\sqrt{2}V_{rms}FV_{ini}} \tag{3.20}$$

Here  $P_{max}$ ,  $V_{rms}$ ,  $V_{ini}$  F are maximum output power, rms value of output voltage, the amplitude of resonant capacitor voltage, and the pulse frequency respectively.

The value of resonant inductor can be calculated by

$$\omega_0^2 = \frac{1}{C_{ron}L_{ron}} \tag{3.21}$$

One current pulse period corresponding to half resonant period, then (3.21) can be rewritten as

$$L_{ron} = \frac{1}{C_{ron} F^2 \pi^2} \tag{3.22}$$

Here F is the current pulse frequency.

#### Control algorithm and discussions

The controlling method from the proposed inductive link auxiliary converter could be adapted for controlling the proposed resonant auxiliary converter. The same carrier wave, same modulation method, and fast computer control can be inherited from the proposed inductive link auxiliary converter.

Different from the proposed inductive link auxiliary converter, the flexibility of the polarity of current pulses are limited due to the property of the resonant circuit. There is always a negative current pulse followed by a positive current pulse. The polarity of current pulses is defined by the initial polarity of the resonant capacitor voltage. An additional voltage sensor or polarity monitor is needed for monitoring the polarity of resonant capacitor voltage to decide the polarity of the current pulses. This feature that the two adjacent current pulses must have opposite polarity, requires symmetrical load on the output side.

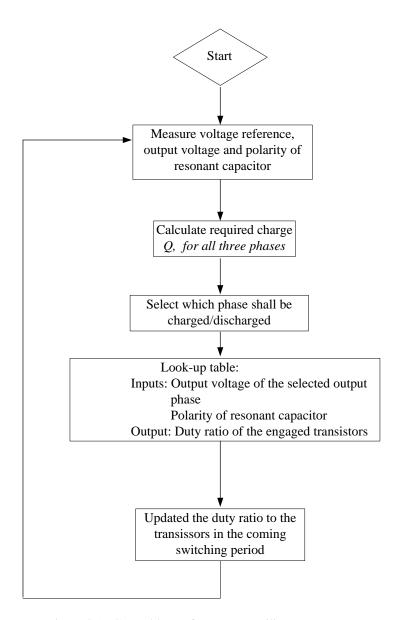

The control flow chart is shown in Figure 3.16. It starts by measuring the current state of the converter: voltage references, output voltages and polarity of the resonant capacitor voltage. Based on these measured data, the polarity of next current pulse and which output phases that should receive the current pulse can be decided.

There are three output phases, but only one output phase can be charged/discharged by the current pulse at a time. Each output phase voltage is compared to its reference voltage. The output phases that require a current pulse that has the same polarity as the next current pulse will be the candidates. If there is more than one candidate, the one that has the largest voltage error has the highest priority. To avoid over charging and to reduce losses, if all voltage errors are smaller than the predefined voltage band, none of these three output phases will be charged.

The output voltage of the selected outputs and the polarity of the resonant capacitor voltage are sent to the lookup-table to calculate the duty ratios of the transistors. The calculated duty ratios of the transistors are applied to the transistor at the beginning of the next switching period.

Figure 3.16 Control loop of resonant auxiliary converter

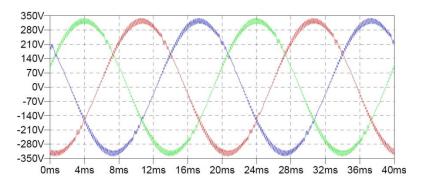

# 3.5 Simulation

Simulations are done to verify the energy balance theory of the resonant auxiliary converter and to develop the control algorithm for converter prototypes. All the simulations are done in LTspice. Figure 3.17 shows the simplified simulation model.

Figure 3.17 Simplified simulation model

The switches T1 to T4 and S1 to S3 are ideal switches. The diodes D1 to D4 are ideal diodes. Note that the load is not included in this circuit, it is formed by three sinusoidal current sources that are connect to nod A, B and C. The amplitude and phase are adjustable to simulate different load conditions.

The output capacitor in this simulation model is also an ideal component. The value is defined by (2.9) which is developed in section 2.3. The

parameter of the transformer that is used in the simulation is from an HF transformer from an auxiliary converter. The resonant inductance is formed by the leakage inductance of the transformer and an ideal inductor L1. The resonant capacitor is an ideal capacitor with the value that is calculated by (3.20)

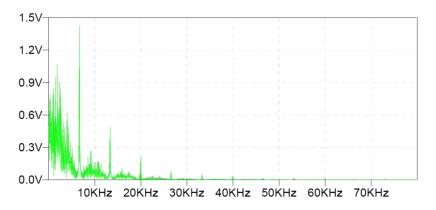

Pulse frequency is set to 20 kHz. One current pulse occupy one pulse period which means the resonant frequency equals to 10 kHz. The output capacitor is selected to 768  $\mu$ F.

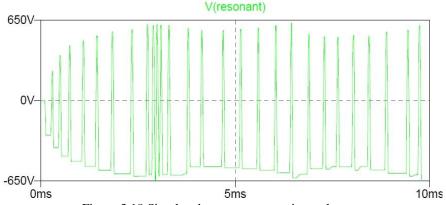

## Simulated resonant voltage

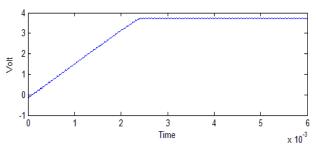

The voltage will be built up to the desired value after several half resonant periods due to the feature of the control algorithm we have discussed in section 3.4. The initial resonant voltage is zero, and in the first several pulse periods before the resonance capacitor voltage reaches its desired value, the input energy of the resonant circuit is higher than the output energy of the resonant circuit. The excess energy is stored in the resonant circuit and the voltage of the resonance capacitor is increased. When this voltage reaches its desired value the input energy is equal to the output energy of the resonant circuit, and the amplitude of the resonance capacitor voltage is stable. Figure 3.18 shows the simulated resonance capacitor voltage.

Figure 3.18 Simulated resonance capacitor voltage

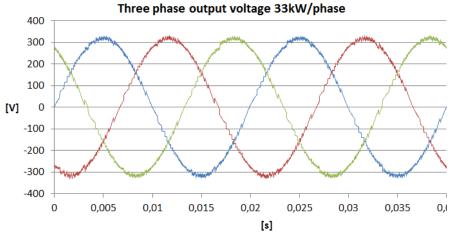

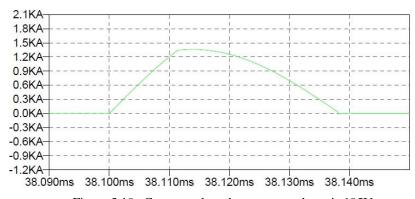

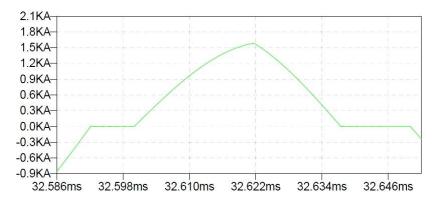

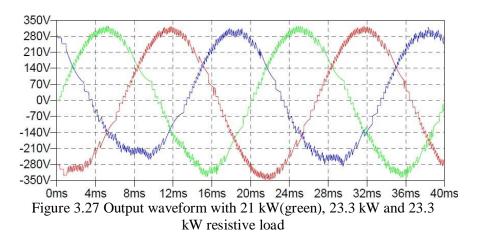

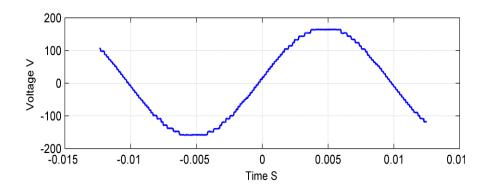

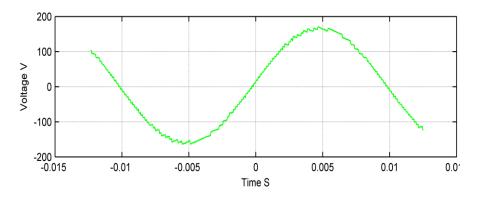

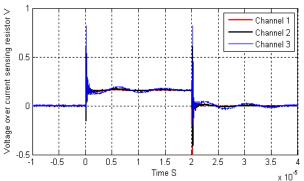

## **Simulated Current Pulse**