# Thermal Modelling of Power Modules in a Hybrid Vehicle Application

**Jonas Ottosson**

Doctoral Thesis in Electrical Engineering

Department of Measurement Technology and Industrial Electrical

Engineering

2013

Department of Measurement Technology and Industrial Electrical Engineering Faculty of Engineering, LTH Lund University

Box 118

SE-221 00 LUND

SWEDEN

http://www.iea.lth.se

ISBN: 978-91-88934-61-1

CODEN: LUTEDX/(TEIE-1069)1-135/(2013)

© Jonas Ottosson, 2013 Printed in Sweden by Tryckeriet i E-huset, Lund University Lund 2013

## **Abstract**

Hybrid electric and full electric vehicles have attracted growing attention during the last decade. This is a consequence of several factors, such as growing environmental concerns, increasing oil prices and a strive for oil independency. Hybrid vehicles have proven to have significant potential to improve fuel economy and at the same time enhance the performance of the vehicle. For the hybrid cars to really penetrate the passenger car market, it is of vital importance that the cost of hybridization can be kept as low as possible and that the increased cost will be paid back within a reasonable time horizon. In addition to this, high reliability of the additional electrical drive system (EDS) needs to be ensured.

The main parts of the electrical drive system (EDS) are the three-phase inverter and the electric traction machine (ETM). The three-phase inverter, or commonly just referred to as the power electronics (PE), is often packaged into some kind of standalone housing. This is a simple and rather straight forward way of packaging, however it is not the preferred choice in a passenger car, where the number of places and the space to put the PEassembly is often limited. Except for the high packaging volume, other drawbacks of using a standalone housing for the PE is that it requires expensive shielded high-voltage connectors and cables. An alternative solution is to integrate the power electronic inverter and the electric machine into one unit, sharing the same cooling system. This will reduce the packaging volume and at the same time omit the need for the expensive connectors and cables. The integration has other benefits such as, modularity and no separate housing for the inverter is required. All of the above mentioned benefits of the system integration lead to reduced costs of the system and in the long run a reduced price of the vehicle. However, integrating the PE and ETM into one unit makes the thermal design more difficult. This thesis focuses on determining the required cooling capacity of the cooling system, which is an important task, both from a reliability and cost perspective. Long lifetime or high reliability is important for customer acceptance.

Performing simulations of power inverter systems, where both the

electrical and thermal response is incorporated, often referred to as electrothermal simulations, is a difficult task due to the different time scales of the two disciplines. If every switching instant is to be simulated, simulation times in the range of microseconds have to be used. Simulating inverter systems in a hybrid vehicle application, where driving cycles lasting for thousands of seconds normally is used, requires unreasonable simulation times. The thesis presents a method for solving this problem.

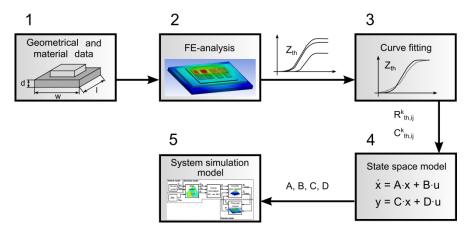

Several electro-thermal simulations are carried out in order to determine the cooling requirements and its effect on module reliability of the inverter. The foundation for these simulations is a simulation model of the electrical drive system, where the main focus is on the thermal model of the inverter itself. Finite element analysis (FEA) can provide highly accurate calculations at the expense of computational effort and simulation time. There is no easy way to incorporate FEA calculations into an electrical time domain simulation. The thesis presents a thermal model development procedure to derive simplified thermal models based on thermal impedances.

Thermal models for a range of power modules, including both Si and SiC based modules, are developed. Different types of assemblies with single-sided cooling are studied in this thesis. In addition to the different single-sided cooled module assemblies, one assembly with double-sided cooling is studied. The thesis shows that the type of layout and assembly greatly affects the thermal behaviour, and as a consequence the lifetime, of the power module.

In addition to different module assemblies and cooling options, the system is evaluated for different driving cycles and cooling medium temperatures, together with a comparison of using a fixed and variable switching frequency. The thesis shows that using a variable switching frequency has a significant impact on the cooling requirements.

## **Acknowledgements**

First and foremost, I want to thank my supervisor Professor Mats Alaküla for the guidance during the work with this thesis.

I would also like to thank my former colleagues at BorgWarner (Haldex Traction) in Landskrona, special thanks to Daniel Hervén, Daniel Norlén, Gustaf Lagunoff and Pierre Pettersson who all have inspired me in different ways. The cooperation with BorgWarner has been very valuable to me.

I would like to thank the Department of Industrial Electrical Engineering and Automation at Lund University for all the interesting discussions. Special thanks to Getachew Darge and Bengt Simonsson for helping me out in the lab. I am also grateful to Dr. Per Karlsson for answering all my power electronics related questions. I would also like to thank my fellow PhD-students Jonas Johansson, Luyu Wang and Francisco Marquez, for good advice and collaboration. I am particularly indebted to Dan Hagstedt, my colleague and dear friend, for travelling with me on conferences and introducing me to the Hagstedts Fridays.

Many thanks to Fredrik Olne, one of my oldest and best friends, for having me as a lodger during my numerous trips to Skåne.

This work has been financed by BorgWarner and the Swedish Energy Agency, which is gratefully acknowledged.

Lastly, I would like to thank my family for all their love and support. A special thanks to my mum Carina for always being there for me, supporting me in all my pursuits. Lisen, one thing is true, this thesis would never have been finished without your support. Thanks for your patience, love and encouragement during these years. Eva-Li, you are my everything.

Göteborg, October 2013 Jonas Ottosson

## **Preface**

When I write this, it is almost ten years ago since I started as a PhD student at the Department of Industrial Electrical Engineering and Automation, Lund University, in 2004. The project that I was working in back then was focused on energy management and control of electrical drives for hybrid electrical vehicles. The results of that project were published in a Licentiate thesis in 2007. In the same year I got an employment at Volvo AB and worked there for nearly two and a half year. In 2009 I got the opportunity to continue my PhD-studies. However, this was within a different project, focusing on the development of an electrically driven rear-axle for a hybrid car, where I came to focus on thermal modelling of power modules.

# **Contents**

| CHAPTI | ER 1 INTRODUCTION                           | 1     |

|--------|---------------------------------------------|-------|

| 1.1    | BACKGROUND                                  | 1     |

| 1.2    | MOTIVATION                                  |       |

| 1.3    | OBJECTIVES                                  | 2     |

| 1.4    | PREVIOUS WORK AND LITERATURE REVIEW         |       |

| 1.5    | MAIN CONTRIBUTIONS                          | 5     |

| 1.6    | OUTLINE OF THE THESIS                       | 6     |

| 1.7    | PUBLICATIONS                                | 7     |

| CHAPTI | ER 2 POWER DEVICES                          | 9     |

| 2.1    | POWER DEVICE PACKAGING AND MATERIALS        | 9     |

| 2.2    | POWER MODULE RELIABILITY                    |       |

| 2.3    | HEAT TRANSFER                               | 27    |

| 2.4    | POWER ELECTRONIC COOLING METHODS            |       |

| СНАРТІ | ER 3 THERMAL MODELLING OF POWER MODULI      | ES.31 |

| 3.1    | THE HEAT CONDUCTION EQUATION                | 31    |

| 3.2    | SOLVING THE HEAT CONDUCTION                 | 32    |

| 3.3    | TRANSIENT THERMAL IMPEDANCES                |       |

| 3.4    | MATHEMATICAL DERIVATION OF FOSTER BASED THE | RMAL  |

|        | Models                                      | 39    |

| СНАРТІ | ER 4 SYSTEM MODELLING                       | 45    |

| 4.1    | SYSTEM MODEL                                | 45    |

| 4.2    | Power Modules                               | 46    |

| 4.3    | VEHICLE MODEL                               | 48    |

| 4.4    | ELECTRICAL MACHINE MODEL                    | 49    |

| 4.5    | POWER ELECTRONIC LOSS MODELLING             | 52    |

| 4.6    | THERMAL MODELS OF POWER MODULES             | 56    |

| CHAPTI | ER 5 SYSTEM SIMULATIONS                     | 63    |

| 5.1    | SYSTEM SIMULATIONS AND EVALUATION CRITERIA  | 63    |

| 5.2    | DRIVING CYCLES                              |       |

| 5 3    | CONVECTION COFFEIGENTS                      |       |

| 5.4    | FIXED AND VARIABLE SWITCHING FREQUENCY | 64      |

|--------|----------------------------------------|---------|

| 5.5    | POWER MODULE INTEGRATION               | 65      |

| 5.6    | COOLING MEDIUM TEMPERATURE             | 70      |

| 5.7    | LIMITED REGENERATIVE TORQUE            | 71      |

| CHAPTI | ER 6 RESULTS                           | 73      |

| 6.1    | MAXIMUM JUNCTION TEMPERATURE           | 73      |

| 6.2    | RELIABILITY RESULTS                    | 90      |

| CHAPTI | ER 7 CONCLUDING REMARKS AND FUTURE WO  | ORK. 99 |

| 7.1    | SUMMARY OF FINDINGS                    | 99      |

| 7.2    | FUTURE WORK                            | 103     |

| REFERI | ENCES                                  | 105     |

| APPENI | DIX A                                  | 111     |

| APPENI | OIX B                                  | 117     |

| APPENI | DIX C                                  | 119     |

| APPENI | DIX D                                  | 121     |

# Chapter 1

## Introduction

## 1.1 Background

This thesis is a part of a project originally called eBAX (*Swedish:* elektrisk bakaxel), which overall aim was to develop an electrically driven rear axle for a passenger car. The name has changed over the years, and the most recent name is eTVD (Electrical Torque Vectoring Device. BorgWarner, former named Haldex Traction AB, had developed a first prototype. During that work, it was found out that more than 80% of the total system cost originates from the power electronics and the electric machine. Hence, the project was focused on three major parts, namely the power electronics, the electric machine and the overall optimization of the system.

## 1.2 Motivation

Hybrid electric and full electric vehicles attract growing attention. This is a consequence of several factors, such as growing environmental concerns, increasing oil prices and a strive for oil independency. According to some, we are rapidly approaching the top of the oil era, whereas some state that we have already passed peak oil. If this is true, the diminishing availability of crude oil will escalate the already high fossil fuel prices. Many countries, there among Sweden, have declared national actions plans to reduce the oil consumption significantly. The background of the desired reduction in oil use, differ between countries, but the two main concerns are the environmental effects and the strive for independency of oil import. Whatever the concern, economical, independency or environmental, how does hybrid vehicles fit in this context?

Hybrid vehicles have proven to have significant potential to improve fuel

economy without reducing the performance of the vehicle. Keeping or even enhancing, which often is the case, the drivability is an important issue in order to reach customer acceptance. Except for gains in the fuel economy, hybrid vehicles also demonstrate potential for reducing exhaust emissions. Most hybrid vehicles on the market today, are hybrid electric vehicles (HEV) with an internal combustion engine (ICE) and at least one electrical machine. Toyota was the first major automaker to introduce a commercial vehicle, the Toyota Prius. The commercialization in the recent years has mainly been possible due to advances in the battery and power electronics technologies. The HEVs mainly benefit from the following: down-sizing or "right"-sizing of the engine, still fulfilling the power demanded from the driver, recovering energy during deceleration by operating the electrical machine as a generator, eliminating the fuel consumption originating from engine idling by shutting the ICE off and operating the ICE more efficiently, since an extra degree of freedom is available to satisfy the power demand.

With this background given, it is clear why almost all car manufactures are developing HEVs today. However, for the hybrid cars to really penetrate the passenger car market, it is of vital importance that the cost of hybridization can be kept as low as possible and that the increased cost will be paid back within a reasonable time horizon.

## 1.3 Objectives

As was stated in the motivation for this thesis, there is a need from the car manufacturers to simplify and reduce the cost of hybrid drivelines, in order to make hybrid cars more attractive on the market. The hybrid vehicle, studied in this thesis, is assumed to be a plug-in hybrid electrical vehicle (PHEV) with an electrically driven rear-axle. The main parts of the electrical drive system (EDS) are the three-phase inverter and the electric traction machine (ETM). The three-phase inverter, or commonly just referred to as the power electronics (PE), is often packaged into some kind of standalone housing. This is a simple and rather straight forward way of packaging, however it is not the preferred choice in a passenger car, where the number of places and the space to put the PE-assembly is often limited. Except for the high packaging volume, other drawbacks of using a standalone housing for the PE is that requires expensive shielded high-voltage connectors and cables. An alternative solution is to integrate the

power electronic inverter and the electric machine into one unit, sharing the same cooling system. This will reduce the packaging volume and at the same time omit the need for the expensive connectors and cables. The integration has other benefits such as, modularity and no separate housing for the inverter is required. All of the above mentioned benefits of the system integration lead to reduced costs of the system and in the long run a reduced price of the vehicle. However, integrating the PE and EM into one unit makes the thermal design more difficult. An inverter able to deliver a peak power output of 90kW, with an average efficiency of 97%, produces approximately 2.7 kW of losses, which needs to be handled by the cooling system. Determining the required cooling capacity of the cooling system is hence an important task, both from a reliability and cost perspective. Long lifetime or high reliability is important for customer acceptance. A detailed analysis of the cooling requirements for the PE, prevents the cooling system and the power modules from being overrated. Hence, based on what has been discussed above the main objectives of this thesis are:

- ➤ Investigate if it is possible to integrate the power electronics into the rear drive unit, by deriving guidelines for the cooling system in terms of required convection coefficients and maximum cooling liquid temperatures.

- ➤ Determine the actual cooling requirements for the power electronics, looking at different driving cycles and module assemblies.

- > Develop thermal models that can be used in system simulations.

- Study how the requirements are changed if high temperature devices like SiC BJT:s are used.

- > Study how the reliability is affected by the cooling requirements.

## 1.4 Previous Work and Literature Review

This section is devoted to a literature review of previous work within the area of thermal modelling of power modules. The literature is divided into three different categories. Some of the papers fit in more than one category, however the actual categorization is based on what the author finds most interesting about the specific paper.

## **Thermal Modelling of Power Modules**

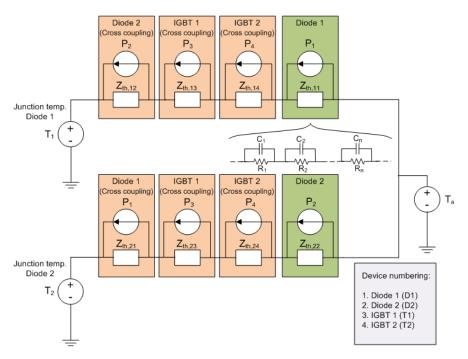

Power modules used in hybrid vehicle applications have to be able to

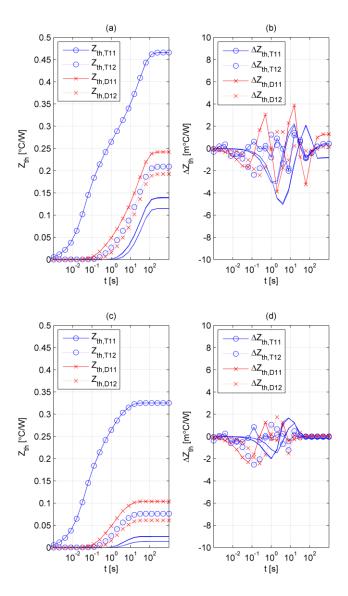

handle high currents. This is solved by parallel connection of multiple IGBT and diode chips within the same power module. This complicates the thermal modelling since thermal coupling within the module has to be considered [40] [54] [55] . There are many ways of building a thermal model of a power module. The finite element method can provide highly accurate calculations at the expense of computational effort and simulation time [53]. There is no easy way to incorporate FEM calculations into an electrical time domain simulation. Simplified thermal models are therefore often used and he most frequently used models are based on thermal networks. There are two different main types of thermal networks, the Cauer and the Foster network. The former is a simplified physical model describing the thermal behaviour of the power module, whereas the latter is a behavioural model usually derived from some kind of curve fitting procedure. The Cauer model can describe three dimensional heat flow [33], however it requires a rather fine discretization of the power module in order to capture the thermal coupling between its power devices. In order to derive a Foster model, results from either FEA simulations or measurements needs to be available. The reason is that it is a behavioural model and therefore needs to be based on known behaviours. Normally some kind of curve fitting procedure is used to extract the parameters of the model. Several Foster models can be arranged into a thermal impedance matrix describing the thermal coupling between the devices within the power module [6][35][38][40]. Thermal impedance matrices are used extensively trough out this thesis, due to its ease of extraction, implementation and model accuracy. Another type of thermal model described in [29]-[32] is based on solving the heat conduction equation with a Fourier series solution method. The method is according to [32] faster than the FDM with an acceptable level of accuracy and can easily be programmed in the Matlab/Simulink environment.

## **Electro-thermal System Simulations**

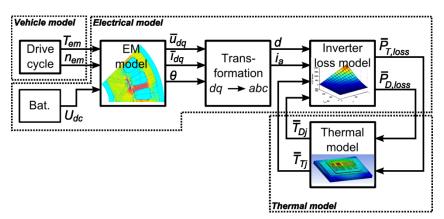

Performing simulations of power inverter systems, where both the electrical and thermal response is incorporated, is a difficult task due to the different time scales of the two disciplines. If every switching instant is to be simulated, simulation times in the range of microseconds have to be used. The thermal time scale is higher and normally in the millisecond range, depending on the size of switching devices. Simulating inverter systems in a hybrid vehicle application, where driving cycles lasting for thousands of seconds normally is used, would require unreasonable

simulation times. In order to speed up the simulations, decrease the simulation time and reduce the required memory space, semiconductor power losses are pre-computed and stored in look-up tables [42]. In [42] the power losses are computed from datasheets and a rather simple model of the EM is used. The authors in [16] and [43] [44] uses compact device models to generate the power loss look-up tables. The combination of using look-up tables for the power losses and simplified thermal models make it possible to evaluate many different system set-ups without simulation times becoming excessive. In [6] different system set-ups in terms of battery voltage, ambient temperatures and cooling options (convection coefficients) are studied.

## **Reliability of Power Modules**

The method used in this thesis to obtain a reliability estimation of the power module lifetime consists of three different steps. The first step is to carry out electro-thermal simulations in order to obtain a thermal evolution of the chip temperatures. The second step is to decompose the thermal evolution into frequencies of different combinations of temperature swing and the associated mean temperature at which the temperature swing occurs. This is done by applying a cycle counting algorithm to the junction temperature evolution. The most commonly used algorithm is the rainflow algorithm [22]-[23], often used within the area of material fatigue analysis, however other algorithms can also be used [21] [47]. As the extraction of the thermal cycling is obtained, the result is used together with some kind of reliability model. The LESIT model is a reliability model that was presented almost fifteen years ago [15]. However, it is still used as starting point of reliability estimation and often used as comparison for new improved packaging technologies [16] [17] [18]. A more recent reliability estimation model is the CIPS 2008 model, which was presented in [19]. The model is derived from extensive testing of different power modules. This model has more parameters than the LESIT model and these additional parameters are related to the power module type and layout. In [20] a lifetime model based on plastic strain is derived and further developed in [21], including creep behaviour of solder layers.

## 1.5 Main contributions

The results and contributions of this thesis are presented in Chapter 6 and discussed in Chapter 7. The main contributions of the thesis can

## summarized as follows:

- ➤ The effectiveness of using thermal models based on thermal impedances is proven.

- ➤ The importance of taking thermal coupling between the devices within a power module into account is pointed out and exemplified.

- ➤ Different module assemblies are compared in terms of cooling capability.

- > Single- and double-sided cooling are compared both on a module and complete system level.

- ➤ The cooling requirements for 300 and 400A modules are determined for a wide range of commonly used driving cycles.

- ➤ It is shown that the cooling requirements can be significantly reduced by using a variable switching frequency.

- ➤ Using SiC based power modules reduces the requirements on the cooling significantly.

- An analysis of what impact a hill-hold feature has on the cooling requirements is studied.

- A reliability analysis on system level is presented.

#### 1.6 Outline of the Thesis

This chapter is devoted to a brief outline of the thesis and a short introduction to each chapter is given. The thesis is focusing on thermal modelling of power modules and an introduction to packaging of power devices, with focus on power modules, is given in Chapter 2. How to model power module reliability and a short introduction to the discipline of Heat Transfer is also included in Chapter 2.

There are several ways of modelling a power module thermally, and a brief description of the most common ways of solving the heat conduction equation is given in Chapter 3. The main focus is however on the concept

1.7. Publications 7

of thermal impedances and a mathematical derivation of thermal impedance based thermal model is presented.

The thermal simulations presented in this thesis are based on a simulation model of a hybrid system for a passenger car. Each of the components of the full system model is described in detail in Chapter 4.

The system simulations and the criteria for evaluation of the results are described in Chapter 5. Full system simulations are carried out for a range of different conditions, such as different driving cycles, cooling requirements, module assemblies, cooling medium temperatures and switching frequency strategies, in order to obtain a comprehensive view of the system.

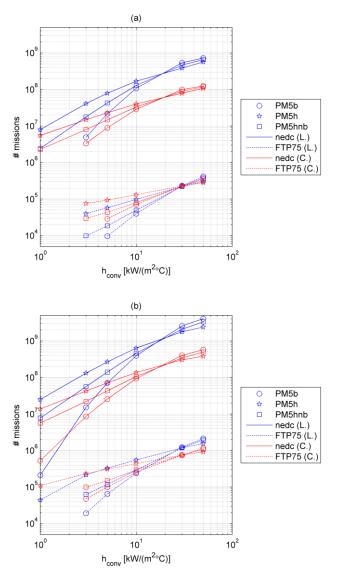

The results of the system simulations are in Chapter 6. The results are divided into two separate sections, where the first one is devoted to determining the actual cooling requirements of different power modules and the second one presents a reliability analysis of the modules.

The thesis ends with some concluding remarks and suggestions for future research in Chapter 7.

#### 1.7 Publications

Parts of the work presented in this thesis have been presented in the following publications:

- J. Ottosson, M. Alaküla, D. Hagstedt, "Electro-thermal Simulations of a Power Electronic Inverter for a Hybrid Car". *International Electrical Machines and Drives Conference (IEMDC2011)*, Niagara Falls, Ontario, Canada, May 15-18, 2011.

- J. Ottosson, P. Karlsson, "Assessment of power electronic inverter cooling requirements for a rear-axle drive". *14th European Conference on Power Electronics and Applications (EPE2011)*, Birmingham, United Kingdom, Aug. 30 Sept. 1, 2011.

- J. Ottosson, L. Wang, "Comparison of cooling requirements for Si and SiC based inverters in a hybrid vehicle application". *Power Electronics South America 2012 (PESA2012)*, São Paulo, Brazil, Sept. 11 Sept. 13, 2012.

# Chapter 2

## **Power devices**

## 2.1 Power Device Packaging and Materials

## **Package Types**

There are many different package types for power switches. The basic features of the package depend on the actual definition of what a power device package is. One possibility is to define the package as everything around the actual die. Two obvious basic features are then to support and protect the rather fragile die and serve as a supporting structure for the electrical connections. However, a good power device package should also provide good thermal performance in order to keep junction temperatures as low as possible. An easy and cost effective production is also important. More specific features are to ensure a long lifetime of the device and to minimize undesirable electrical properties, such as parasitic resistance, capacity and inductance [1].

The most demanding challenges for power device packages, from a reliability perspective, are to withstand the induced stress in interconnection of different materials due to thermal cycling. Every material within the device has a coefficient of thermal expansion (CTE), which is a measure of the degree of expansion of the material for a change in temperature. As a device is heated up, either externally by the surroundings or internally by its own losses, the different materials will expand differently causing bending within the structure. The stress induced by the difference in CTE will over time destroy the device.

## **Discrete Packages**

There are mainly three different package types used for power switches

and the type is tightly coupled to the power level of the device. In low and high power applications discrete components are normally used. However, their packaging assemblies are totally different, which can be seen in Figure 2.1.

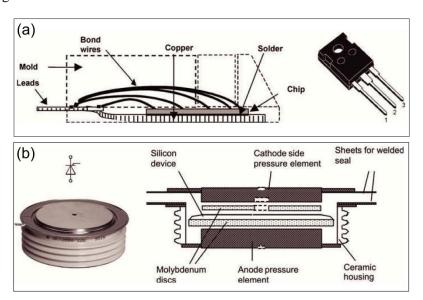

Figure 2.1 Package assembly for a TO package (a) and a capsule (b) [1].

The most common type of package for the low power switches is the TO-package. This type of package basically consists of a copper baseplate on which the silicon chip is soldered, see Figure 2.1(a). Bond wires connect the silicon chip to the lead frames. A mold is added to support the bond wires and protect the silicon chip from the surrounding environment. Other packaging designs have evolved from the TO-package, where development in order to increase reliability and to minimize electrical parasitics has been done.

When it comes to really high power applications, discrete components are also used and the dominating packaging type is the capsule. An example of the capsule packaging type and a schematic overview of the internal construction can be seen in Figure 2.1. The reasons for using capsules in the high power range are its compact design, the possibility to cool the device on both sides, the lack of bond wires and the limited number of

interfaces between materials with different thermal expansions [1].

#### **Standard Power Module Assemblies**

A power electronic module, or often shorter power module, is a packaged device that can contain different setups of switches and diodes. Common setups are half-bridges and full three phase inverters. Several switches and diodes are often parallel connected in order to increase the current capabilities of the module. Both MOSFET:s and IGBT:s are used in power modules, and the choice of which one to use depends on the application. There are power modules, often referred to as intelligent power modules (IPM), where peripheral electronics such as the driver and protective circuits are built in to the same package as the power devices. Common protection features are over current and short circuit protections, together with temperature monitoring.

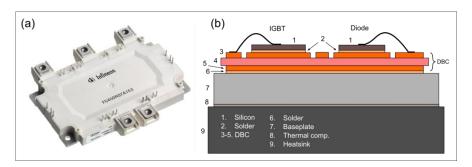

A cross sectional view of the most common power module packaging structure is presented in Figure 2.2(b). The figure also shows an example of an IGBT power module from Infineon [2], containing a full three phase inverter.

Figure 2.2 Power module from Infineon [2] (a) and a cross sectional view (b) of the layered power module structure.

The silicon chips are soldered onto an isolation layer that consists of a direct-bond-copper (DBC) structure, centred round a ceramic substrate. The ceramic isolation layer isolates, electrically, the current carrying parts from the rest of the module structure. Bond wires, normally made out of aluminium, are used for interconnections on the DBC. The bond-wires are also used to connect the current carrying part to the power module terminals. The DBC is soldered onto the module baseplate, which both

acts as a mechanical support, for the rather fragile DBC, and as a heat spreader, increasing the heat dissipating area. The module itself is often mounted on a heatsink that dissipates the heat generated within the module. Both the baseplate and the heatsink have surfaces that, in a microscopic scale, are not completely smooth. These irregular surfaces prevent good thermal contact and a large part of the contact surface is separated by a layer of interstitial air [3]. Since air has low thermal conductivity, a Thermal Interface Material (TIM) is used to enhance the contact. There exists a large variety of TIMs and the most common ones are commonly referred to as thermal grease. The thermal grease is applied to one of the surfaces and fills the micro voids with grease instead of air, greatly reducing the thermal resistance of the contact layer. However, it should be pointed out that the TIM layer is prone to degrade over time and can drift away as a consequence of the bending of the baseplate, caused by the thermal cycling.

There are two variants of the classical power module structure presented in Figure 2.2 that are getting more common. One is to omit the baseplate and mount the substrate directly on the heatsink, while the other is to use the baseplate itself as a heatsink. Omitting the baseplate has the benefit of reducing the stress in the solder joint between the silicon chips and the substrate [4]. The reason is that the substrate is mounted closer to the heatsink and hence will have a lower temperature, resulting in less stress between the chip and substrate. In addition to this, the large solder joint between the substrate and the baseplate is eliminated. This joint is a weak point and is often prone to failure [5]. A drawback is however that the thermal inertia is lowered and this can cause higher junction temperature swings in applications where frequent low frequency high power pulses occur [4]. The second variant mentioned is to omit the heatsink and let the baseplate itself act as a heatsink, often referred to as direct cooling. The heat spreading effect of the heatsink is then lost, but the effective baseplate area can be increased by using a pin fin structure [6]. A benefit of using direct cooling is that the thermal grease can be removed.

## **Power Module Assemblies for Enhanced Cooling**

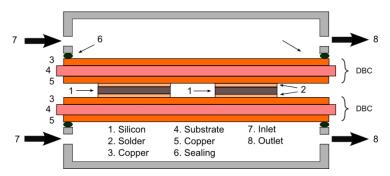

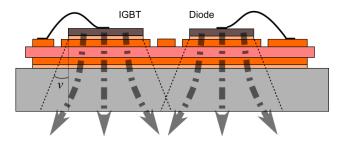

In addition to the more common power module assemblies mentioned in the previous section, more innovative solutions exists where the aim is to enhance the cooling of the device. Standard power module assemblies are normally cooled on the non-wire bonded side of the assembly. Omitting the bond wires, by using other interconnection solutions, makes it possible to cool the semiconductor devices from both sides. Some examples of different interconnection solutions where bond wires are not used are low temperature joining, flip chip solder balls, press pack, DirectFET, power overlay and embedded power technology [49]. The different bond wire free interconnection solutions are used together with different types of double-sided cooling techniques. The design solution presented in [50] – [52] is based on using two DBC:s, where the additional substrate is placed on top of the device, see Figure 2.3.

Figure 2.3 Power module based on two DBC:s with double sided cooling.

Using two substrates makes it possible to extract heat from both sides of the device, which, compared to a version with single sided cooling, has higher current carrying capability due to a reduced thermal resistance. From Figure 2.3 it can be seen that the proposed solution does not have any baseplate, which from a reliability perspective is beneficial since the solder layer between the substrate and baseplate is prone to degrade over time. The solution with two substrates and no baseplate is studied more in detail in later chapters of the thesis. Thermal simulations of the design solution are carried out and compared to a more standard solution with single-sided baseplate cooling.

There are several advantages of using double-sided cooling, where one have already been mentioned, a decreased thermal resistance, since heat is extracted from two sides and decreased number of layers within the module structure. The baseplate is the heaviest part of the power module assembly and omitting it has a significant impact on the total module weight. Another advantage is that the structure carrying the cooling liquid

can be made from any material, since it is not actually conducting any heat [50]. In the proposed solution the assembly is clamped in between the structures carrying the cooling liquid. The clamping force that needs to be applied is quite low since it only needs to be high enough to create a proof sealing. Due to the low clamping force, no mechanical stress is transferred between module assembly and the cooling structure [50].

There are mainly three drawbacks of the module assembly presented in Figure 2.3. The two substrates are in close vicinity to each other, around 100µm, and have a high electric potential difference which causes a high electrical field. This can be solved by etching of the DBC in exposed areas [52] or by using spacers to increase the clearance. Another drawback is that it is difficult to coincidentally bond the silicon chips to the bottom and top substrates [52]. Even though omitting the baseplate has its advantages, it can actually have a negative impact on the cooling performance, since its heat spreading effect and its thermal inertia is lost. Advantageous or not, is a question of the cooling technique applied to the module assembly. This is further investigated in Chapter 5.5.

## **Power Module Packaging Materials**

Power modules consist of several different materials and the most common ones are listed in Table 2.1. Included in the table are also the key parameters from a power module packaging and reliability perspective.

The most common material for the chip of commercially available power devices is Silicon. This has been the dominating material since the introduction of semiconductor devices in the middle of the twentieth century. The main reasons for the dominating use of Silicon are its simple processing, useful temperature range and low price. In later years, devices based on Silicon Carbide (SiC) have become more and more common. The reason for using SiC is its wider band gap, approximately 3 times higher than for Silicon, which results in much smaller intrinsic carrier concentrations [7]. Table 2.1 shows that the thermal conductivity for SiC is two to three times higher than that for silicon. This together with the lower intrinsic carrier concentration makes the SiC material more suitable for high temperature applications.

Thermal Coefficient Standard Dielectric Heat conductivity capacity of thermal thickness strength Material expansion  $[J/(kg \cdot {}^{\circ}C)]$  $[W/(m\cdot {}^{\circ}C)]$ [ppm/°C] [kV/mm] [µm] Si 150 712 70-250 SiC 340 830 2,8 400 24 Al<sub>2</sub>SO<sub>3</sub> 765 6.0 381 12 AlN 170 745 15 4,6 635 70 3.0 10 Si<sub>2</sub>N<sub>4</sub> 691 635 300/400 Cu 498 385 17.8 AlSiC 170-200 700-800 6,5-13,8 300/400 P12 1 1020 50-100 Х \_ Al 238 897 23,5 5000

Table 2.1 Key material parameters for materials used in power modules.

For attaching the chips to the substrate and the substrate to the baseplate, some kind of bonding material has to be used. The most common category of bonding materials for power semiconductors are solders, which are alloys of two or more materials. The most common solders today are variations of Tin/Silver (Sn/Ag) alloys. These solders have replaced the Tin/Lead (Sn/Pb) based solders used in the past, in order to meet new environmental requirements. The lead free solders have higher melting points and correspondingly higher reflow temperatures. Hence, using leadfree solders makes the soldering process more critical. The drawback of using traditional solders and the soft soldering technique, is that it cannot be used for junction temperatures above 125°C. The reason for this is that the solder joint is getting more sensitive to strain as the melting point of the solder is approached. Higher chip temperatures, approaching 175°C, will dramatically reduce the reliability of devices due to the soft soldering technique. When comparing different bonding materials a term called homologous temperature is often used and it is defined as the ratio between the maximum operating temperature and the melting temperature (in the Kelvin temperature scale) [8]. High ratios will result in poor mechanical strength and creep under stress. Ratios lower than 40% have very little impact on material properties. In the range between 40 to 60%,

material properties start to change and the solder is getting more sensitive to strain and for ratios above 60% materials are considered unable to bear engineering loads in a structure. [4]. The homologous temperature for the most commonly used soft solders today, assuming two different operating temperatures, 125°C and 175°C, are approximately 80 and 90%, respectively. These high ratios lead to fatigue cracks in the solder layers when the device is subjected to thermo-mechanical loading. This has resulted in the development of new soldering techniques, offering stronger chip die attach with a higher creep resistance. The two most promising techniques are transient liquid phase soldering (TLPS) [8]-[9] and silver sintering [9]-[11]. The homologous temperatures for these techniques are 52-65% [8] and 35% [4], respectively.

The reason for using a substrate is mainly to isolate the chip electrically from the baseplate. The substrate also serves as a supporting structure for the power module circuitry. Using a substrate is also beneficial for the reliability since the chip and substrate has better matching of CTEs, than chip and baseplate, which can be seen in Table 2.1. A substrate should offer high thermal conductivity, matching CTE with the chips, high dielectric strength and a low cost [12]. There are basically three substrate material candidates, Alumina (Al<sub>2</sub>SO<sub>3</sub>), Aluminium Nitride (AlN) and Silicon Nitride (Si<sub>3</sub>N<sub>4</sub>), all having its pros and cons, see Table 2.1. The most common one in power semiconductor applications is the Al<sub>2</sub>SO<sub>3</sub>. It offers low cost and average mechanical, thermal and electrical characteristics. The drawbacks are its relatively low thermal conductivity and rather high thermal expansion mismatch with Si [12]. A better option could be AIN which has a much higher thermal conductivity, a better thermal expansion matching with silicon and breakdown voltage capabilities. However, ceramic insulators based on AlN are considerably more expensive, a factor of two to three, than those based on Al<sub>2</sub>SO<sub>3</sub>. The last candidate is the Si<sub>3</sub>N<sub>4</sub>, which has good thermal conductivity and a very good thermal expansion match with silicon. It also has almost twice as high mechanical fractural toughness compared to Al<sub>2</sub>SO<sub>3</sub> and AlN. This makes it suitable for applications where it is beneficial to omit the supporting baseplate. A drawback is the higher price and limited number of suppliers [12].

The reason for using a baseplate in the power module package is to offer mechanical support for the, sometimes rather fragile, substrate. The baseplate acts as a thermal inertia, absorbing heat during power transients within the chip. The baseplate conducts the heat to the heatsink, and has a heat spreading effect which increases the effective heat dissipating area. Copper is the most commonly used material for baseplates due to its high thermal conductivity and relatively low cost. The drawback is its thermal expansion mismatch with the substrates. For high performance applications, where AlN substrates are often used, the preferred baseplate material is the Aluminium/Silicon carbide (AlSiC) metal matrix composite [1]. The reason for using AlSiC in these types of applications is the better matching in thermal expansion between the substrate and the baseplate.

## 2.2 Power Module Reliability

#### **Failure Mechanisms**

Power modules for traction in hybrid electric vehicles are subjected to several thermal cycles due to self-heating, where the losses generated within the device heats the module itself. The power module consists of several layers of several different materials, for which the coefficient of thermal expansion (CTE) can vary significantly. This variation in CTE induces stresses in the materials and in the interconnection of the different materials, as they are subjected to thermal cycling. The fatigue stress is a consequence of the bi-metallic effects and the actual level of stress depends on the thermal excursion or temperature swing. The most common failure mechanisms in power modules are bond wire fatigue, bond wire heel cracking, aluminium reconstruction and solder fatigue and solder voids [13]-[14]. The most dominant of these failure mechanisms is bond wire lift-off. This failure mechanism is mainly caused by the mismatch of the CTE for the aluminium wire and silicon chip. Repetitive thermal cycles induces shear stress on the interface between the bond pad and the wire and bending or flexure of the bond wire itself. Normally, several bond wires are connected in parallel to increase current capability. If a bond wire breaks, this results in an increased resistance and a redistribution of the current within the device. This will accelerate the failure rate of the remaining bond wires. The lift-off failure mechanism is also accelerated by solder fatigue. Solder fatigue increases the thermal resistance between the chip and the convective surface, and consequently causes the junction temperature to increase.

## **Reliability Estimation Models**

The reliability for the power modules studied in this thesis is estimated using two different reliability estimation methods. Both of the methods are developed through testing of a large number of devices, where the results serve as a base for fitting a function estimating the number of cycles to failure. Hence, the estimation models are based on statistical analysis of the device testing results. The first model studied is often referred to as the LESIT model. Several different modules from different suppliers were tested for a wide range of thermal conditions, consisting of different junction temperature swings at different mean junction temperatures. The results from these tests were first presented in [15]. Even though this model is relatively old, it has still in recent years been used as a starting point for power device reliability estimation [16]-[18]. The number of cycles to failure,  $N_b$  can be computed as

$$N_f = A \cdot \Delta T_j^{\alpha} \cdot e^{\frac{E_a}{k_B T_m}} \tag{2.1}$$

where  $k_B$  is Boltzmann's constant,  $E_a$  is the activation energy and A and  $\alpha$ are fitting parameters. The temperatures  $\Delta T$  and  $T_m$ , which are the temperature swing and the absolute mean junction temperature, respectively, are the dependent variables that determines the number of cycles until failure. The LESIT model is actually a combination of the Coffin-Manson law and an Arrhenius factor. The Coffin-Manson law states that the number of cycles until failure is a function of the plastic strain, which in turn is a function of the temperature swing [13]. In [15] it was shown that the number of cycles until failure, as a function of the temperature swing, appeared as straight lines when plotting them in a double logarithmic scale. As the mean temperature changed, the lines were shifted but still parallel, which indicates an exponential dependency. Hence, an Arrhenius factor was added to account for this thermally activated shift. It should be pointed out that the LESIT model was derived for mean temperatures ranging from 60 to 100°C, with temperature swings between 30 and 80°C. Hence, some care must be taken when the model is used for temperature combinations outside this range. Using the LESIT model for more recent power modules has proven to give a somewhat conservative estimation of the number of cycles to failure [17].

The second model used in this thesis was presented in [19], and is often referred to as the CIPS 08 model [1]. As for the LESIT model, this model is derived from extensive testing of different power modules. However, this model has more parameters and these are related to the power module type and layout. The number of cycles until failure,  $N_f$ , can be computed as

$$N_{f} = K \cdot \Delta T_{j}^{\beta_{1}} \cdot e^{\frac{\beta_{2}}{T_{low}}} \cdot t_{on}^{\beta_{3}} \cdot I^{\beta_{4}} \cdot V^{\beta_{5}} \cdot D^{\beta_{6}}$$

(2.2)

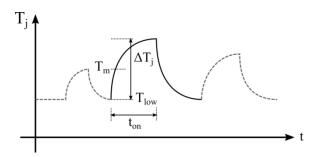

where K and  $\beta_I$ -  $\beta_o$  are fitting parameters chosen according to [19]. The model contains other parameters, such as the heat-up time,  $t_{on}$ , the current per bond stitch, I, the voltage range of the device, V, and the bond wire diameter, D. Both the LESIT and the CIPS08 model have the temperature excursion,  $\Delta T_j$ , as a dependent variable. The CIPS08, however, uses the starting point of the temperature swing,  $T_{low}$ , as a parameter instead of the mean temperature. Apart from this it requires an estimate of the heat-up time associated with the temperature swing, see Figure 2.4 for a definition of the variables. The reason for including the heat-up time in the model is to capture the fact that the different layers of the power module have different time constants. The top layers, and the associated failure mechanism of bond wire lift-off, have a time constant in range of seconds, whereas the solder layer between the substrate and baseplate has usually a time constant at least ten times higher. Hence longer pulses will not only contribute to the bond wire lift-off, but also solder degradation.

Figure 2.4 Definition of the heat up time and the different temperatures used in the LESIT and CIPS08 models.

It should be pointed out that the CIPS08 model was derived for a range of each parameter in Equation 2.2 [19]. Hence, some care must be taken when interpreting results derived from the model with parameters outside of the validated range.

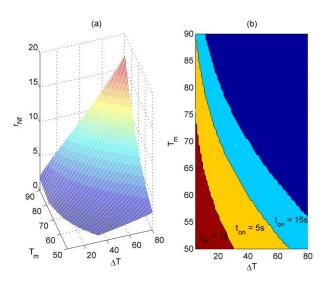

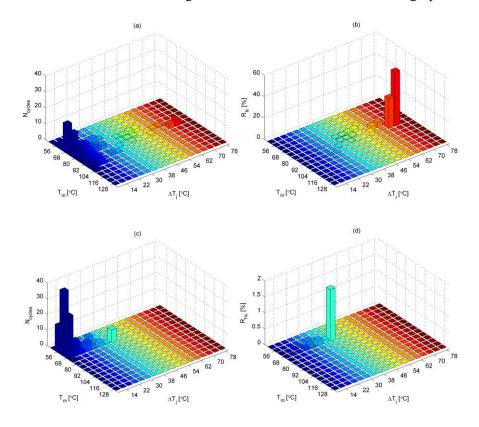

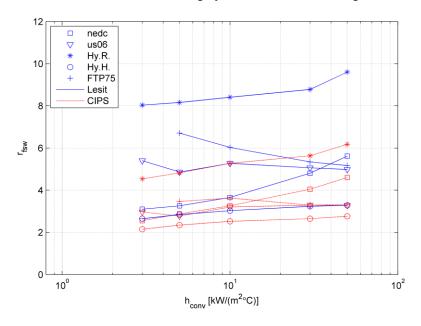

Both models presented above are used in the estimation of the lifetime for the modules studied in this thesis. It could therefore be of interest to compare the two models. Figure 2.5(a) shows a comparison of the number of cycles until failure for the LESIT and CIPS08 model. The comparison is presented as a ratio,  $r_{Nf}$ , of the number of cycles until failure for different temperature swings and mean temperatures, computed according to

$$r_{N_f} = \frac{K \cdot \Delta T_j^{\beta_1} \cdot e^{\frac{\beta_2}{T_{low}}} \cdot t_{on}^{\beta_3} \cdot I^{\beta_4} \cdot V^{\beta_5} \cdot D^{\beta_6}}{A \cdot \Delta T_j^{\alpha} \cdot e^{\frac{E_a}{k_B T_m}}}$$

(2.3)

The on time for the CIPS08 model is, in Figure 2.5(a) assumed to be 1s. Figure 2.5(b) shows for what combinations of the temperature swings and mean temperatures that the LESIT model estimates a higher number of cycles until failure than the CIPS08 model. This comparison is presented for three different on-times, 1, 5 and 15s, respectively.

Two important things can be seen in Figure 2.5(a). The first one is that the CIPS08 model estimates a higher lifetime for almost all combinations of the temperature swings and mean temperatures. For this particular case, where ton = 1s, the CIPS08 model estimates, at the most, a 20 times higher lifetime. The ratio is decreased as ton is increased and is at the most 5 for ton = 15s. Figure 2.5(b) shows in what range the ratio computed according to Equation 2.3, is less than one, i.e. where the LESIT model is estimating a higher lifetime. The ratio is computed for three different on times, 1, 5 and 15s. The result shows that the LESIT model estimates higher lifetimes for a range of combinations where the temperature swings and mean temperatures are low and this range is growing as the on-time is increased. Hence, for mission profiles consisting of shallow cycles at low mean temperatures, the LESIT model is estimating a higher number of missions until failure.

Figure 2.5 Ratio of number of cycles until failure between the CIPS08 and LESIT model (a). Showing regions in which the LESIT estimates a higher number of cycles until failure (b).

## **Linear Accumulated Damage**

A temperature profile consists of several temperature swings at many different mean temperatures. The reliability models presented here gives the number of cycles to failure for a specific operating point. Hence, a relation relating the different temperature swings and their associated number of cycles to failure must be used. The relation that is often used in literature is the Miner's rule [16], [20]-[21]. This relation can, for two variables, be written as [16]

$$C = \sum_{i,j} \frac{n_{i,j}}{(N_f)_{i,j}} \tag{2.4}$$

where C is the accumulated damage,  $n_{i,j}$  and  $(N_f)_{i,j}$  is the number of cycles and the number of cycles until failure for the ith mean temperature and the jth temperature excursion. When the accumulated damage, C, is close to one failure occurs. For any mission profile there will be different combinations of temperature swing and mean temperatures. Miner's rule can be seen as the linear combination of the induced stress portions for the

different thermal states. Equation 2.4 can be directly used in the case of reliability estimations with the LESIT model. However, for the CIPS 08 model, it needs to be extended. Miner's rule can easily be extended with more variables, since it is independent of the exact nature of the lifetime model [1]. The CIPS 08 model requires one more variable, the heat up time,  $t_{on}$ . When using Miner's rule, it is assumed that the accumulation of damage is linear. Hence, no respect is given to the order of the thermal cycling and the associated induced stress. However, as is pointed out in [16], the relation may still be used to derive a single value representing the accumulated damage of the device.

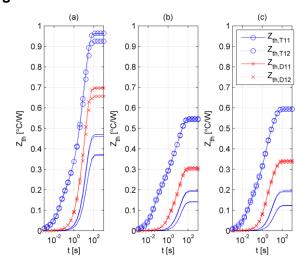

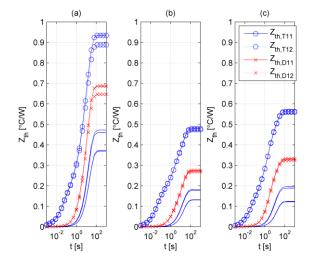

## **Thermal Cycling**

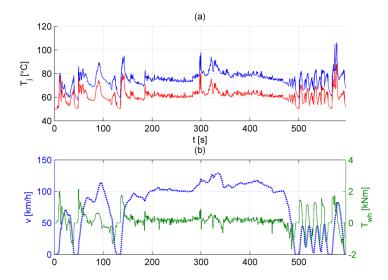

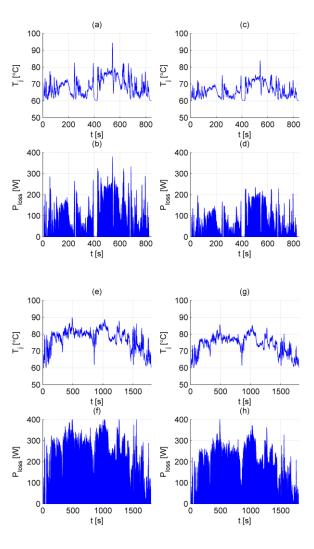

The output of the system simulations in the coming chapters are, among other things, the junction temperatures for the IGBT:s and diodes in the power module. The thermal cycling, imposed by the operation of the electrical machine, serves as an input for the reliability study. Figure 2.7 shows the IGBT junction temperature evolution for a well-known driving cycle named US06, for two different convection coefficients, 1 and 10 kW/(m².ºC).

Figure 2.6 IGBT junction temperature evolution for the US06 cycle for two different convection coefficients, 1,0 to  $10 \text{ kW/(m}^2 \cdot ^{\circ}\text{C})$ .

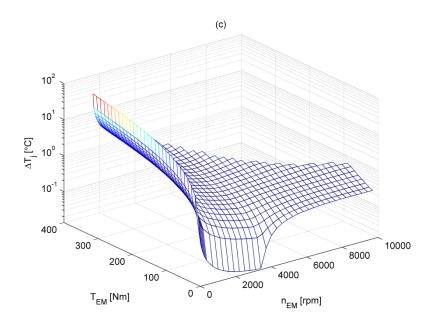

Figure 2.7 Vehicle speed and the driver requested wheel torque. IGBT junction temperature rise as a function of EM torque and speed for one electrical revolution (c).

The junction temperature excursion depends on the load conditions of the electric machine The IGBT temperature rise of the IGBT chip, computed for one electrical revolution, is presented in Figure 2.7. The figure shows that the most demanding operating points, in terms of temperature increase, are the ones with high torque and low speeds. High torques in combination with low speeds implies high currents and relatively low modulation frequencies compared to thermal time constant of the power module heatsink, which results in a high temperature swing. The figure also shows that operating the machine close to the maximum torque in the field weakening region results in high temperature excursions. The reason is that field weakening operation requires both high current and high voltage levels, resulting in high losses for the switches.

## **Cycle Counting**

The device experiences an irregular, or almost random, thermal cycling with different combinations of thermal excursions and mean temperatures. Cycle counting methods can be used to decompose these irregular thermal

evolutions into frequencies of these dependent variable combinations. Hence, cycle counting is used to determine the number of cycles of each combination of the dependent variables in the Miner's rule. The variables that need to be considered for the LESIT model are the mean temperature and the temperature swing or thermal excursion. The CIPS08 model also requires the temperature excursion, but uses the starting point of the excursion instead of the mean temperature. Apart from this it requires an estimate of the heat-up time associated with the temperature excursion.

## Rainflow algorithm

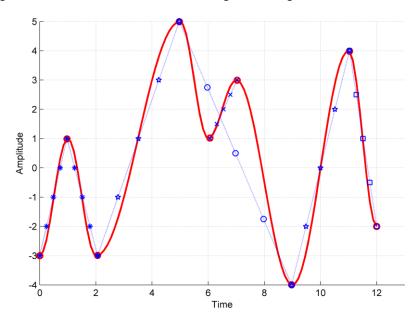

One of the algorithms used to extract the mean temperature and the temperature swing from the time evolutions of the junction temperature obtained from the full system simulations, is the rainflow algorithm. This algorithm is widely used for estimating stress/strain hysteresis loops within the area of fatigue life estimation [22]-[23]. Figure 2.8 shows an example of a thermal cycle and how the rainflow algorithm decomposes the cycle into temperature swings. Compare with Figure 2.9 for other cycle counting algorithms. The result of the rainflow algorithm is given in Table 2.2.

Figure 2.8 An example of how a cycle is decomposed into its subcycles by the rainflow algorithm.

The output of the rainflow counting algorithm is a matrix containing the number of occurrences of each combination of thermal excursion and temperature mean, together with the cycle period. The main difference of the rainflow algorithm compared to other cycle counting algorithms is that the rainflow algorithm really extracts the deep cycles, see Table 2.2 for a comparison.

### Other cycle counting algorithms

There are many ways of extracting the thermal cycles of a junction temperature profile. Six different cycle counting methods are described below [21] [47].

- "Rising edge": The height of the rising edge within a cycle is used as the amplitude for the whole cycle (see Figure 2.9(a)).

- "Falling edge": The height of the falling edge within a cycle is used as the amplitude for the whole cycle (see Figure 2.9(b)).

- "Mean edge 1": Computed by taking the mean of the Rising edge and Falling edge (see Figure 2.9(c).

- "Maximum edge": The maximum height of the rising and falling edge within a cycle is used as the amplitude for the whole cycle.

- "Minimum edge": The minimum height of the rising and falling edge within a cycle is used as the amplitude for the whole cycle.

- "Mean edge 2": Computed by taking the mean of the Maximum edge and Minimum edge.

The cycle counting method called Mean edge 1 and Mean edge 2 gives the same result. The main difference between the cycle counting methods presented above and the rainflow algorithm is, as has been mentioned before, that the later finds the deeper cycles within a temperature profile. This can be seen in Figure 2.9 and the results presented in Table 2.2.

Figure 2.9 Three examples of cycle counting methods, "Rising edge" (a), "Falling edge" (b) and "Mean edge 1" (c).

|            | Cycle               | 1  | 2 | 3    | 4   | 5   | 6   |

|------------|---------------------|----|---|------|-----|-----|-----|

| ě          | Δ                   | 4  | 2 | 8    | 9   | 8   | 6   |

| Rainflow   | Mean                | -1 | 2 | 1    | 0,5 | 0   | 1   |

| Ra         | N <sub>cycles</sub> | 1  | 1 | 0,5  | 0,5 | 0,5 | 0,5 |

| Mean cycle | Δ                   | 4  | 6 | 4,5  | 7   | ı   | -   |

|            | Mean                | -1 | 2 | 0,75 | 0,5 | -   | -   |

|            | N <sub>cycles</sub> | 1  | 1 | 1    | 1   | -   | -   |

Table 2.2 Comparison of cycle counting algorithms.

The cycle counting methods presented here is sensitive to temperature profiles containing ripple in the temperature, since these superimposed shallow cycles are extracted, resulting in the deeper cycles being overlooked [47]. This is a major drawback, since it is the deeper cycles that have the largest impact on the power module lifetime. One way to

2.3. Heat Transfer 27

partly overcome the sensitivity of the presented cycle counting algorithms, is to first filter the extracted temperature profiles. The rainflow algorithm is, due to its robustness, exclusively used for cycle extraction in the thesis.

### 2.3 Heat Transfer

The main purpose of any kind of cooling application for power electronics is to remove heat generated in the device chips to prevent the junction temperatures from reaching destructive levels. Heat can be defined as "the form of energy that can be transferred from one system to another as a result of a temperature difference" as stated in [24]. There are three basic mechanisms or modes for heat transfer, conduction, convection and radiation, and they are briefly described in the following section together with an overview of different power electronic cooling options.

#### **Modes of Heat Transfer**

Conduction is a heat transfer mechanism where energy is transferred in solids and stationary gases or liquids. The energy transport in solids is an effect of molecule vibrations and energy transport of free electronics, whereas the transport in liquid and gases is an effect of collision and diffusion of the actual molecules [24]. The heat transfer rate,  $\dot{Q}$ , through a plane layer due to conduction can be expressed as

$$\dot{Q} = -\lambda A \frac{dT}{dx} \quad [W] \tag{2.5}$$

where the constant  $\lambda$  is the thermal conductivity, which is a material property describing the materials ability to conduct heat, A is the heat transfer area and x is the direction of the heat conduction. The relation above is called the one dimensional form of Fourier's law of heat conduction. The rate of heat flux is proportional to the thermal conductivity and the temperature gradient across the layer. The minus sign is motivated by the fact that heat is always transferred in the direction of decreasing temperature. The dominating mode of heat transfer within power semiconductor devices is conduction. The main part of the losses generated in the device chip is transferred through the different layers down to the heatsink, where the heat transfer mechanism of convection finally removes the excess heat.

Convection can be defined as heat transfer to a fluid or gas, which has a bulk motion [24]. The heat transfer is a combination of conduction and energy transport due to the movement of the fluid or gas. Convection is normally divided into two main categories, natural and forced convection. Fluid motion due to buoyancy forces, induced by the differences in densities, is called natural convection. Forced convection is achieved by creating fluid motion by an external device, like a pump or fan. The heat transfer rate,  $\dot{Q}$ , due to convection can described by Newton's law of cooling, according to

$$\dot{Q} = hA_s \left( T_s - T_{\infty} \right) \quad [W] \tag{2.6}$$

where  $A_s$  is the convective area and the temperatures  $T_s$  and  $T_\infty$  are the surface and fluid temperatures, respectively. The parameter h is the convection heat transfer coefficient and is in the following text referred to as the convection coefficient. Determining the convection coefficient for a certain application is a complex task since it is determined by the combination of several factors, such as the surface geometry, the nature of the fluid, fluid properties and the bulk fluid velocity [24]. Thus, determining the convection coefficient for complex geometries is often done experimentally. Convection coefficients for different cooling methods commonly used for power electronics cooling can be found in the literature and this is further discussed in the section regarding Power Electronic Cooling Methods.

Radiation is a mode of heat transfer caused by thermal radiation, which is a type of electromagnetic radiation. Comparing the amount of heat emitted through radiation and the heat removed by forced convection in a power electronic application, shows that the latter is significantly higher. Hence, taking into account that the power devices are limited in temperature and that surfaces with low emissivities are common, the effects of radiation are left out in the thermal analysis carried out in this thesis.

### 2.4 Power Electronic Cooling Methods

Determining the convective heat transfer coefficient for a certain cooling method is often a difficult task, since it involves predicting advanced fluid motions around bodies. Many papers are published, where the convection coefficients for different cooling methods are determined. The cooling methods can be categorized as follows [25]

- > air cooling,

- liquid cooling,

- heat pipes,

- refrigeration cooling,

- thermoelectric cooling,

- phase change material based cooling.

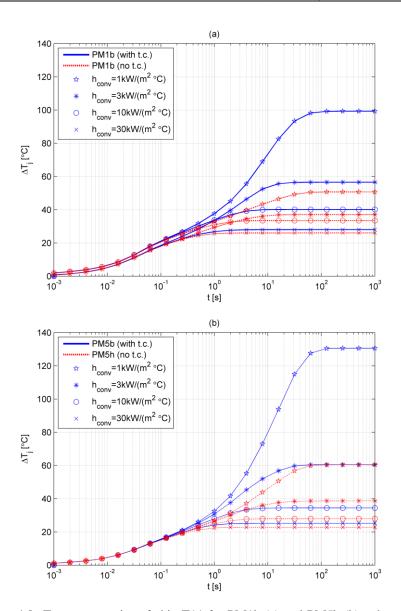

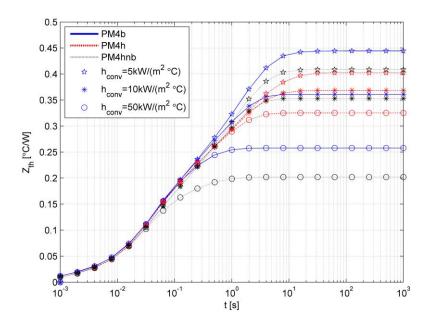

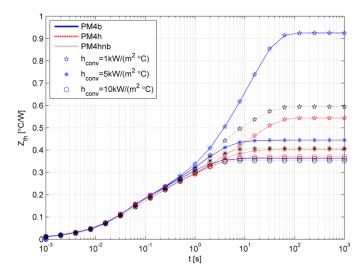

The convection coefficients for the different cooling methods used for power electronic cooling, ranges from approximately 20 W/(m²·°C) up to 300 kW/(m²·°C) [25]-[27]. A range of different convection coefficients is used in the simulations presented in this thesis. In order to cover the wide range of cooling options that could be used in a hybrid vehicle application, convection coefficients ranging from 0,5 kW/(m²·°C) to 50 kW/(m²·°C) are considered. This range covers the cooling methods of forced air cooling via traditional cold plates, to advanced types of liquid cooling, such as spray and jet impingement cooling. The convection coefficients are applied to the bottom of the baseplate or heatsink, depending on the packaging layout or assembly, and are hence assumed to be effective convection coefficients [28].

### **Chapter 3**

# Thermal Modelling of Power Modules

### 3.1 The Heat Conduction Equation

As was pointed out in Chapter 2.3, the main mode of heat transfer occurring in a power module is conduction. The heat generated in the device chips due to the inherent loss generation, is conducted through the layered structure of the device towards the heatsink, see Figure 3.1. Depending on the level of cooling, lateral heat spreading occurs, and this is indicated in Figure 3.1 as a heat spreading angle,  $\nu$ .

Figure 3.1 Heat conduction in power module.

The temperature distribution within the module can be determined by setting up the correct boundary conditions and solving the transient heat conduction equation for each layer within in the module. The transient heat conduction equation for a single layer is given below

$$\nabla (\lambda \nabla T) + \dot{g} = \rho c \frac{\partial T}{\partial t}$$

(3.1)

where  $\lambda$ ,  $\rho$  and c is the thermal conductivity, density and heat capacity, respectively. The generated heat within each layer is denoted  $\dot{g}$ . Solving the heat conduction equation requires knowledge about the geometry and material composition of the module. In addition to this, initial conditions have to be assumed and boundary conditions have to be set up. For simple geometries and one-dimensional problems, it is quite easy to obtain an analytical solution. However, for complex geometries and if heat spreading and thermal coupling, where chips are heating each other, has to be considered, obtaining a solution is a very complex task. Hence, numerical methods are used to achieve an approximate solution. Studying the literature regarding thermal modelling of power modules, four different methods for obtaining the temperature distribution can be distinguished. These methods are finite difference method (FDM), finite elements method (FEM) and the Fourier series solution method. These numerical methods together with the method of thermal RC-networks are briefly described in the following chapter.

### 3.2 Solving the Heat Conduction

### Finite Difference Method (FDM)

The FDM method is based on substituting the derivatives of the governing partial differential equations with differences. To compute these differences, the geometry is divided into a finite number of elements. The accuracy of the final solution is dependent on the number of elements, where more elements will result in a higher accuracy at the expense of more computational effort. The result of the discretization of the geometry and applying that to the heat conduction equation, is a set of approximate algebraic equations. These algebraic equations can then be solved numerically by different methods, such as Jacobi's method, Gauss-Seidel method or TDMA (Tri-Diagonal-Matrix-Algorithm), to mention a few.

### **Finite Element Method (FEM)**

The finite element method is, just as the finite difference method, a numerical method for solving various engineering problems. One of the most important features of the FEM is that it can handle complicated

geometries, whereas the FDM normally is restricted to handle rectangular shapes. As for the FDM, the FEM starts with turning the geometry of interest into small parts or elements. This division of the geometry into sub-parts is commonly referred to as meshing or generating a mesh. The elements are connected at node points. The next step is to approximate the unknown variables with a linear combination of algebraic polynomials and undetermined parameters, where the undetermined parameters are the wanted values of each node [48]. Algebraic relations for the parameters are derived by minimizing a weighted residual for each element. The last step is to put the algebraic relations together based on continuity and "equilibrium". Solving research and engineering problems with the aid of finite element analysis (FEA) is commonly carried out by using a commercial software package. The FEA tool used in this thesis is called ANSYS Workbench and is developed by ANSYS Inc.

#### **Fourier Series Solution**

The Fourier series solution method is an analytical solution method which is based on assuming a solution to the heat conduction equation in the form of a Fourier series expansion [29]. This method has in recent years been presented in [30] for a one-dimensional model and later presented in [31] and extended to two dimensional heat conduction problems. The accuracy and the simulation speed of this method depend on the number of harmonics used in the Fourier series expansion [31]. The method is according to [32] faster than the FDM with an acceptable level of accuracy and can easily be programmed in the Matlab/Simulink environment.

#### **Thermal RC Networks**

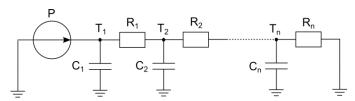

If the heat conduction equation is compared to the equation describing the voltage for an electrical transmission line, it can be seen that there are similarities. This equation can, in fact, serve as an electrical analogy of the heat conduction equation after some simplifications. An equivalent circuit diagram for describing a one-dimensional heat flow can be seen in Figure 3.2 Each R/C pair represents a layer in the power module structure. This type of network is often referred to as a Cauer network or model.

Figure 3.2 Cauer RC-network for one-dimensional heat flow.

In the electrical equivalent, power is equal to current and temperature is equal to voltage. The current source represents the heat dissipated as losses in the device chip. The thermal resistances and capacitances are computed based on material parameters according to

$$R_{th,i} = \frac{d_i}{\lambda_{th,i} \cdot A_i(v)} \quad [^{\circ}\text{C/W}]$$

(3.2)

$$C_{th,i} = c_i \cdot \rho_i \cdot d_i \cdot A_i(v) \quad [J/^{\circ}C]$$

(3.3)

where  $d_i$  and  $A_i$  are the thickness and area of layer i. The parameters  $\lambda_{th,i}$ ,  $\rho_i$  and  $c_i$  are the thermal conductivity, density and heat capacity for the material of layer i. Material properties for the materials in the power module are listed in Table 2.1. If a one-dimensional heat flow is assumed, a heat spreading angle, v, can be included to account for heat spreading effects [33]. Convection can also be included in the Cauer model as a thermal resistance. This resistance is obtained by rearranging parts Equation 2.6.

$$R_h = \frac{1}{h \cdot A} \quad [^{\circ}C/W] \tag{3.4}$$

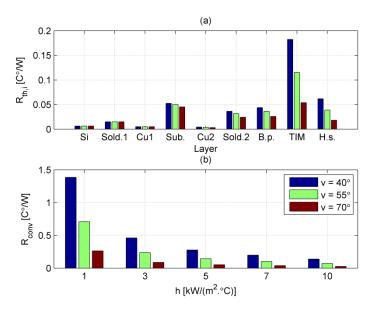

where  $A_s$  is the convection area. Figure 3.3 shows the thermal resistances calculated based on the dimensions for one of the power modules studied in this project. Different heat spreading angles,  $\nu$ , and convection coefficients, h, ranging from 40° to 70° and 1 to 10 kW/(m²·°C), respectively, are assumed.

Figure 3.3 Power module thermal resistances (a) for the different layers of an IGBT power module. Thermal resistances due to convection (b).

Figure 3.3(a), shows that the low thermal conductivity of the thermal interface material causes this layer to have the highest thermal resistance. Hence, keeping this layer as thin as possible is important in order to reduce the total thermal resistance. The resistance contribution from the substrate is also quiet significant and should thereby be kept as thin as possible, without jeopardizing the electric insulation capacity between the silicon chip and the baseplate. The thermal resistances decreases for a higher heat spreading angle since the assumed active area of each layer increases. The thermal resistance due to convection decreases both with the convection coefficient and the active area, which can clearly be seen in Figure 3.3(b).

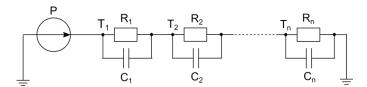

Physical based thermal models for power electronics are models that are based on the heat conduction equation. One example is the RC-network of the Cauer type, where the parameters are computed based on the geometrical and material properties of the power module structure. The Foster network is, in contrast to the Cauer network, not a physical based model. In fact it is often referred to as being a behavioural model. The reason for this originates from the fact that the thermal model is derived by fitting functions to measurements or simulation results obtained from FEA

calculations. An equivalent RC-network of the Foster type can be seen in in Figure 3.4.

Figure 3.4 Foster RC-network.

The main difference between the Cauer and the Foster network is the connections of the capacitors. In the Foster network, the capacitors are connected in parallel to the resistors, whereas for the Cauer network they are connected to ground. The response of the two models can be exactly the same for the temperature of the first node, which in most case are the junction temperature. However, it should be pointed out that the values of the thermal resistances and capacitances are not the same in the two models. The parameters in the Foster model does not have any physical relevance, as is the case with the Cauer model and since the parameters are derived for a particular response, dividing a network or connect two different networks is not possible. Hence, extending a Foster model for the junction to case temperature response with a model for the case to heatsink, is not possible by a simple series connection of the two models. Either the two models have to be transformed into two separate Cauer models or a new Foster model representing the whole system has to derived. Algorithms for transforming Foster networks to Cauer networks are presented in [34].

### 3.3 Transient Thermal Impedances

The transient thermal impedance (or resistance) for a semiconductor device describes the predicted temperature rise for a single rectangular power pulse of different lengths. The thermal impedance from the junction to the ambient is defined as

$$Z_{th} = \frac{T_j - T_a}{P} \quad [^{\circ}\text{C/W}]$$

(3.5)

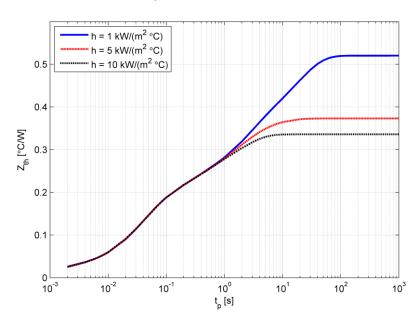

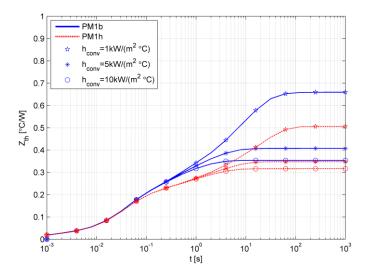

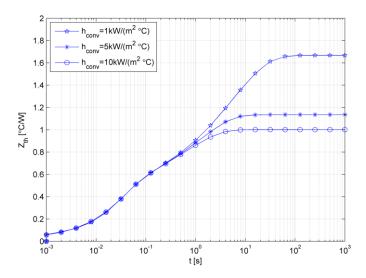

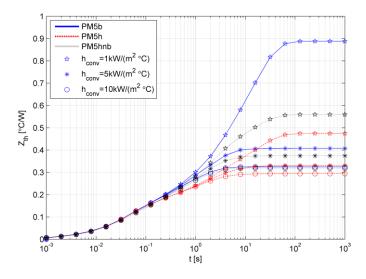

The thermal impedance is actually the unit step response. Three thermal impedances for an IGBT power module with three different convection coefficients are shown in Figure 3.5.

Figure 3.5 Thermal impedance for an IGBT with three different convection coefficients.

The figure shows that for a pulse length of less than 1 s, the thermal impedance of the device is independent on the level of convection. The reason for this is the lower thermal capacitances of the chip and the substrate compared to the baseplate. Hence, all of the dissipated heat is, during the duration of the pulse, stored in the chip and substrate. For pulse length above 1s, the heat has transferred down into the baseplate or heatsink. Hence, having a lower convection coefficient results in higher thermal impedance. The thermal impedance value for infinitely long pulses is equal to the steady state thermal resistance.

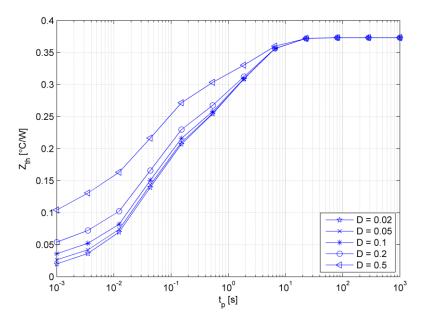

The transient thermal impedance for a single-pulse, presented in Figure 3.5, is more relevant for application as welding or induction heating than electrical drive applications. Hence, transient thermal impedance curves are often given for repetitive pulses of different duty cycles. Figure 3.6

shows the transient thermal impedance for repetitive pulses of different pulse widths and duty cycles ranging from 0 to 0,5.

Figure 3.6 Thermal impedance for five different duty cycles with a convection coefficient of  $5 \text{ kW/(m}^2 \cdot ^\circ\text{C})$ .

The heat losses generated in power semiconductor used in drive applications are normally of a more repetitive nature. In a three-phase inverter used for controlling an electrical machine, the diodes and switches of a phase leg are operated in pairs. During a switching period, depending on the current direction, it is either the upper transistor and the lower diode or the lower switch and upper diode, that are operated together to conduct the phase current. Hence, during one electrical period the switch/diode pairs will be active 50% of the period. Assuming electrical frequencies ranging from 0-500 Hz, the thermal impedance curves for pulse widths ranging from 5 ms to infinity with a duty cycle of 50 % are the most relevant for power devices used in drive applications. Figure 3.6 shows that the maximum junction temperature increases as the duty cycle is increased, since an increased duty cycle implies less time for the chip to cool off.

# 3.4 Mathematical Derivation of Foster Based Thermal Models

The development of the Foster network has its origin in Duhamel's theorem. This theorem is an analytical method that can be used to solve transient heat conduction problems when time-dependent functions are present. These functions can either appear in the boundary conditions and/or as source terms [37]. Duhamel's theorem can be written as

$$T(r,t) = T_0 + \int_0^t f(\tau) \left[ \frac{\partial u(r,t-\tau)}{\partial t} \right] d\tau$$

(3.6)

for the temperature evolution at point r. The time dependent boundary condition is denoted f(t) and the function u(t) is the temperature response to a unit step. The theorem can be used to compute the junction temperature response to its internal power loss. It can also be extended to include the internal heating or thermal coupling between devices taking place inside multi-chip power modules. If only a single heat source is considered, the temperature, T, at time t at point t can be computed by solving the Duhamel integral

$$T(r,t) = T_0 + \int_0^t P_i(\tau) \cdot \frac{\partial Z_{th}(r,t-\tau)}{\partial t} d\tau$$

(3.7)

where  $T_0$  is the initial temperature. The time dependent function f(t) and the unit step response u(t) in Equation 3.6 is, when applying the theorem to the calculation of the power module junction temperature, equal to the heat generated in the chip, P(t), and the thermal impedance,  $Z_{th}(t)$ . As will be studied later, the thermal impedance can be determined by fitting a suitable function to measurements or the results from FEA calculations. For a multichip module, more than one heat source needs to be taken into account. This can be done by applying the superposition principle [38]. The temperature evolution of device j,  $T_j(t)$ , due to several heat sources  $P_i$  can be written as

$$T_{j}(t) = T_{0} + \sum_{i=1}^{N_{i}} \int_{0}^{t} P(\tau) \cdot \frac{\partial Z_{th,ij}(t-\tau)}{\partial t} d\tau$$

(3.8)

where  $N_i$  is the total number of heat sources. The thermal impedance  $Z_{th,ij}$  is the thermal response of chip j to a unit power step applied to chip i. The space dependence on r has been dropped in the above equation, since it is assumed that all temperatures are calculated at the centre of every chip. The thermal impedance matrix, including thermal coupling between the different devices within the power module, can be written as

$$Z_{th} = \begin{bmatrix} Z_{th,11} & \cdots & Z_{th,1j} & \cdots & Z_{th,1n} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ Z_{th,i1} & \cdots & Z_{th,ij} & \cdots & Z_{th,in} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ Z_{th,n1} & \cdots & Z_{th,nj} & \cdots & Z_{th,nn} \end{bmatrix}$$

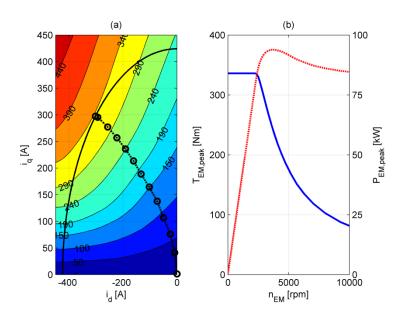

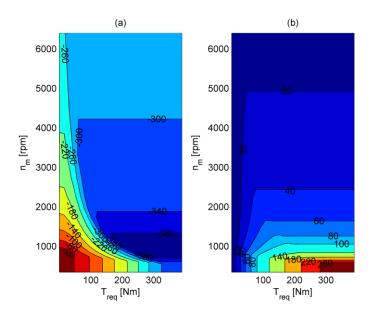

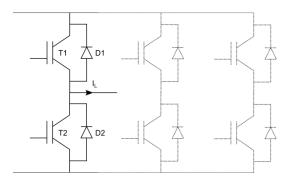

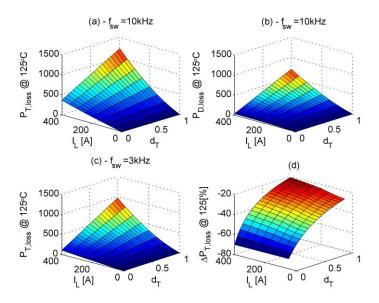

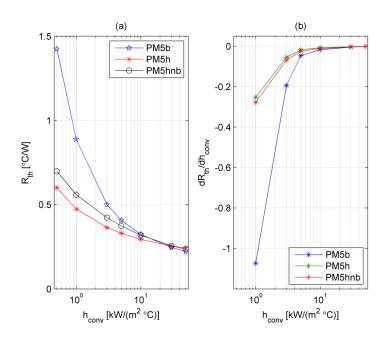

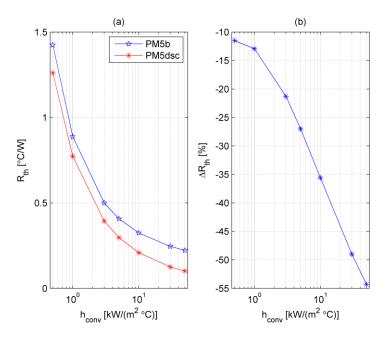

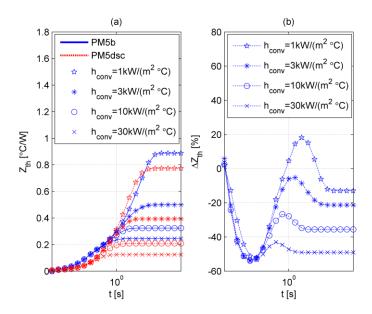

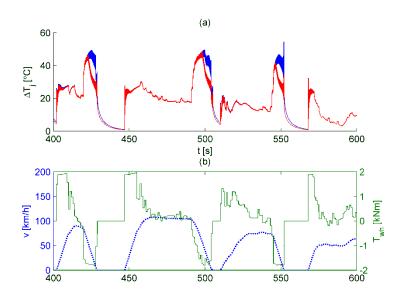

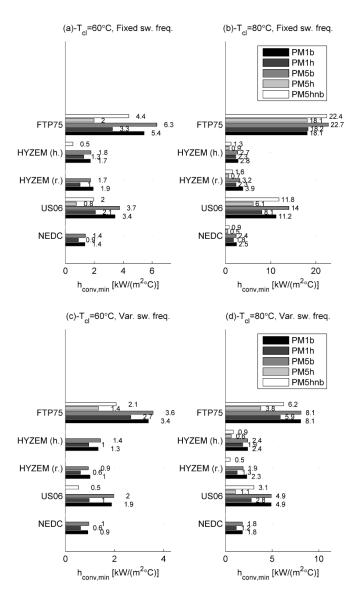

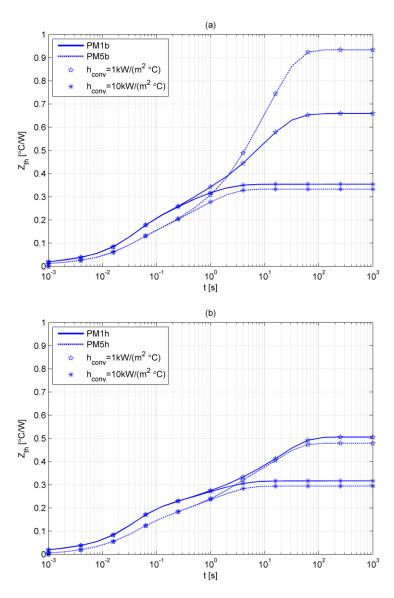

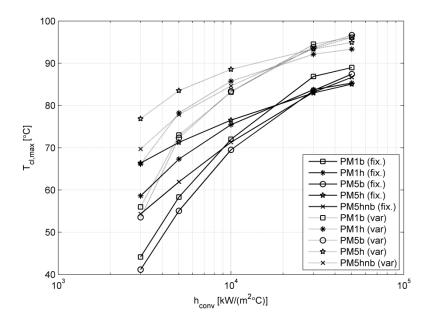

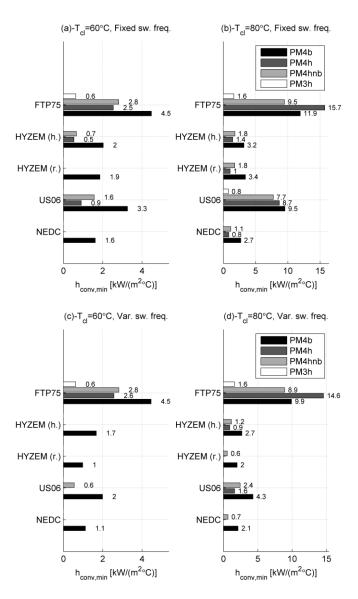

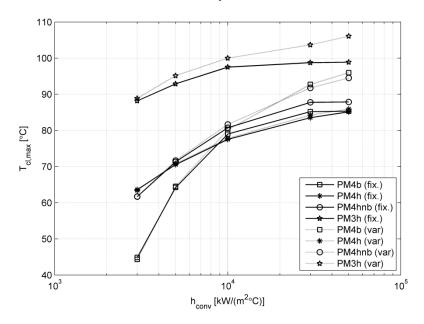

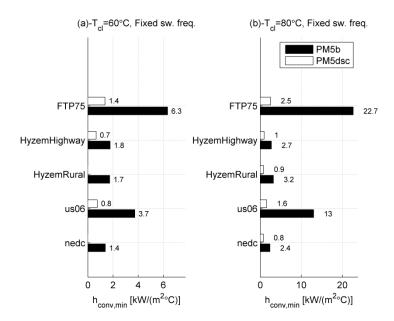

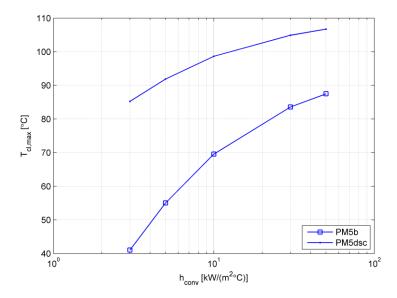

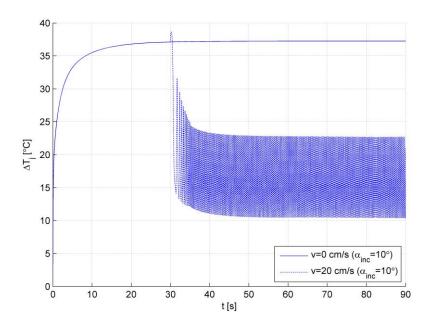

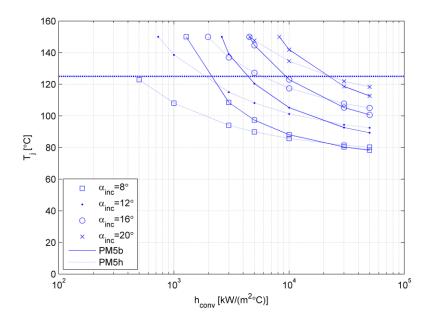

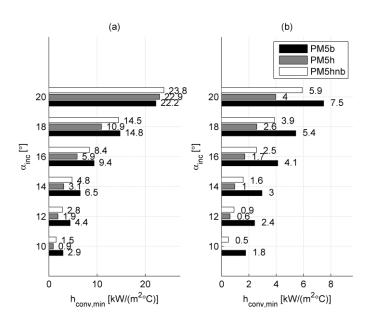

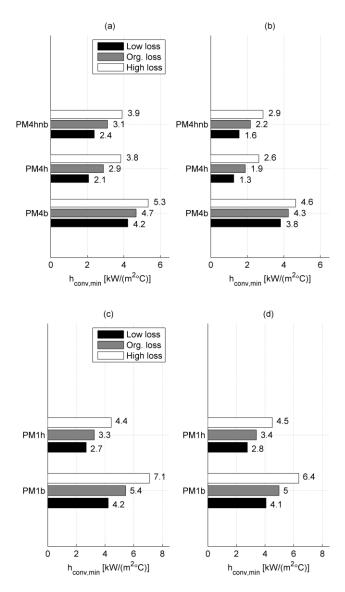

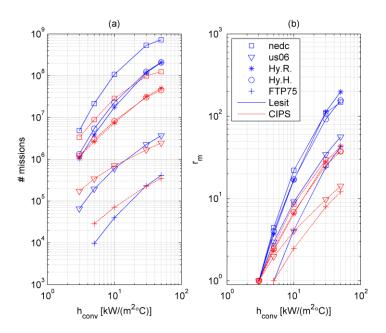

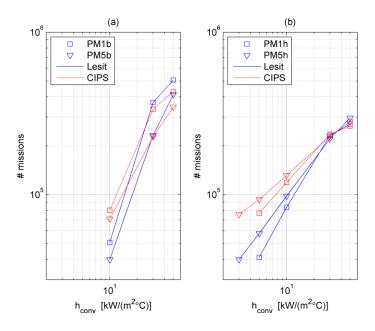

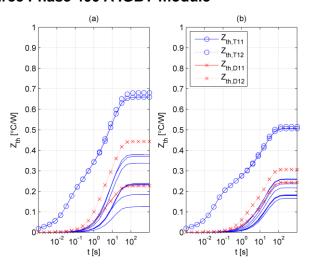

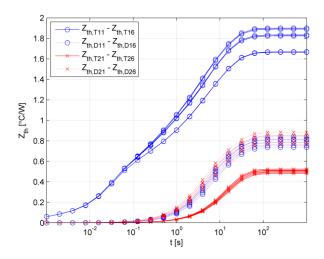

(3.9)