Department of Industrial Electrical Engineering and Automation Lund Institute of Technology

Box 118

221 00 Lund

Sweden

© 1999 by Hans Bängtsson

Published 1999

Printed in Sweden by Reprocentralen

# **Abstract**

In railway traffics the low friction between wheel and rail causes long braking distances, normally much longer than the driver's sight distance, i.e. if the driver starts the braking when a problem is discovered on the track it may be too late to brake the train. Therefore safe railway traffic can not only rely on the driver, there must also be a signalling or even a automatic surveyor system, which supervises the positions of different trains along the track and organise the traffic. Such a system uses train detection systems to check if a certain section of the track is occupied or not. Train detection systems can be disturbed by harmonics generated by the vehicle's drive system. Therefore it is necessary to be able to predict the line interference generated by a vehicle.

In this work, fast algorithms for calculation of harmonic from a traction drive system, based on three phase induction motors, are presented. The generation from both machine converters and line converters can be calculated. Both ideal and non-ideal commutations are taken into account.

The non-ideal commutations causes asymmetries, which can be compensated for. Following compensation methods are investigated in this work:

- Dead time compensation. The compensation method feeds back the differential between the integral of the inverter output voltage, or rather the output flux, and the voltage time area reference.

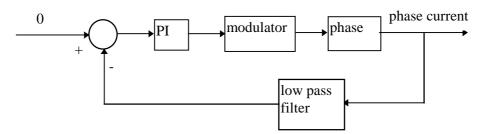

- Position asymmetry compensation. The compensation method is based on feed back of the DC-component in the machine inverter phase currents.

- Compensation of a remaining dc bias in Hall-effect current transducers. In the method, the fundamental current content in the DC-link current is fed back to the control system.

The compensation methods are found to be effective in most operating conditions.

# Acknowledgements

During this work I have been encouraged and supported by colleagues at Adtranz, by personnel at the Department of Industrial Electrical Engineering and Automation at Lund Institute of Technology and appreciates especially the support from my own family.

I would like to thank Prof. Mats Alaküla, Prof. Lars Gertmar and Prof. Gustaf Olsson, Anders Carlsson and Lars Buhrkall.

## Contents

# **Contents**

| 1. Introduction                         | 1   |

|-----------------------------------------|-----|

| 2. The Signalling System                | 9   |

| 3. The Traction System                  | 31  |

| 4. EMC Model of the Traction System     | 55  |

| 5. Compensation Methods                 | 83  |

| 6. Conclusions and Future Work          | 111 |

| 7. References                           | 113 |

| Appendix A. Commutation Delay Algorithm | 117 |

| Appendix B. ASCALP-Description          | 127 |

| Appendix C. The Test Set up             | 151 |

| Appendix D. List of Symbols             | 153 |

# 1 Introduction

In railway traffics the low friction between wheel and rail causes long braking distances, normally much longer than the driver's sight distance, i.e. if the driver starts the braking when he discovers a problem on the track it is too late to brake the train. The conclusions will be that the railway traffic can not only rely on the driver for the traffic safety, there must also be a signalling or even a automatic surveyor system, which can supervise the positions of different trains along the track and organise the traffic. Such a system exists, denoted "signalling system", but it can be interfered by the emission of harmonics from electrical traction drive systems.

This work presents solutions to some of the problems of guaranteeing safe railway traffic with electric trains when variable frequency AC-motor drive systems are introduced. Such drive systems generate undesired frequency components in the supply line, which can disturb the railway signalling system. The aim for the safety design is to guarantee that the interference does not cause a fatal disturbance. The signalling system as well as the traction system shares the rails for information and energy transfer:

**Energy**. The rails act as the current return path back to the substation for the power current. In a double rail system the current has the same directions in both rails and should be equally distributed between the two rails, i.e. the current is in common mode. In a single rail system only one rail is used as the current return path.

**Information**. To avoid collisions the signalling system uses train detection systems to indicate if a section of the track is occupied by a train. The standard train detection system, called a track circuit, is formed of one transmitter, the two rails and at least one receiver. The transmitter sends an electric signal in one rail to the receiver and the current returns to the transmitter in the other rail. The signalling current is in differential mode.

## 1.1 History

The track circuit was invented in the USA at the end of the last century, when all traffic was based on steam locomotives, and there was no risk of interference. With the introduction of electric traction the problems started. Originally this problem was solved by letting the train detection system use a certain frequency which was not generated by the vehicle drive system. This was possible in the days when AC track circuits were used on DC supplied lines where the traction motors were controlled by series resistor, and when DC track

circuits were used on AC-supplied lines where series motors were fed with a constant frequency adjustable voltage from a transformer. With chopper controlled drive systems it was still possible to handle the situation by letting the chopper frequency differ from the track circuit frequency.

However, with the introduction of variable frequency drive system, based on induction motors, the frequency spectrum, produced by the drive system, became more or less continuous. Interference with the same frequency as the train detection system frequency is occasionally generated.

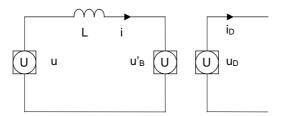

# 1.2 Definitions and an overview of a DC supplied drive system

DC supplied lines are normally used in suburban traffic, but also for high-speed passenger trains and in locomotives, operating on main line in densely populated areas. The onboard electrical equipment is simpler compared to trains on AC-lines. On DC supplied lines the line voltage is normally low, 750 V, 1.5 kV or 3 kV. The line current will be correspondingly high, and the voltage drop along the line demands short distances between substations, but as the distance between the feeding substations in suburban traffic is short this is not a big problem.

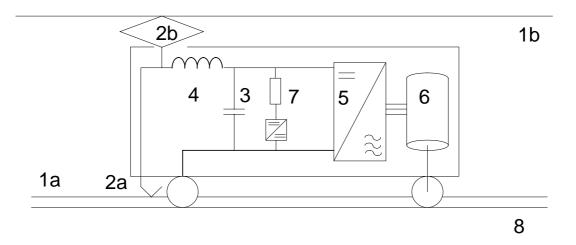

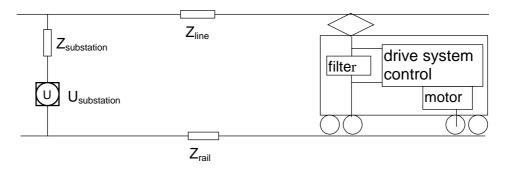

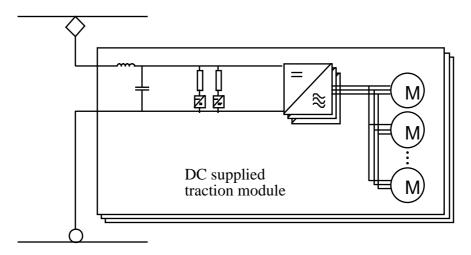

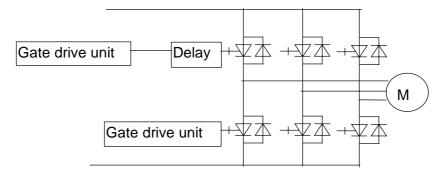

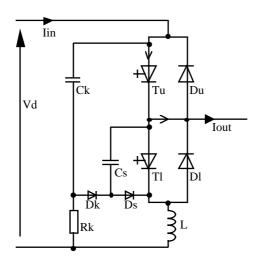

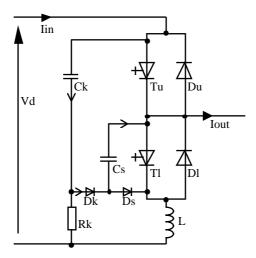

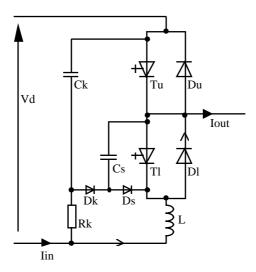

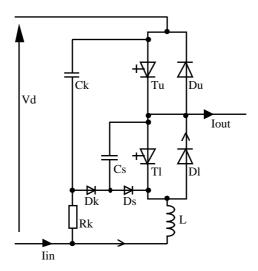

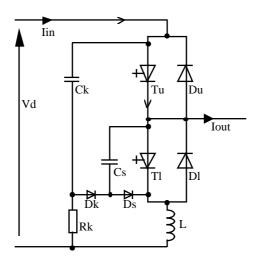

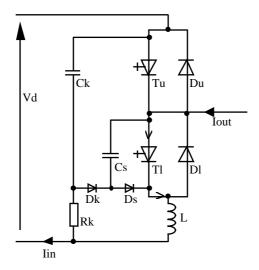

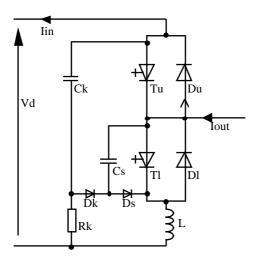

**Figure 1-1** A DC supplied AC-motor drive system with a brake chopper phase.

The main power handling parts of a DC supplied AC-drive system in a railway vehicle are depicted in figure 1-1.

1. The power line is either (a) a third rail situated at ground level, or (b) an overhead catenary. The advantage of a third rail system is its low

resistance due to the large cross section area, compared to the resistance in an overhead catenary with a small cross section area. The low resistance allows long distances between feeding substations. Third rail systems are normally used in combination with heavy traffic like subways and main line trains, where the supply voltage is below 1 kVDC (typically 750 VDC). An overhead catenary is used for tram systems, since it is impossible to use a ground level third rail, as the tram traffic often is mixed with other traffic. At voltages above 1 kVDC, like 1,5 or 3 kVDC, overhead catenaries are always used to supply any kind of DC-railway traffic.

- 2. In third rail systems current shoes (2a) are used as the current collector, pantographs (2b) are used in systems with overhead catenaries.

- 3. The voltage source DC-link where the capacitor stabilises the DC-voltage feeding the machine converter.

- 4. The line inductor forms together with the DC-link capacitor a line filter, which reduces line interference.

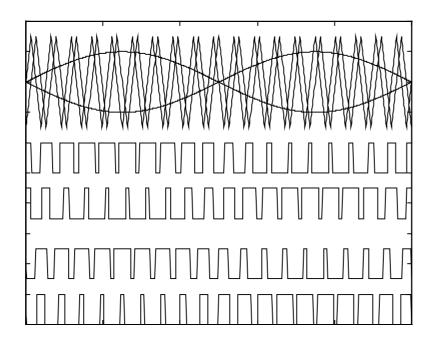

- 5. The three-phase machine converter produces the desired motor voltage at the desired motor speed. As the motor speed and the motor torque varies during the train operation, the motor voltage and the motor frequency will also vary. This is the reason why the drive system generates a more or less continuous spectrum of line interference. The inverter does not produce a pure sinusoidal output voltage, but the voltage is PWM-modulated, and the generated interference originates from both the variable fundamental frequency and from the modulator switching frequency. Due to imperfections in the power converters, low frequency harmonics on the motor side will be reflected in the DC-link.

- 6. The modulated voltage does not only give rise to line interference, it also produces undesired torque pulsation, sound and vibrations in the three phase squirrel cage induction motor and in the mechanical gear. Also for this reason, it is desired to reduce the harmonic content.

- 7. When the drive system operates in braking mode, the power shall normally be generated back to the line, but if this is unreceptive, the braking power is converted to heat in the brake resistor(s). The brake chopper operates also in pulse width modulation mode and will generate line interference, but with <u>constant</u> frequency.

8. The current, including harmonics, leaves the vehicle via the wheels and returns to the feeding substation in the rails, where interference can occur with the track circuit frequency.

# 1.3 Definitions and an overview of an AC supplied drive system

AC-supplied lines are used in high-speed passenger trains and in locomotives, operating on main line. By means of transformers in substation an on board the train, the line voltage can be high, 15 kV and 25 kV are standard levels in Europe. The line current will be correspondingly low, and the voltage drop along the line will therefore be low, and the distance between substations can be long.

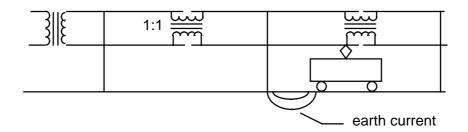

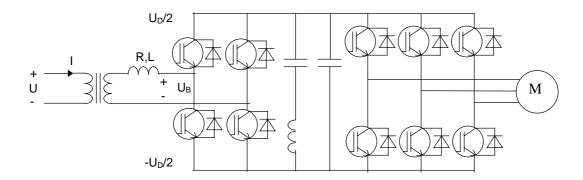

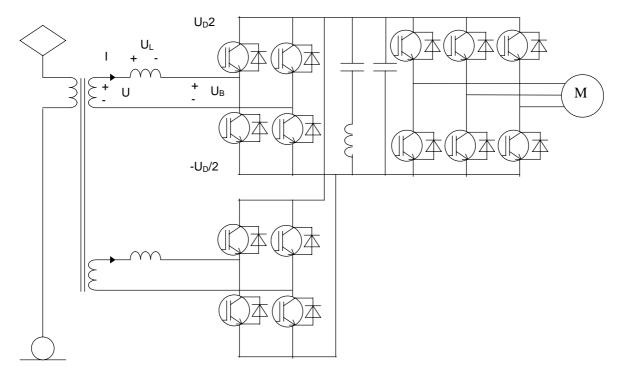

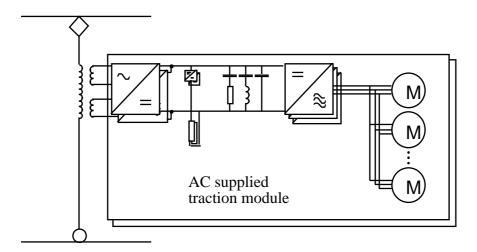

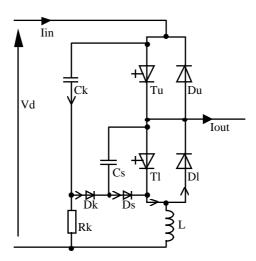

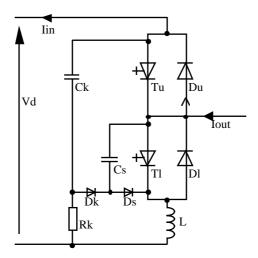

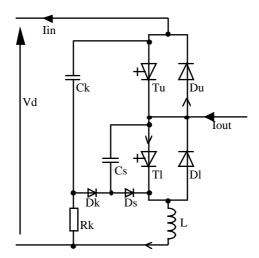

The main power handling parts of an AC supplied train with an AC drive system are shown in figure 1-2.

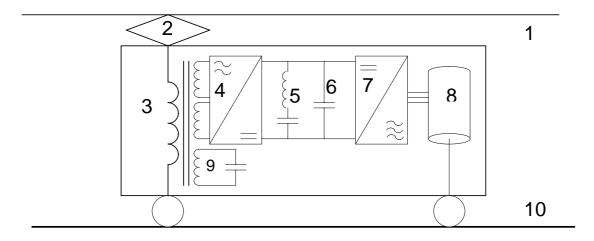

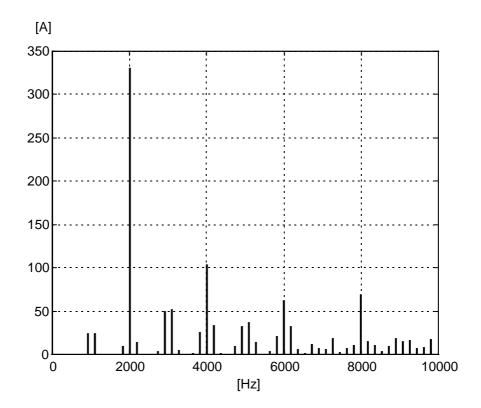

**Figure 1-2** An AC supplied AC-motor drive system.

- 1. In AC-supplied systems, the power line is always an overhead catenary, due to the high voltage.

- 2. The current collector is a pantograph.

- 3. The main transformer

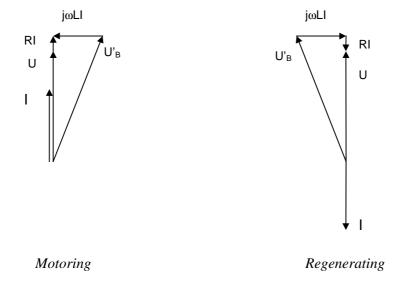

- 4. The line converter is a four quadrant ("4qs") converter, with two bridges, which can consume and regenerate power at unity power factor. The line converter rectifies the line voltage to a DC-voltage in the DC-link. Since the line frequency is constant, the line converter does not generate a variable spectrum except for the machine converter produced DC-link

voltage ripple, which will be modulated to the line by the line converter. From this point of view, the line converter can be compared to a chopper drive system, where the switching frequency can be selected to give a harmless influence.

- 5. The second harmonic link is a shunt branch. The function of the line converter is to rectify the line voltage and generate a DC-voltage, simultaneously a current component with twice the line frequency will be generated. The second harmonic link is a low-impedance path at twice the line frequency, and therefore the second harmonic ripple in the DC-link will be low. The second harmonic link must be carefully tuned.

- 6. The voltage source DC-link.

- The three phase machine converter produces the desired motor voltage at 7. the desired motor frequency. As the motor speed and the motor torque varies during the train operation, the motor voltage and the motor frequency will change. The inverter does not produce a pure sinusoidal output voltage, instead the voltage is PWM-modulated. The generated interference originates from both the variable fundamental frequency and from the modulator switching frequency. In a DC supplied drive system, the continuous spectrum from the machine converter results in a continuous spectrum of line interference. In an AC-supplied drive system, the continuous spectrum will not reach the line, instead it will cause a continuous spectrum of DC-link voltage ripple, that the line converter modulates to a line side spectrum, with variable sidebands around the line converter switching frequency harmonics. Due to imperfections in the power electronics, low frequency harmonics will be produced into the line.

- 8. The modulated voltage does not only give rise to line interference, it also produces undesired torque pulsation, sound and vibrations in the three phase induction motor and in the mechanical gear. Also for this reason, it is desired to reduce the harmonic content.

- 9. The line filter reduces the line converter interference.

- 10. The current return path via the wheels and the running rails. In AC-supplied lines the running rails are only partly used as the current return. With some arrangements the return current is removed from the rails to a cable situated in the mast tops, but some of the generated line interference will still be found in the running rails, where it can interfere with track circuits.

## 1.4 The challenge

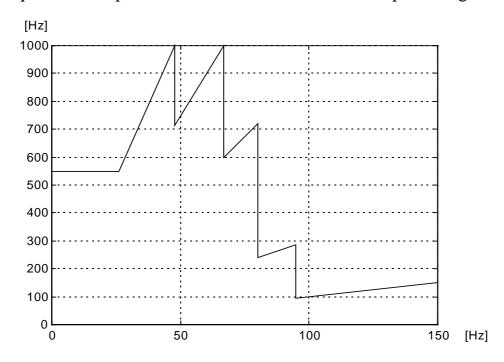

In modern AC motor driven trains, the spectrum from the machine converter is variable and the frequency of the harmonics depends on the actual vehicle speed. The spectrum from the line converter has varying amplitude, but as long as the frequencies are constant it is possible to avoid critical frequencies by choosing certain switching frequencies.

The continuous spectrum from the machine converter is the major problem in the low frequency area due to the switching pattern, restrictions like minimum pulse length. Besides the fact that the switching itself being non ideal, the actual switching will be delayed due to semiconductor component imperfections and due to snubbers, which makes the prediction more difficult. Therefore, this thesis is concentrated on machine converters and its non-ideal switching.

It is of fundamental importance that the line current spectra generated from the train does not interfere with the train detection system. The traction system has to be designed in order to avoid exciting critical frequencies for the train detection system, or the train detection system has to be designed in such a way that it is not sensitive for the spectra generated by the train.

Parts of the signalling system can be very old, and it has been designed without considering all the problems that new technique do cause. The signalling system, new or old, is also a part of the infrastructure. As Europe is becoming one region, trains will pass border between countries and therefore new traction drive systems must fulfil the demands of several signalling systems. The investments to install a new signalling system are normally very high. Therefore, the signalling system will not be changed when a new traction system is introduced.

One challenge is to be able to predict the emission from a drive system already at the design stage. Traditionally, it has been regarded that current in the rail or in the earth causes interference with the signalling system. However, as the switching in modern semiconductor based converters has become faster, other coupling mechanisms, e.g., inductive coupling, must be taken into account. Another challenge is the mitigation of those harmonics that are liable to disturb the train detection system. If the mitigation has to be done by passive filters, these have a tendency to become physically large. Thus, software based methods to obtain the same result ar of outmost importance.

# 1.5 The goal of the work

It is necessary to be able to predict the electromagnetic emission from the drive system already at the design stage in order to ensure that the generated level from a manufactured and commissioned vehicle will be lower than the detection level of the train detection system.

In the design stage of the drive system it is presumed that the induction motor is fed with a voltage which is based on an ideal modulation pattern, but due to imperfections in the modulator and in the power semiconductors undesired harmonics will be generated.

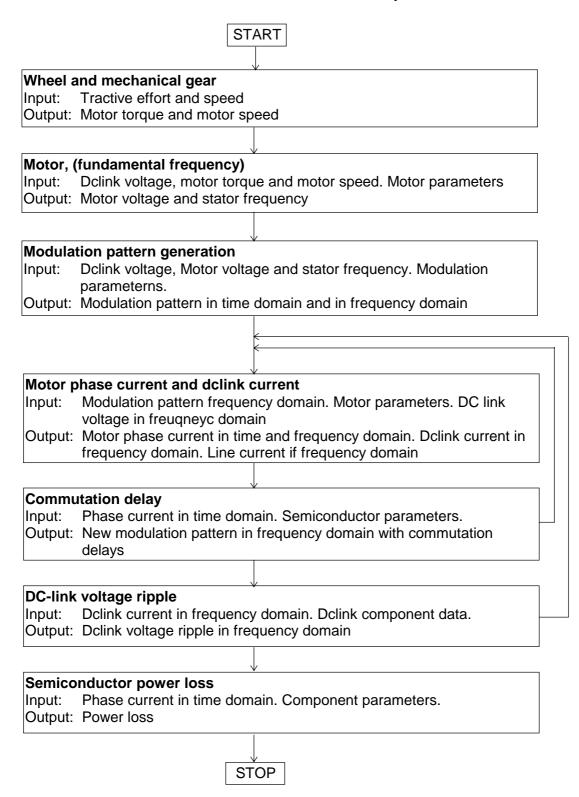

- The first goal is to construct and establish mathematical tools, which can be used to predict the emission of electrical interference from an electrical train, which has a traction drive system based on three phase induction motors. The algorithms shall also calculate the non-ideal effects as commutation delay, asymmetries etc., which always are present in a real converter.

- The second goal is to develop compensation methods by which it will be possible to reduce the generation of the undesired harmonics, which are generated due to the non-ideal effects in a real converter. The work is restricted to the motor inverter.

#### 1.6 Main contribution

The contribution from the author to this thesis is divided in two areas:

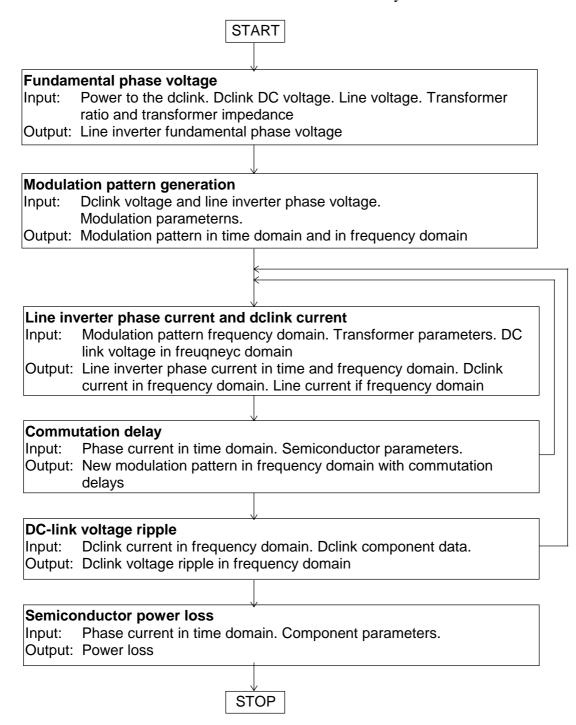

- The calculation program Ascalp, see chapter 4, which is used for fast calculations of generations of harmonics from a drive system based on three phase induction motors. In DC supplied drive systems, the generation from the machine converter, including brake chopper phases, is calculated. In AC supplied drive system the harmonics from both the line converter and the machine converter are calculated. In the latter case also the cross-modulation, where the machine converter DC-link ripple by the line converter can be taken into account.

- Three compensation methods, which reduces the machine converter generated harmonics caused by non ideal commutations. One compensation method reduces the harmonic with six times the fundamental frequency that is caused by the so called dead time. Another method reduces the harmonics, that are caused by asymmetries.

#### 1.7 The contents of the thesis

This paragraph is an overview of the content of the thesis. The first part is a description of today's signalling and traction equipment.

Chapter 2 is a description of existing signalling system. Especially the function and the interference mechanisms of different kinds of track circuits are described.

Chapter 3 is a description of traction drive systems based on three phase induction motors. Also a description of the drive system control is included.

Chapter 4 is mainly a description of the drive system as the source of line interference generation. In this chapter the calculation program Ascalp is described, which is used for calculation of the harmonic generation. In chapter 4 also the non-ideal commutation effects in the in the converter is classified.

In chapter 5, finally, compensation principles are presented, which can be used for correction of some of the non-ideal effects.

# **2** The Signalling System

As mentioned in the beginning of Chapter 1, a supervising system must be used in railway traffic. The supervising system controls that permission is given to one train to run on a certain part of a track section if, today automatic, it is ensured that the section is not occupied.

In the early days of railway traffic supervision was done by means of token. Each section of the track, normally the part between two stations, had its own, and only one, token, .i.e. a physical object used as evidence. A train was only allowed to run on a certain track section, when the train driver possessed the token. The token was given to him at the departure station and he left it at the arrival station, where he received a new token for the next track section. The token-based system works well when every second train runs in opposite direction. However when two trains after each other run in the same direction, the token must be brought back from the arrival station to the departure station by some other means.

When electricity was introduced in the society the problem was solved in an electrical way. In the station at each end of a track section a limited number of tokens were stored in a token instrument, one in each station. Both token instruments were connected electrically. When a token was taken from either of the two instruments, both became locked by electric means and it was not possible to take another token until the first token was returned to any of the instruments. In this way a number of trains can run in the same direction without any need for trains running in opposite direction. ([3] page 60).

When telephones and telegraphs were introduced, and today even radio, the "token" could be brought as a message, but to do this the token had to be converted from a physical to a logical thing. Instead the risk of duplication of the token arose. To avoid that two trains simultaneously got a token for the same track part, the rules and regulations of token handling became very rigorous.

However, even with rigorous rules, there was always an uncertainty if the track section really was not occupied when a train was given permission to run.

A need of a train detection system, that could check if the track really was free became more and more obvious. In today's complex railway traffic in and around big cities, the train detection system is a fundamental part of the computerised supervision and interlocking system.

Most train detection systems are based on track circuits, and therefore track circuits form the basis of modern signalling ([1] page 182), but have also become the most important victim of low frequency interference from the drive system.

The aim of all railway signalling systems is to prevent head-on and end-on collisions, prevent derailments and to allow trains to travel at maximum speed allowed for the line and for the vehicle. To achieve this, information about restrictions etc. is given to the driver by visual means, track side coloured lights or semaphore arms. Information can also be presented to the driver's cab by a display, often in combination with an audible signal and recently also as ATC ([2] page 5). The information from the train detection system is transferred to the supervising traffic control, where the track interlocking is done.

A signalling system has the following key elements ([2] page 5):

- A train detection system based on track circuits or axle counters

- Control of points and crossings (a point is where a track is split in two tracks or two tracks are merged into one single track)

- Interlocking of points and signals

- Indication to the driver by line side signals or cab signalling

- Enforcement of signal controls on the train with train stops or ATP (automatic train protection)

- Braking characteristics of the trains on the line

### 2.1 The track circuits

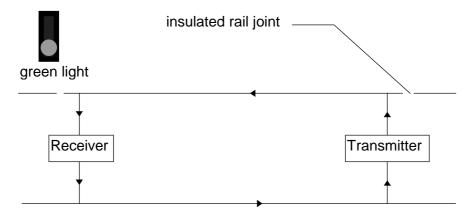

The main purpose for the track circuit is to prove that there are no other rail vehicles in a track section. When this is done, points may be operated and signals may be cleared for a train to move safely into the section. The second purpose for the track circuit is to detect the presence of a train within a certain section of the track. When this is being done the route ahead of the train will be locked in order to ensure the safe transit of the train ([1] page 182). The track circuit makes it possible to indicate on the train traffic surveyor's control panel the detailed position of a train along the track in order to keep the surveyor knowing where different trains are. The track circuits consists of a transmitter, a receiver and the two rails. The transmitter sends a signal to the receiver at the other end of the track section and the running rails are used as conductor to connect the transmitter to the receiver. If there is a train in the track section the signal will be short circuited by the wheel sets in the train and no signal reaches

the receiver. The track circuit is isolated from adjacent track circuits by means of insulated rail joints, that prevents the signal from interfering other track circuits. The insulated rail joints must not prevent the traction current (the power current) from returning to the sub station. There are three ways to achieve this:

In **single rail system** one rail, "the traction rail", is used for traction current. This rail has no insulated rail joints. The other rail, "the signal rail", is divided into insulated sections. A track circuit is formed of one of these sections and the corresponding part of the traction rail. Single rails system is used on tracks with such traffic, where the traction current has a small magnitude, i.e. traffic with low weight vehicles, the number of vehicles is low or where high voltage supply is used. The voltage drop in the running rail is therefore low, despite that only one rail is used as the traction current return. Single rail track circuits are normally not allowed at crossings, due to the current shunt in the surrounding earth. The ballast resistance is low due to salt etc. ([7] page 2).

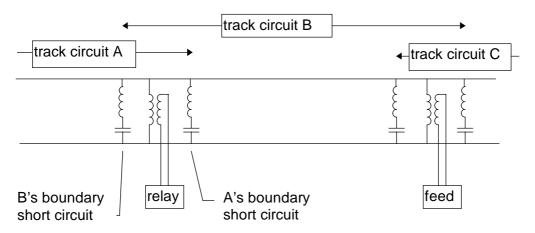

In **double rail system** the traction current has high magnitude and is equally distributed between the two rails, the traction current is a common mode current. The signal current has different directions in the two rails and is therefore a differential mode current. Both running rails have insulated rail joints, see figure 2-1. Between adjacent track circuits an impedance bond is connected, which has a low impedance for common mode traction current and a high impedance for the differential mode signal current. The impedance bond allows the traction current to pass on to the feeding supply substation, but prevents the signal from reaching adjacent track circuits and from shunting the receiver. This system is used on the tracks with heavy traffic, where both running rail must be used as traction current return, in order to keep the voltage drop low.

Track circuit systems on continuously welded rails shall preferable not use insulated rail joints, and therefore jointless track circuits are used. In these kind of track circuits the signal current is prevented from passing to adjacent track circuits by means of a short circuit between the rails, normally a tuned LC series link. Adjacent track circuits use different frequencies and therefore each track circuit uses its own tuned link. At the short circuit a train can not be indicated, because a short circuiting wheel axles have no meaning there. Instead adjacent track circuits overlap, see figure 2-23.

### Safety.

Fail safe. The signalling system must be designed to be fail safe. Any component or subsystem failure must lead to a default safety state which

ensures safety in all circumstances ([2 ] page 5), i.e. the track side signals shall turn to red. Electronic design and components must comply with the following: ([1] page 198): "Components must be chosen to avoid any possibility of self oscillation, and all transistors and other active components must be continually switching, and failure, whether an short circuit or open circuit, must cause the relay to drop."

**Right side failure** means that a not occupied track circuit is indicated as occupied. This situation is not dangerous but leads to traffic disturbance.

Wrong side failure means that an occupied track circuit is indicated as not occupied and it is of course a very dangerous situation. The design of a signalling system is to prevent a wrong side failure to happen. Coding is one traditional way to immunise a track circuit, i.e. to decrease the probability for a wrong side failure. Examples are the phase shift in an AC power frequency vane relay track circuit sections, or the switching between two frequencies in frequency shift key (FSK) track circuit sections. The problem of coding is that it reduces the probability for a wrong side failure to almost nothing, but the probability for a right side failure is increased, at least as long as the electric interference is unchanging, and this will lead to disturbed traffic.

**Restrictive side**. Stop is normally coded as no signal, and if the signal disappears because of an error, the train will automatically be stopped.

Response time. A track circuit can respond to transients, caused by sudden change in torque reference, by bouncing current collectors etc., because transients contain a wide band of frequencies. The most effective way to immunise the track circuit receiver against transients, is to make the response time as long as is possible concerning the interlocking and control system. A track circuit shall be "fast to drop, slow to pick up", i.e. it shall turn to red quickly but turn to green slowly.

# 2.2 Principal aspects of track circuit action

### The track circuit is not occupied.

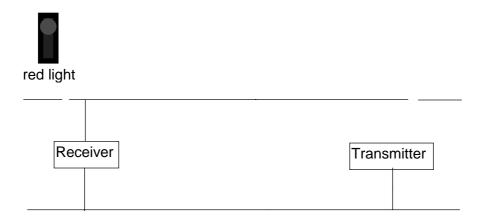

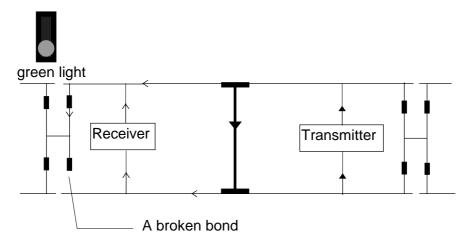

In the basic function the transmitter sends the signal to the receiver, and if the receiver receives the signal the track circuit is regarded to be not occupied, and another train is allowed to enter the track circuit. The green light is turned on if the train traffic surveyor allows traffic in the actual section and in the actual direction, see figure 2-1.

Figure 2-1. An unoccupied track circuit.

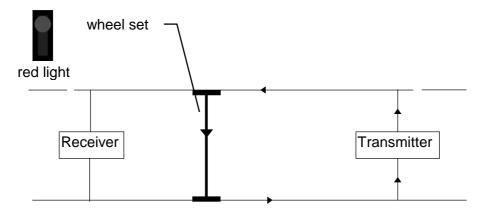

### The track circuit is occupied.

When a train occupies the track circuit, the current signal will be short circuited by the train's wheel axles and the current will not reach the receiver, and the track circuit is regarded as occupied and another train is <u>not</u> allowed to enter the track section. The red light is turned on. See figure 2-2. An advantage with track circuits is that even a "dead" vehicle will be indicated, as long as it has the capability to short circuit the rails.

During work on the track, when an accident has occurred or at other occasions when a train is not allowed to enter a certain track section, a short circuit between the two rails can be done by means of a wire.

**Figure 2-2.** An occupied track circuit

#### Fail safe.

If there is a current interruption in the supply to the transmitter, to the receiver or in the track circuit the train detection system will not work, but as no current signal reaches the receiver, the track circuit will automatically be regarded as occupied. The red light is turned on, see figure 2-3.

**Figure 2-3.** A track circuit with the transmitter disconnected.

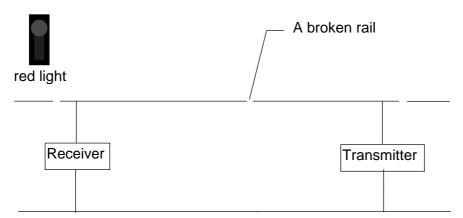

#### Broken rail.

If one rail is badly broken, there is a derailment risk, and therefore a train is not allowed to run on that part of the track. Fortunately a broken rail is also a circuit interruption. As no current signal will reach the receiver, the track part will automatically be regarded as occupied. The red light is turned on. See figure 2-4.

**Figure 2-4.** A track circuit with a broken running rail.

### Disadvantage with poor rail isolation.

If the rails are not carefully isolated from earth shunts, some part of the current signal will be shunted to the other running rail via wet and dirty sleepers. If the track circuit is long enough all current signals will be shunted and no current is

left for the receiver. The track circuit will be indicated as occupied. The red light is turned on. See figure 2-5.

**Figure 2-5.** A track circuit with bad isolation from earth.

# 2.3 Track circuit interference mechanisms

In a machine converter fed AC-motor drive system the variable output frequency forms a problem. The design of the machine converter modulation pattern has the restriction to avoid generation of output frequencies which will appear in the line current as frequencies equal to and interfering with the track circuit frequencies. The machine converter is often combined with a brake resistor chopper. The brake chopper produces a constant frequency, which can be chosen to differ from the track circuit signalling frequency. The brake chopper frequency can however cross modulate the machine converter DC-link ripple frequencies and can give rise to unexpected interference frequencies.

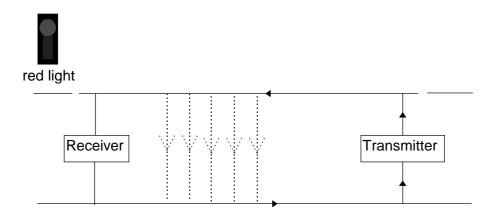

# Interference with the traction current return path in the running rails.

In double rail track circuit systems the traction current shall ideally be distributed equally between the two rails, the current is a common mode current. The track circuit receiver is not sensitive to common mode current in the rails and shall therefore not be sensitive to harmonics in the traction current. In single rail track circuits systems, the traction current return is by definition in differential mode, but the track circuit system shall be designed for this. However during abnormal situation like a broken impedance bond in double rail system or a broken rail in a single rail system a higher amount of traction current will pass the receiver and can then interfere with the track relay in a not

occupied track section. The light will turn to red, a right side failure. See figure 2-6.

**Figure 2-6.** A track circuit that is interfered by a fraction of a traction current from a adjacent track section which passes the track receiver where it cancels the track circuit current in a not occupied track section.

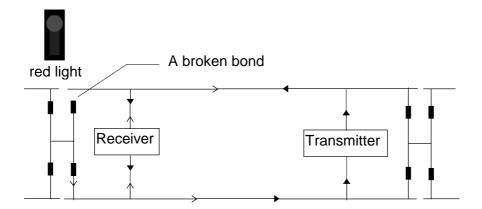

Another situation, and much more serious, is shown in figure 2-7. The track section is occupied and the light should be red, but due to the broken bond a fraction of the traction current is forced to pass the receiver. In this case the frequency and phase content of the traction current is assumed to be such that it can trip the track circuit receiver. As the receiver responds to the signal, the light is turned to green, *a wrong side failure*.

**Figure 2-7.** A track circuit that is interfered by a fraction of the traction current that passes the track relay in an occupied track section

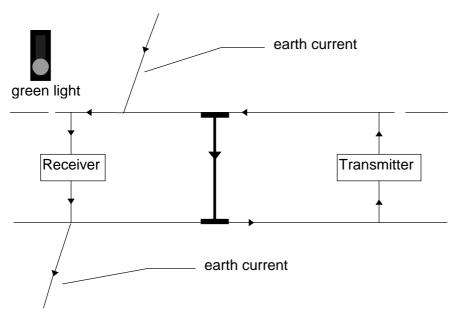

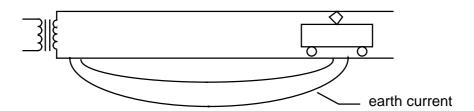

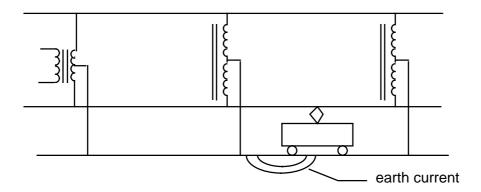

#### Interference from earth current.

When tracks are not isolated from earth the current return from tracks in the vicinity can also be found in stray earth currents, which can pass the track circuit receiver in another track and interfere with track relay. Similar situations as those described in figures 2-6 and 2-7 can happen, either a not occupied track can be indicated as occupied or an occupied can be indicated as not occupied. An example of a wrong side failure is shown in figure 2-8.

**Figure 2-8.** A stray earth current with the correct frequency content passes the track circuit receiver

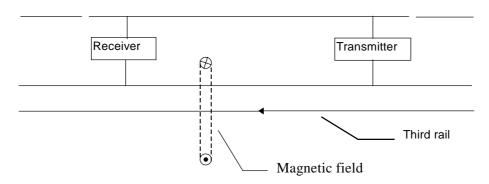

# Interference from a differential mode current induced by the third rail current.

**Figure 2-9.** Interference from a third rail or from an overhead power line to the track circuit.

The traction current in the third rail, in the catenary or in an overhead power line will induce differential mode current in the track circuit, see figure 2-9. If the harmonic content in the traction current is high or the track circuit trip level is low, the track circuit can be disturbed.

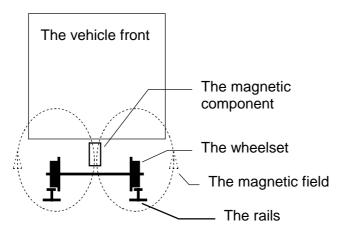

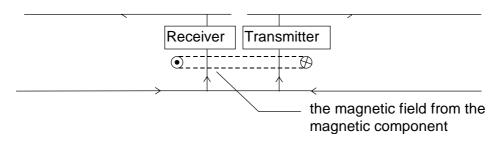

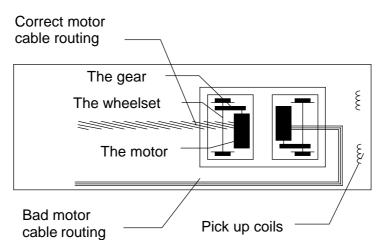

# Interference from a differential mode current induced by magnetic components on board the train.

Magnetic devices on board the train can induce a differential mode interference current in the track circuit, especially when they are mounted in the vehicle under-frame. The inductive coupling depends on the orientation of the magnetic axis of the component. The worst orientation is a vertical orientation where the magnetic field effectively is coupled to the track circuit, see figure 2-10.

**Figure 2-10.** *Inductive interference from components with a vertical magnetic axis.*

An orientation of the magnetic component where the magnetic field can go down and return within the same track circuit will be a correct installation and no interference current will be induced.

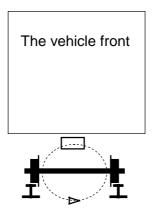

**Figure 2-11.** A magnetic field which normally is safe can at the boundary interfere with two track circuits.

The best orientation seems to be with the magnetic axis along the track. With this orientation the component can be installed anywhere in the underframe. But this orientation has one disadvantage; at the track circuit boundary the magnetic field can go down in one track circuit and return in the adjacent track circuit, and interference currents will be induced in both track circuits, see figure 2-11. Finally, the best orientation is obviously with the magnetic axis horizontal and perpendicular to the track direction. If this orientation shall be effective, the magnetic component must be installed above the midpoint between the two running rails, see figure 2-12.

**Figure 2-12.** *Inductive interference from components with the magnetic axle horizontal and perpendicular to the track direction.*

# 2.4 Track circuits in reality

Track circuits signal frequencies vary from DC to some tens of kHz. In Sweden the number of different kinds are limited. On the AC supplied main lines DC track circuits are used, and SL, Stockholm Underground, uses 75 Hz AC track circuits. On the other hand, in UK almost any kind of track circuit can be found.

In this thesis four different kinds will be described: DC track circuits, power frequency AC track circuit, audio frequency AC track circuits and high voltage impulse track circuits.

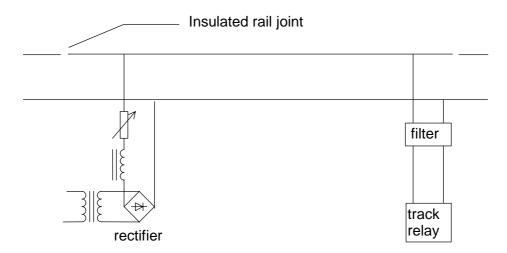

#### DC track circuit.

DC track circuits are the simplest and least costly track circuits and should therefore be the first choice, as long as the track is not DC supplied ([8] page B1). The first track circuits, invented over a hundred years ago, used dry cells as electric energy supply. This system worked well in combination with steam locomotive technology. With the introduction of electrical traction this system

was easily disturbed. At this point the never ending story of traction current interference with track circuits started.

DC track circuits shall only be used on AC supplied lines, not on DC supplied lines. It is always a bad combination to have the same frequency in the track circuits as in the traction supply.

On AC supplied lines the voltage is high and consequently the current is low. Therefore a single rail system can normally be used. The track circuit is fed via a rectifier and an inductor is smoothing the current. A variable resistor is used to adopt the current level. The receiver is protected from interference AC current by means of a filter, see figure 2-13 ([1] page 196).

Figure 2-13. A DC track circuit.

The first DC track circuits with dry cells supply, had low signal levels in order to reduce the wear and number of batteries ([8] page B2). Low signal levels are one reason why they were not immune to disturbance. Modern DC track circuits are supplied from the public grid via rectifiers.

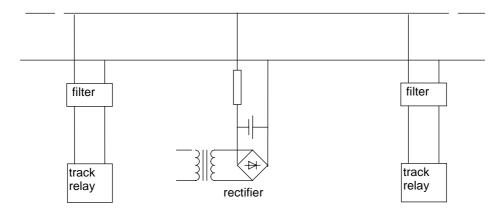

**Figure 2-14.** A DC track circuit in areas with high geomagnetic currents.

The Swedish National Railway Administration ("Banverket") uses DC track circuits on the main lines. Batteries are integrated as a UPS-supply. Track circuits longer than 200 m have relays at both ends as protection against heavy geomagnetic currents ([2] page 128), see figure 2-14.

DC track circuits are only well suited in combination with AC supply. However as the AC supply itself can energise the track circuit relay, it can also be a source of interference, see figure 2-15 and figure 2-16.

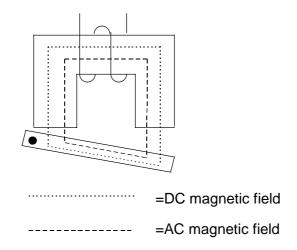

**Figure 2-15.** *Normal DC track relay action.*

**Figure 2-16.** An AC-immunised DC track relay.

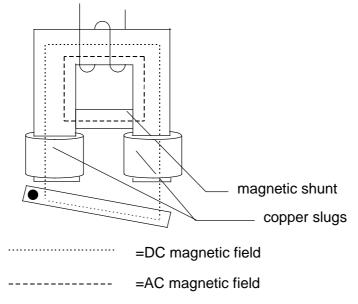

To immunise the DC track circuit, the magnetic circuit is changed. A magnetic shunt and two copper rings, "slugs", are put in the iron core. As an AC magnetic flux tries to penetrate the copper rings, a current is induced in them

and they become quite impermeable to the AC magnetic flux, which instead will pass the magnetic shunt. Only the DC magnetic flux can penetrate the rings and trip the track relay. ([1] page 194), see figure 2-16.

Important interference sources for DC track circuits are asymmetric commutations in the line converter, transformer inrush and pantograph-catenary arcing, which cause saturation in the main transformer. All three sources generate DC components, with duration long enough to trip the track circuit, [24] and [25].

Buried metal objects in the vicinity of the track can together with the soil form simple galvanic cells, which can cause corrosion to the object. To avoid this a cathodic protection system with opposite potential must normally be applied to the object. An earth current from the protection system can flow via the rails and interfere with the DC track circuit ([8] page B8). Also reinforced concrete sleepers can form a galvanic cell. The voltage is not high enough to compete with short circuiting wheel axles, but can keep a disconnected DC track circuit energised for several minutes ([8] page B10). These examples show the problem with low DC track circuit signals, and the solution is that the track should be isolated from ground, or if it has to be grounded, it shall only be grounded at one point within each track circuit.

### **Double element vane relay AC track circuits.**

Initially, AC supplied track circuits were developed for use in DC supplied lines. They were fed from the public mains 50 Hz. However, with another frequency, for instance 83.3 Hz, AC track circuits can also be used on lines supplied with 50 Hz or  $16^2/3$  Hz. 83.3 Hz track circuits can also be used on DC supplied tracks if the DC supply contains too much 50 Hz harmonics, due to rectifier components asymmetries or if there is a high amount of 50 Hz vagabonding current.

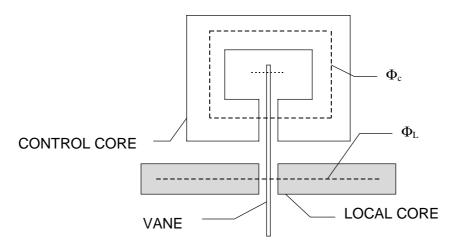

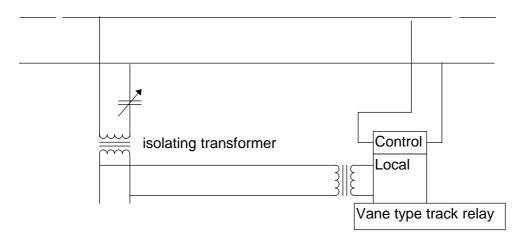

In the double element vane relay a contact is closed when the vane is turned. The torque, needed to move the vane, is produced by eddy currents induced in the vane by the fluxes from two signals, called "local" and "control". The phase shift between these signals shall be 90 degrees. If the two signal frequencies are unequal the torque will have a beat frequency and the relay will not operate. The relay will therefore only respond correctly to "control" current of the same frequency as the "local" current, and with the correct phase shift. The local signal voltage is typically 110 VAC, the control signal only 1-3 VAC. ([7] page 4). The electromagnetic amplifying action of the double element vane relay is both elegant and fail-safe. See figure 2-17 ([1] page 202-207).

Special measures are necessary in 50 Hz traction areas to prevent the supply to the local coil of the relay being disturbed by 50 Hz current. The "local" supply for relays can demand specified relay rooms, can be screened or can use 50 Hz earth leakage current detection equipment.

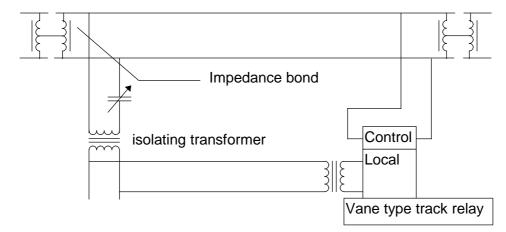

**Figure 2-17.** A double element vane relay AC track circuits.

The control signal shall be connected to the running rail via a capacitor or an inductor in order to get the 90 degrees phase shift, see figure 2-18.

**Figure 2-18.** *Single rail double element vane relay track circuit.*

The capacitor is preferred in order to avoid transformer saturation due to DC current. The capacitor must be of an adjustable type in order to get the correct phase shift with varying rail and ballast impedance.

In double rail double element vane relay track circuit systems, adjacent track circuits are connected with impedance bonds, see figure 2-19. The impedance

bond iron core shall have an air gap to avoid saturation when a DCsupply traction current is not equally distributed between the two rails. Otherwise the impedance bond will act as a short circuit between the rails.

**Figure 2-19.** Double rail double element vane relay track circuit with impedance bonds.

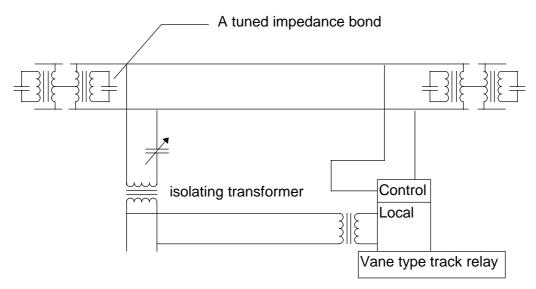

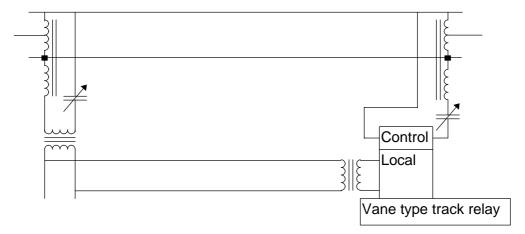

**Figure 2-20.** A tuned impedance bond.

The impedance characteristics of the track circuit can be improved by tuning the impedance bond. With a capacitor connected in parallel to the impedance bond, the impedance between the two rails can be made resistive, and the total impedance can be raised allowing longer track circuits, see figure 2-20.

With an auto coupled impedance bond the track circuit can be fed with higher voltage, and the track sections can be made longer, see figure 2-21.

**Figure 2-21.** A double element vane relay track circuit with auto coupled impedance bond.

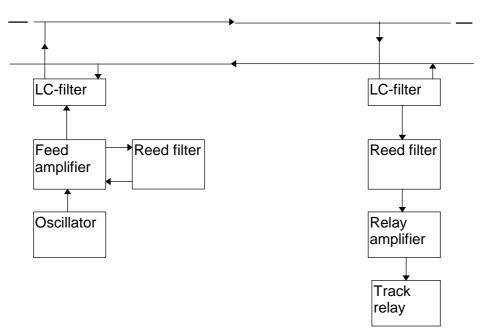

#### **Tuned reed track circuit**

Tuned reed track circuit can be used on both DC and AC supplied tracks and also on non-electric tracks where long track circuits (tunnels for instance) are required. Generally they can be used on the same kind of tracks where double element vane relay track circuits are used, see figure 2-22. ([1] page 213). A reed track circuit is characterised by a pair of mechanically tuned reed filters, one reed filter in the transmitter and one reed filter tuned to the same frequency in the receiver. A coil mechanically excites the reeds, and the reed filter can be tuned to a considerable precision and they have a high Q-value. The transmitter has an oscillator and a feed amplifier, with the reed filter in the feed back loop. The output from the amplifier is fed to the track via a LC-filter. One purpose for the LC filter is to prevent traction surges and other interference from back feeding the transmitter that could cause saturation and/or damage.

The receiver has an LC-filter in series with the reed filter and a relay amplifier, which operates a DC-relay. The reed frequency band can lie as close to each other as 3 Hz. The typical reed frequency bands for 50 Hz traction supply are 363, 366, 369, 372, 375 and 378 Hz ([23]). The use of different frequency band for adjacent track circuits gives freedom from faulty operation due to insulated joint failure. In fact reed track circuits can be used as a jointless track circuit on continuously welded tracks.

Figure 2-22. A tuned reed track circuit.

#### Jointless track circuits.

When continuously welded rails are used, it is impossible to use insulated rail joints. Instead jointless track circuits shall be used, which can be of either voltage or current operated type. They are normally operated in the audio frequency band.

This technique involves an oscillator and amplifier at the feed end. The frequency signal must be filtered and amplified at the receiver end before it can operate the track relay. By the use of suitable fine tuned filters, either electrically or mechanically tuned, crosstalk is avoided. Adjacent and parallel tracks should use different frequencies. ([1] page 215)

In track circuits with insulated rail joints the end of a track circuits is defined by the insulated joint. In jointless track circuits, a short circuit between the two rails will instead act as a definition of the track circuit boundary. This is of course a contradiction. How can a short circuit be used, when the presence of a train is indicated by the short circuiting wheel axles? However if the boundary short circuit is situated a certain distance from the receiver, it is still possible to send enough current through the receiver to make the track relay to pick-up. As long as the short circuiting wheel axles are not too close to the boundary short circuit a train's presence can be indicated. However when the train gets close to the boundary, the wheel axle's short circuit has little impact on the receiver current and the train's presence can not be indicated.

To solve this problem two adjacent track circuits, A and B in figure 2-23, have different frequencies and the track circuits overlap. B's track circuit starts before A's track circuits finishes, i.e., when the wheel axles, still within A's track circuit, are close to A's boundary short circuit, their presence cannot be detected by A's track circuit. Instead its presence will be detected by B's track circuit. The boundary short circuit can not be a real short circuit, instead it is realised as a series LC-filter, tuned to the track circuit frequency, i.e., at the track circuit boundary two such LC-filters are present, one for track circuit A and one for track circuit B. See figure 2-23 where the voltage operated Aster "Type U" track circuit is depicted. This track circuit is a typical example of an audio frequency jointless track circuit ([1] page 219).

**Figure 2-23.** *Aster "Type U" jointless track circuits.*

**Type TI21 Track Circuit** is designed to be used on both AC and DC supplied tracks and also on non electrified lines([9] page B2). It can be used on both jointless and joint track. It is a voltage operated track circuit, similar principle as the Aster 'U' track circuit, but with some improvements. The equipment has great immunity to high values of interference signals. ([2] page 135).

The principle operation of the track circuit is to operate with FSK, "frequency shift key". The audio frequency carrier signal shifts between two frequencies, 34 Hz apart, and the modulation frequency is 4.8 Hz. The reason for two frequencies is to immunise the track circuit against interference. Both signals must have correct modulation frequency and both must be detected by the receiver. Otherwise it is regarded to be an interference and the track side signal turns to red.

The frequency difference 34 Hz is chosen for one reason: If the lower of the two frequencies is interfered by one modulated 50 Hz harmonic, the next higher 50

Hz harmonic shall not be able to interfere with the higher of the two frequencies. The TI21 track circuit system uses 8 different carrier frequencies, each modulated +/-17 Hz. Adjacent track circuits on the same track uses two different carrier frequencies. However also tracks running side by side must use different carrier frequencies due to earth currents. Thus a single track needs two, a double track needs four and four tracks need eight carrier frequencies([9] page B2).

The TI21 transmitter consists of a 4.8 Hz multivibrator, which modulates the carrier frequency oscillator. The modulated signal is amplified and fed to the track via a transformer, for matching and isolation purpose, and a filter. In the TI21 receiver, the signal first passes a transformer. By means of filters, the signal is then split into two parallel branches for each FSK frequency. The signals in the two branches are demodulated to two anti phase square wave signals. Both must be present if the receiver shall pick up. The relay picks up after two seconds, but it drops in a few milliseconds ([9] page B4).

#### HVI (high voltage impulse) track circuits.

HVI track circuits operate with 50 to 100 V amplitude pulses. These track circuits are used on track with low traffic or with old vehicle traffic, where the railhead can have a thin film of rust and/or dirt, which destroys the electrical contact between the rail and the wheels. The voltage peaks are high enough to penetrate the film.

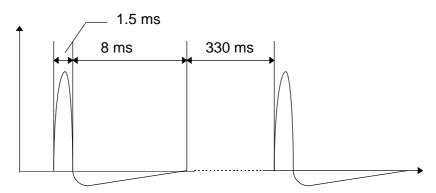

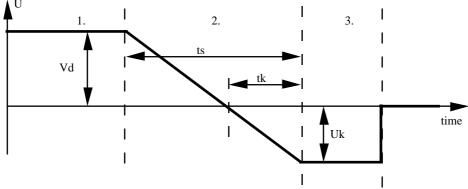

**Figure 2-24.** *The HVI track circuits pulses.*

The pulse is asymmetric where the positive amplitude is seven times the negative amplitude. The duration of the positive peak is 1.5 ms and the duration of the negative pulse is 8 ms. The repetition frequency of the pulses is only 3 Hz ([10] page B2), see figure 2-24.

HVI track circuits are immune to DC since both the transmitter and the receiver are connected to the track via transformers. The receiver is designed to recognise the asymmetric HVI pulse, and therefore it is immune to AC

interference signals that has a symmetric wave form (except under transient conditions) ([10] page B3).

# 2.5 Onboard signalling system for Automatic Train Control system (ATC)

One disadvantage with track side signalling systems is that there is no safety system which handles the problem when the train driver passes a red light signal. Also during stress, the driver can hesitate whether the latest signal he passed was "red" or "green". At traffic jam the speed of the vehicles should be reduced in order to keep the traffic flowing. This can be solved with an ATC (automatic train control) system, which also includes an onboard presentation system where the information is displayed to the driver in the driving cab. Besides when the information is onboard the train it can be used to automatically apply the emergency brake of the train if the drivers fails to act correctly.

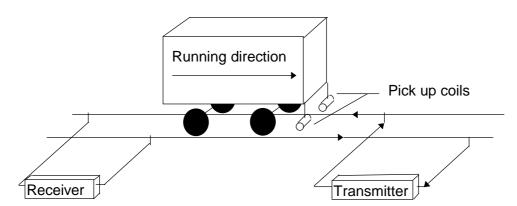

**Figure 2-25.** An ATC system with pickup coils at vehicle front and with the information coded into the track circuit current.

Until now we have regarded the track circuit signal current as being without extra information. However in **low frequency ATC system** the current is coded with information about the maximum allowed train speed, and after being picked up by the train the information can be presented to the driver. Just above each rail at the front end of the train, two pick up coils are mounted, where they pick-up the magnetic field from the track circuit current in the two rails. The output signal from the two coils are differentially connected, and they are therefore only sensitive to the differential mode signal current and insensitive to the common mode traction current, see figure 2-25.

The pick up coils can also pick up interference from other sources. The motor current in the motor cables can be inductively coupled to the coils. If the cables are not routed in symmetry to the coils, e.g. the motor cables can be more close to one of the coil than to the other, the interference from the motor cables will be picked up and the ATC system can be disturbed, see figure 2-26. The most effective solution to this problem is to twist the motor cables and to route them along the vehicle centre axle.

**Figure 2-26.** Inductive interference from motor cables to pick up coils on board the train.

In **audio frequency track circuits ATC system** the amount of information can be increased. The Swedish National Railway Administration, responsible for the main line track system uses a **radio communication ATC**-system which sends information from a micro-wave transmitter between the rails up to an antenna onboard the train. The consequence of the use of such a system is not taken into account in this thesis.

# **3** The Traction System

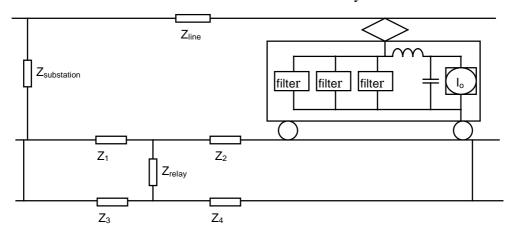

In this chapter, the traction system, depicted in figure 3-1, will be described. Traction is the action of drawing or pulling a vehicle over a surface by motor power. The traction system consists electrically of the substation, of the transmission line and of the vehicle drive system.

Both the DC and AC supplied drive systems, based on three phase induction motors fed from a machine converter will be studied in this work while DC motor trains are excluded. Special attention is paid to the DC supplied drives system, since the variable current spectrum will reach the line directly and interfere with the track circuits of the signalling system. Such a traction system often includes brake chopper phases. This kind of traction system is very common in metro traffic, of which Stockholm "T-bana" (Underground) is one example.

The converter can either use GTO thyristors in combination with snubbers or use snubber-less IGBTs.

**Figure 3-1.** A general traction system

## 3.1 Energy supply

AC supplied lines use either 50 Hz or 162/3 Hz in countries with 50 Hz mains, while in the USA corresponding supply frequencies are 60 Hz or 25 Hz. If the line frequency equals the frequency of the power grid, the supply system is only a transformer, if the line frequency differs from the public mains frequency, the line voltage is either produced in special power plant for traction, or in some kind of a rotating or a static converter. The general problem for AC supply is that on the public three phase side of the supply system the power flow is anticipated to be constant due to a three phase symmetrical load, while on the traction single phase side the active power is pulsating with twice the line

frequency. As the public electric companies normally do not allow this pulsating power the supply systems must be combined with filters. Power semiconductor converters will produce harmonics to the traction side, and those harmonic frequencies must be separate from the signalling system frequencies.

On DC lines the supply system consists of rectifiers. In these system the power flow is constant both on the public side and on the traction side, so the DC supply does not have the same filter problem as the AC supply. One major problem is that 50 Hz track circuits are often used in combination with DC supplied systems. Due to asymmetries in the firing angles of the rectifiers and in the three phase transformers, a large 50 Hz component can be found on the traction side. The asymmetry is especially pronounced when Hg-valve rectifiers are used.

A substation unit can normally supply a limited number of trains. In areas with a lot of traffic a number of such units are used to form a substation. Typical substation power is 10-30 MVA, and a typical locomotive power is 3-4 MW.

## European main line railway electric supply system

The European countries have different railway supply systems and the supply systems at each side of a national border are often not the same. There are some exceptions: Germany, Austria and Switzerland form one group with 15 kV 16 2/3 Hz. Sweden and Norway form another group with the same system. But Denmark, located between Sweden and Germany, has a different system. France and UK have the same system as Denmark, 25 kV 50 Hz. However this supply system is mainly used on the main lines north of London. South and south-east of London the main lines are supplied with 750 VDC, which makes direct train traffic from France to London difficult.

The different supply systems are not the only reason why it is difficult for a train to cross a border. The supply system can be the same on both sides of a border, but the signalling systems with their track circuits are different. As an example: France has built a TGV train ("train de grand vitesse") which can cross a number of borders in central and western Europe, but the train became very expensive. However there are high ambitions within the European community to harmonise the railway traffic ([6] page 275).

In table 3-1 the different supply systems on main lines are presented.

| System | Voltage        | Country                                                   |

|--------|----------------|-----------------------------------------------------------|

| AC     | 25 kV 50 Hz    | UK, France, Finland, Denmark, Luxembourg, Portugal, Spain |

| AC     | 15 kV 162/3 Hz | Germany, Austria, Switzerland, Sweden, Norway             |

| DC     | 3 kV           | Belgium, Spain, Italy, Poland                             |

| DC     | 1.5 kV         | France, Netherlands                                       |

*Table 3-1.* Different main lines railway supply system in Europe ([6] page 276).

## DC railway traction power supply

UK

750 V

DC

This supply started to be used, mainly in the USA at the end of the last century. The voltage was 500-700 VDC, but at the beginning of this century systems with 1200 VDC started to be used ([11] page 582). The original advantage of DC supply was its simplicity to operate DC series motors, by means of series resistor control, in combination with switching from series to parallel connection during acceleration, all equipment mounted on board the vehicle. 3 kV supply systems is dating from 1920s and 1930s and are used on main lines. 1.5 kV is normally used on regional and interurban traffic with up to typically 100 km distance between feeding substations, but also some main lines use this voltage. Urban metros and trams use 600 V and 750 V, but mainlines in England are also electrified with this voltage.

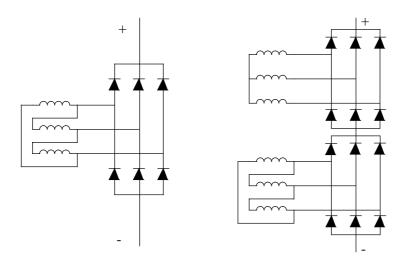

**Figure 3-2.** *Six pulse and twelve pulse rectifier.*

The DC voltage is fed from a converter which rectifies the three phase voltage of the mains, normally with a six pulse or a twelve pulse rectifier, into DC. Circuit diagrams for different rectifiers are depicted in figure 3-2.

By means of (3.1) the production of the ideal dc side harmonics can be calculated. This expression is not usable for calculation of the non ideal harmonic due to the rectifier imperfections. ([6] page 277):

$$v = \frac{pV_{\text{max}}\sin(\frac{\pi}{p})}{\pi(m^2p^2 - 1)\sqrt{2}} \cdot \left[ \left\{ 1 - \cos(\gamma)\exp(jm\gamma) \right\} - jm \cdot \sin(\gamma)\exp(jm\gamma) \right]$$

(3.1)

where:

$\gamma$  is the overlap angle

*m* is the harmonic order.

p is six or twelve

From a 50 Hz six pulse rectifier the 300, 600, 900 Hz etc. harmonics are basically generated, and from a 50 Hz twelve pulse rectifier the 600, 1200, 1800 Hz etc. harmonics are basically generated.

The basic harmonics will also be found on the public three phase side of the rectifier, and can be calculated by means of (3.2) ([6] page 278).

$$i_A = I(\sin(\omega t) - \frac{\sin[(n-1)\omega t]}{n-1} + \frac{\sin[(n+1)\omega t]}{n+1})$$

(3.2)

Almost all multiples of 50 Hz appears in practical operation with slightly asymmetrical three phase supply and asymmetrical firing pulse patterns, and therefore track circuit frequencies are avoided at multiples of 50 Hz, e.g. no reed frequency are used at 400.

## AC railway traction power supply

The disadvantage with DC supply is its rather low voltage which leads to a large line current for a certain vehicle power. The large current leads to high losses and high voltage drop on the supply line. The advantage of AC supply instead of DC is that it is easy to achieve a high voltage by means of a transformer. The high voltage makes it possible to supply main lines over long distances with a reduced number of substations. ([6] page 279). The AC supply became practical when the single phase commutator series motor was constructed, but the problem of commutating a 50 Hz current by the mechanical

commutator, lead to the use of a lower frequency. Initially the supply voltage on the Swedish mainlines was 15 Hz 15 kVAC. The voltage was produced in special power plant. Later on rotating converters, fed from the public mains produced the supply voltage, and then the frequency was changed to 162/3 Hz ([11] page 585). Today power semiconductor converters are more and more coming into operation.

With the introduction of on board rectifiers, especially solid state rectifiers, it was possible to supply traction motors with DC voltage. Later AC electrification has therefore been 50 Hz 25 kV, with start in France after the Second World War. The 50 Hz can easily be supplied to the line via transformers directly from the public grid.

## 3.2 Energy distribution

#### DC line

DC supply lines are only defined by the line resistance when concerning the electrical power distribution. However when also the harmonics distribution is taken into account, the reactance of the line must be included. Normally the line impedance, (= inductance) reduces the line interference, and therefore the line interference is studied at worst case situations, i.e., when the vehicle is located directly at a substation where the supply line length diminishes.

When used for metros, and, if the voltage are below 1 kV, the power is normally distributed via a third rail just along the track, see figure 1-1a. However, for obvious reason, the distribution to trams and street cars is an overhead catenary, see figure 1-1b.

In DC supply the current return is formed by the rails, but the current return can split so a fraction will flow through the earth which can cause some problems, metallic construction in the earth is already mentioned, see DC track circuits in chapter 2.4. The earth current will not be shunted by short circuiting wheel axles, and this earth current can enter the rails again where it can interfere with the track circuit receiver. Also earth current from adjacent tracks can enter the rails and interfere with the track circuit receiver. Harmonics in the earth current can crosstalk and interfere with other signal cables routed in the ballast. For these reasons, as mentioned before, it is highly recommended that the rails are insulated from earth, ([14] page 103). Another solution to this problem is the use of an isolated fourth rail as the current return. This system is used in the London Underground, and an extra advantage with this four rail system is the separation of the signalling current in the running rails from the traction current return.

#### AC line.

AC supply lines normally uses high voltage in order to reduce the power loss, as the current becomes low. Therefore, the resistance of the supply line has a minor interest, it is rather the line inductance that determines the power distribution. The line inductance, together with the substation and vehicle transformer impedance and the line stray capacitance forms a resonance circuits that makes it difficult to predict the frequency behaviour of the line. As the long lines have a large inductance the power factor can be 0.8 as an average. In phase controlled drive systems the power factor is reduced and can be as low as 0.4 at start. The power factor can be a real problem on long single fed lines where the reactive power reduces the feeding voltage at the vehicle. The introduction of phase controlled drive system has also increased the generation of AC lines harmonics.

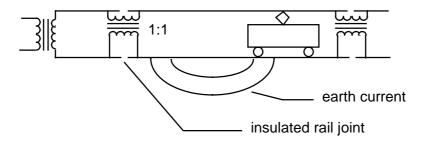

The simplest and least capital intensive way of connecting the supply to the line is to connect one end of the transformer secondary winding to the catenary and the other to the rail, see figure 3-3 ([6] page 281).

**Figure 3-3.** *Simple feeding.*

The disadvantage of this connection is that a major fraction of the return current will be through the earth. The earth current will crosstalk to other signal cables in the track bed, and it can also interfere with the track circuits as described in the DC line part above. Besides, the overhead catenary will, together with the current return in the rails, form a big loop that will act as a transmitter of radio frequency interference.

The problems of crosstalk with telephone lines became obvious from the start of AC railway electrification, and different attempts have been used to control the current return path.

The situation can be improved by connecting a return conductor in parallel with the running rails ([6] page 281).

With the installation of booster transformers with unity ratio, see figure 3-4, less current return will spread to earth and a larger fraction of the current will

remain in the rail ([15] page 107). This arrangement reduces both cross talk and emissions. It can also solve the problem of carrying the traction current over an insulated rail joint, see figure 2-1 and figure 2-13.

**Figure 3-4.** AC supply with a booster transformer for reduction of the earth current.

However as the current still is in the rail, it can disturb the telephone lines. Also the loop antenna is still rather big. Both these effects will further be reduced when booster transformers are used to pick-up the return current from the rails to a conductor installed close to the top of the masts, see figure 3-5. As the distance between the overhead power line and the current return now is small the line impedance is reduced ([13] page 92, [15] page 107).

**Figure 3-5.** *AC* supply with a booster transformer in combination with a mast top current return cable for further reduction of the earth current.

The same advantage as with the booster transformer in combination with the mast top current return conductor can be achieved with an auto transformer, see figure 3-6. With this arrangement the line inductance is further decreased and the voltage drop along the line is reduced, which allows higher power to be distributed at a long distance from the substations. Also the spacing between substations can be increased. "Malmbanan" in the northern part of Sweden uses auto transformer distribution.

**Figure 3-6.** Auto transformer feeding for further reduction of the line inductance.

In AC system, the distance between substation is normally much longer than in DC systems. This will together with line inductance result in high rail potentials, and therefore the rails must be earthed ([12] page 89, [13] page 92). With the use of booster or auto transformers the earth current problems, as described in the DC system, are reduced as the earth current is reduced. However earth current from adjacent tracks or other installation can still interfere with the track circuits. So, care must be taken if the rails must be earthed at more than one position per track circuit.

## 3.3 The three phase AC motor drive systems.

The first attempt with three phase induction motors goes back to 1920s. At the turn of the 20th century some tracks in Germany, Italy, Switzerland and USA were built for trains with three phase induction motor drives. The power was either supplied with three overhead catenaries, or with two overhead catenaries and the running rails as the third phase. The speed and torque control were achieved with pole changing and with resistors in series with the rotor.

The main problem was the supply of three-phase motors from DC or from a single-phase AC. Kando in Hungary built a drive system with slip ring induction motor fed from a rotary phase converter, ([5] page 143). During the 1970s the development of high-power thyristors led to three phase drives mainly based on current source converters, which soon was replaced by voltage source converters in combination with high-power gate turn off (GTO) thyristors. In 1976 the first voltage source inverter drives system was tested in a locomotive (DB 120). The voltage source converter is now established as the standard traction approach. The latest development step is to use bipolar or

insulated gate bipolar transistors (IGBT) as the standard component in low and medium power drive systems. The three phase induction motor has the following advantages ([5] page 143):

- High maximum speed

- Robustness and reliability with low maintenance requirement

- Simple cooling arrangement with enclosed frames

- High uniform torque with inherent overload management

- High power/weight ratio

- Low cost/power ratio

- High voltage operation

- Inherent regenerative braking capability

- Steep torque-speed characteristics

- Parallel connection feasible

From a traction point of view these advantages make a drive system based on three phase AC motors very good. From a signalling point of view there is a big disadvantage, the motor must be fed from a variable voltage, variable frequency machine converter. As the frequency is allowed to vary over a wide range the converter will produce variable frequency line interference in the DC supply and in the AC supply with finite DC-link capacitor, i.e. also including critical frequencies.

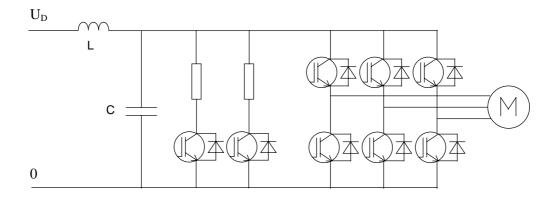

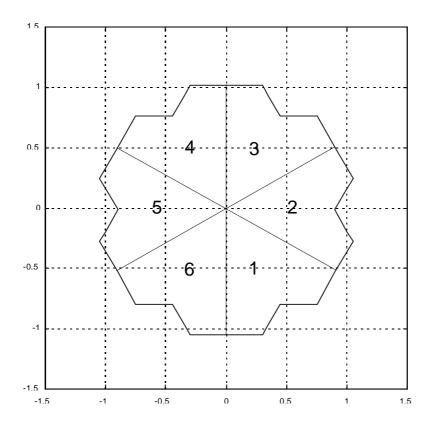

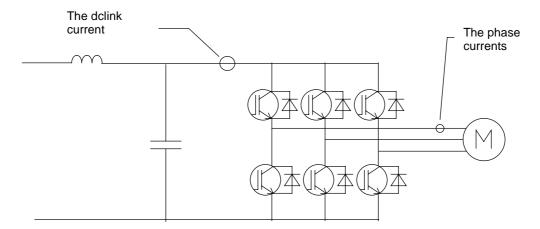

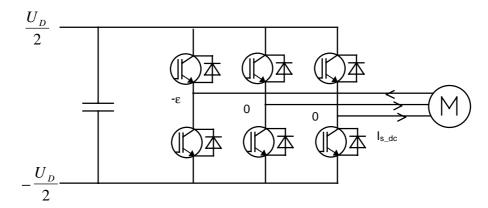

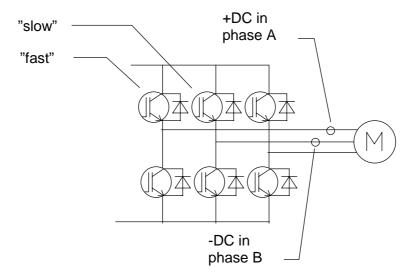

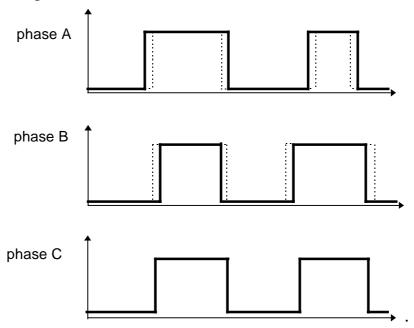

A modern machine converter consists of three phase branches. Often brake chopper branches are connected in parallel with the DC-link, see figure 3-7.

**Figure 3-7.** A three-phase machine converter with a two-phase brake chopper, used in DC supplied drive systems. The converter switching elements are IGBTs.

Two transistor/diode pairs forms a phase leg, where the semiconductor switches either connect the DC-link high voltage or the DC-link low voltage to the motor phase winding. The converter consists of three such phase legs. When power-transistors are used, the diode is normally integrated in the same module. When the upper position in a phase is conducting, a positive current will go through the upper transistor. When the modulation pattern to the phase is changed to lower position, a positive current commutes to the lower diode. In a corresponding way, a negative current will flow through the upper diode and commutes over to the lower transistor. The switching sequence is critical, a fast switching gives low switching losses but stresses the semiconductor. At turnoff, the voltage will be high due to *Ldi/dt*. When transistors are used the switching speed can and thus the voltage can be controlled.

When GTO-thyristors are used instead of transistors the turn-off is faster and a snubber capacitor is required in parallel with the thyristor. To reduce the diode current inrush also a snubber inductor is needed..

A well designed induction motor traction drive system will have the base frequency where the machine converter gives its maximum output voltage with nominal DC-link voltage, at about one third of maximum speed. The drive system is designed to have full flux below base frequency, i.e. the motor voltage/stator frequency ratio is kept constant. Above base frequency the field weakening region starts. In the field weakening area, square wave modulation is normally used and the output voltage is kept constant. The maximum output power is also kept constant. The limiting speed for maximum constant power will be above typically two third of maximum speed, where the pull out (break down) torque will limit the power. In 750 VDC and 1500 VDC fed voltage-source-converter traction drives, the DC-link capacitance is connected to the DC line supply via an inductor. The DC-link voltage will therefore vary as the

supply line voltage varies, and when the DC-link voltage is low the field weakening area will start at lower speeds than the base speed.

DC supplied vehicle uses a LC filter, of at least second order, as an input filter to reduce the harmonic generation to the line, but the filter is also used to reduce the harmonics generated by the substation.

## The control system

In normal mode accelerations and retardation, the feedback control system has small influence on the production of harmonics. Therefore relative simple open-loop slip frequency control with current feedback was implemented in early induction motor drive systems, fed from machine converters. The torque was controlled at constant rotor flux by the ratio of slip frequency and rotor resistance. Acceptable steady-state behaviour is obtained with speed and stator current feedback, by calculating the slip frequency and by adding this frequency to motor speed the converter frequency is found. Correction of the motor voltage by the current control loop is sufficient to maintain the flux at the reference value, ([5] page 149).

However this kind of control system is not fast enough in more dynamic control action like slip/slide control, or the control of transient caused by voltage interruptions at pantograph bouncing. A fast and accurate vector control system can prevent the production of torque pulsation and corresponding line interference. A fast control system can be used in active elimination of critical frequencies.

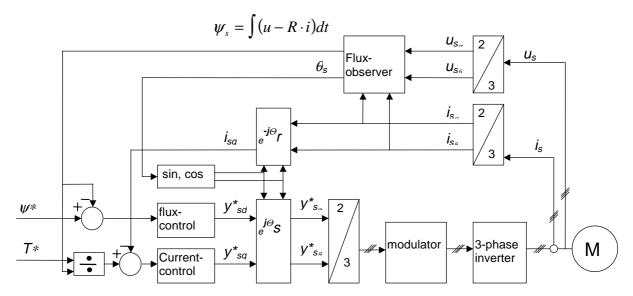

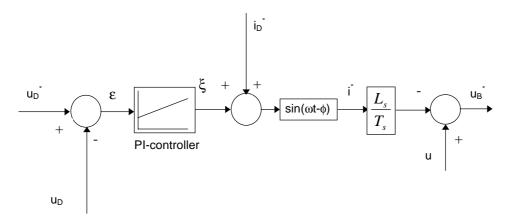

Vector control with pulse-width modulation is now used in most modern induction motor drive systems fed from a machine converters, see figure 3-8. This drive system is today used in all kind of rail vehicles from trams and street cars with limited rating up to big freight locomotives.

A vector control system is usually oriented to either the stator-flux or the rotor-flux linkage vector. The following description is based on a stator flux vector orientation. Since the stator flux cannot economically be measured directly, it has to be calculated based on the measured quantities stator voltage, stator current and rotor speed. There are several ways to perform these calculations, generally referred to as flux observers. In this case, a flux observer reported in ([21], page 38) is used. Both the stator flux estimate, and the stator current are expressed in a reference frame (d,q) oriented to the stator flux linkage vector estimate.

The three phase voltages and the three phase currents are measured and expressed as the complex voltage  $(u_{so}, u_{so})$  and the complex current  $(i_{so}, i_{so})$ . The

resistive voltage drop in the stator is calculated and subtracted from the voltages  $u_{s_{\alpha}}$  and  $u_{s_{\beta}}$ , and thereafter the magnitude and the argument of the flux is formed in the flux observer by integration. A new reference frame (d,q) is attached to the stator flux linkage vector, and thus the flux magnitude is identical to the direct component  $\psi_d$ .

The stator flux estimate is compared to the stator flux reference, and the error is fed to a flux controller. The output of the flux controller is the voltage-time area reference for the output voltage along the d-axis of the machine converter during the coming sampling interval.

The torque reference is divided by the modulus of the stator flux linkage vector, resulting in a reference for the torque producing stator current component. By means of the angle  $\theta_s$  the current components  $i_{s_{\alpha}}$  and  $i_{s_{\beta}}$  can be transformed to the quadrature current component. This current reference is then compared to the measured equivalent and the error is fed to a PI current controller, calculating the reference for the output voltage along the q-axis of the machine converter during the coming sampling interval.

The direct and the quadrature component of the voltage-time area are by means of the angle  $\theta_s$  transformed to the  $\alpha,\beta$ -frame, which after 2/3 transformation forms the desired three phase voltage-time area references.

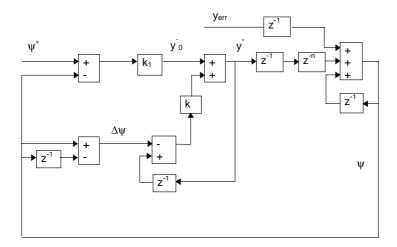

**Figure 3-8**. *Induction motor torque control based on stator flux*

The following seven equations form the control algorithm ([19] page 3-75):

Torque control:

$$i_{sq}^{*}(k) = \frac{T^{*}(k)}{\psi_{sd}(k)} \tag{3.3}$$

where  $T^*(k)$  is the torque reference and  $\psi_{sd}(k)$  is the stator d-axis flux approximately, with the same amplitude as the air-gap flux amplitude.

Flux control:

$$y_{sd}^{*}(k) = R_{s} \cdot i_{sd}(k) \cdot T_{s} + \left[ \psi_{sd}(k+1) - \psi_{sd}(k) \right] =$$

$$= \left\{ \psi_{s}^{*}(k) = \psi_{sd}(k+1), i_{sd0} \approx \frac{\psi_{s}}{L_{s}} \right\} =$$

$$= \frac{R_{s}}{L_{s}} \cdot T_{s} \cdot \psi_{s} + \left( \psi_{s}^{*}(k) - \psi_{s}(k) \right) =$$

$$= \left\{ \psi_{s} = \sum_{0}^{k-1} \psi_{s}^{*}(k) - \psi_{s}(k) \right\} =$$

$$= \frac{R_{s}}{L_{s}} \cdot T_{s} \cdot \sum_{s=0}^{k-1} \left[ \psi_{s}^{*}(n) - \psi_{s}(n) \right] + \left[ \psi_{s}^{*}(k) - \psi_{s}(k) \right]$$

(3.4)

where  $y_{sd}^*$  is the direct component of the voltage-time area reference.

#### Current control:

$$y_{sq}^{*}(k) = \left(R_{s} + \frac{L_{s}}{\tau_{r}}\right) \cdot \sum_{0}^{k-1} \left[i_{sq}^{*}(n) - i_{sq}(n)\right] \cdot T_{s} + \left[\sigma \cdot L_{s} + \frac{\left(R_{s} + \frac{L_{s}}{\tau_{r}}\right) \cdot T_{s}}{2}\right] \cdot \left[i_{sq}^{*}(k) - i_{sq}(k)\right] + \omega_{r}(k) \cdot \psi_{sd}(k) \cdot T_{s}$$

$$(3.5)$$

where  $y_{sq}^{*}$  is the quadruple component of the voltage-time area reference.

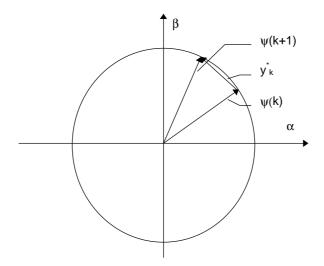

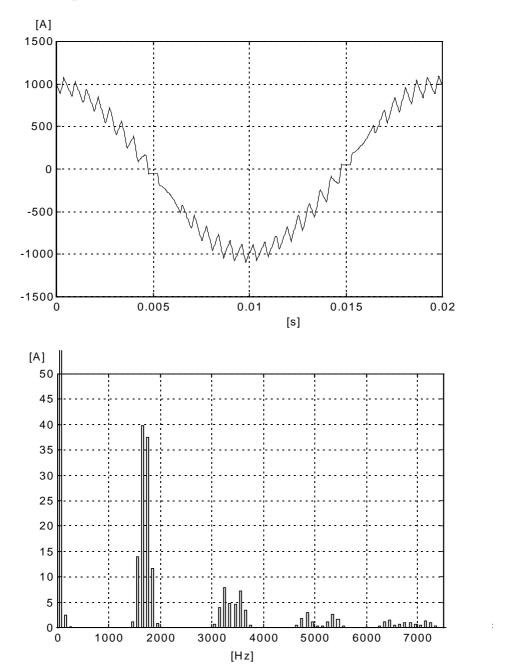

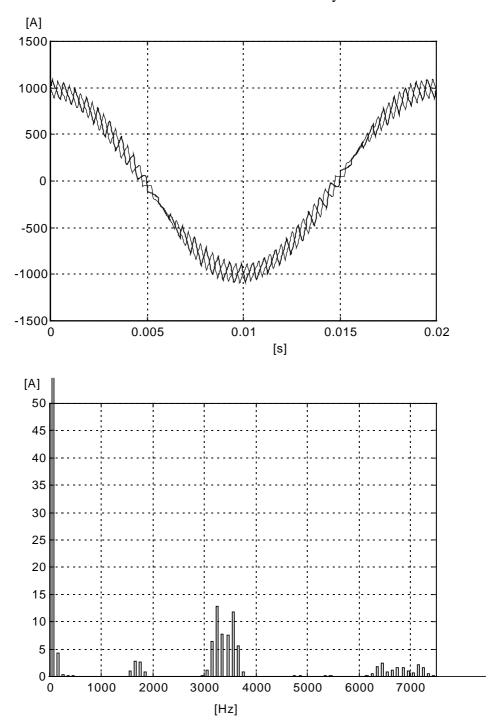

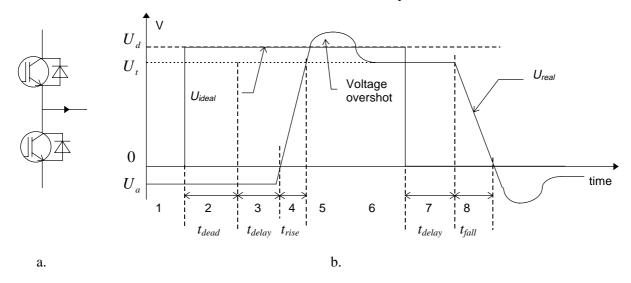

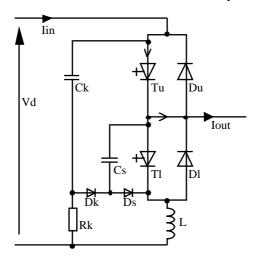

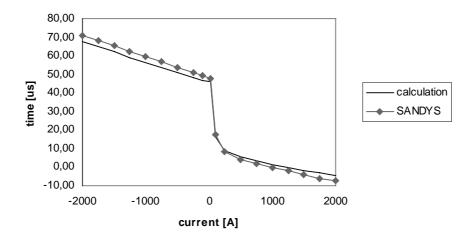

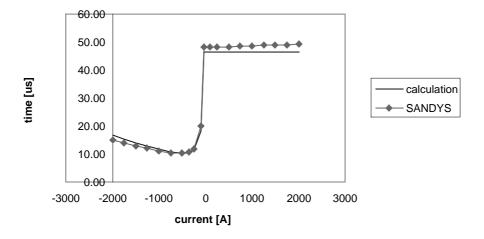

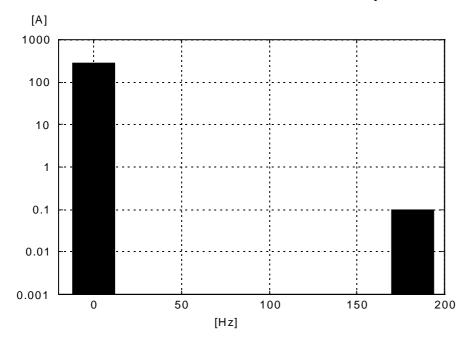

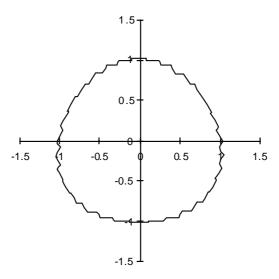

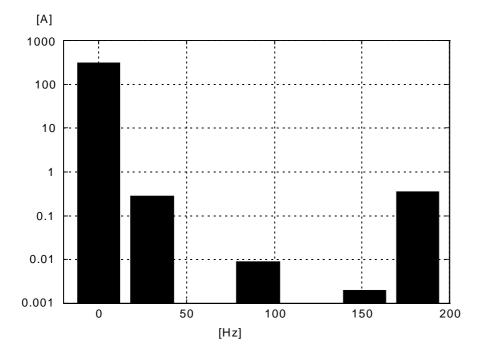

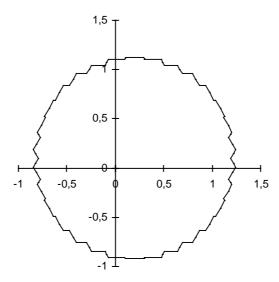

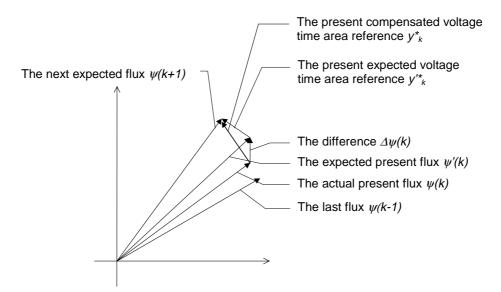

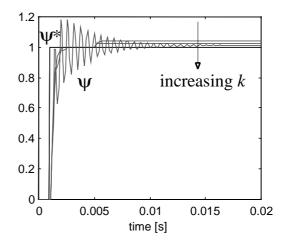

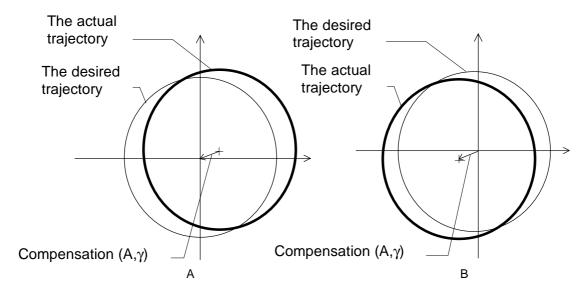

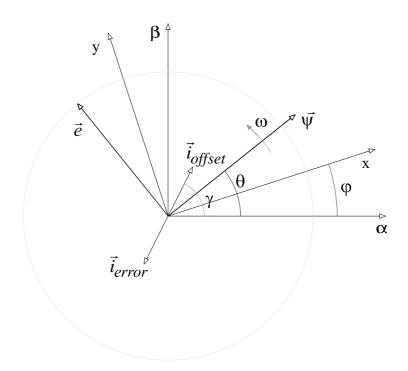

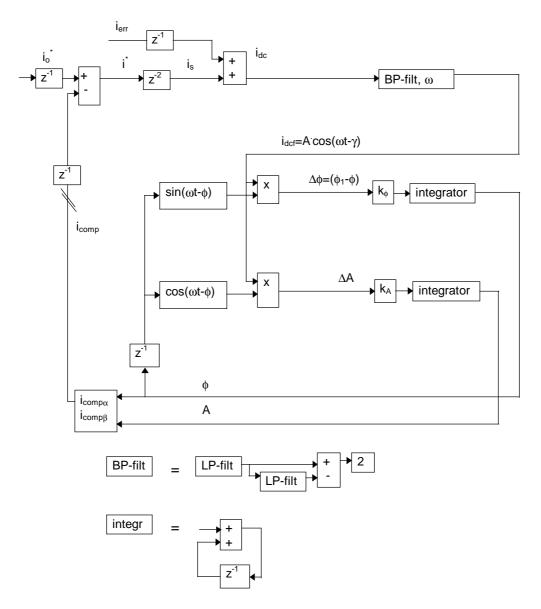

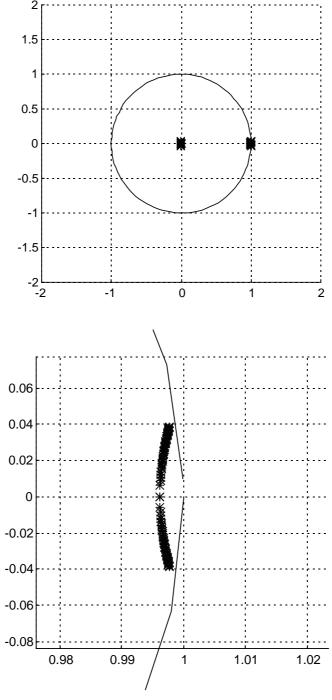

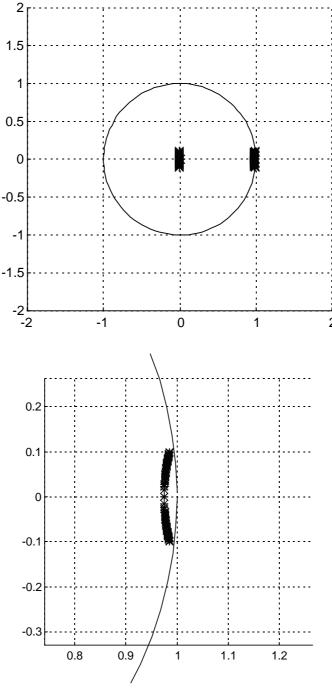

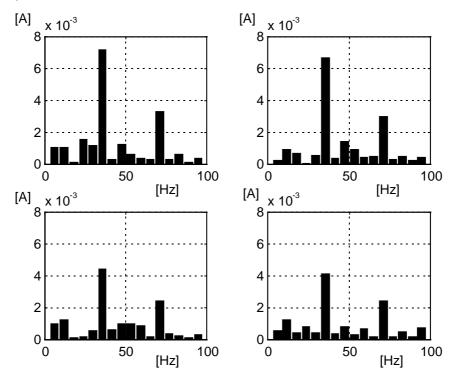

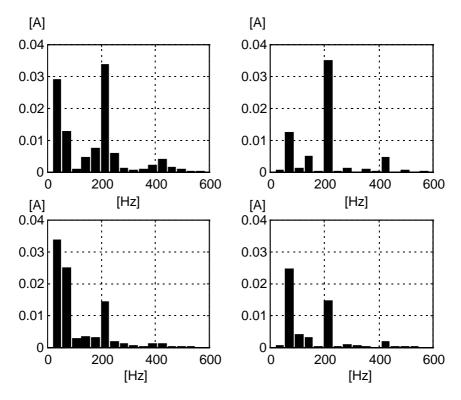

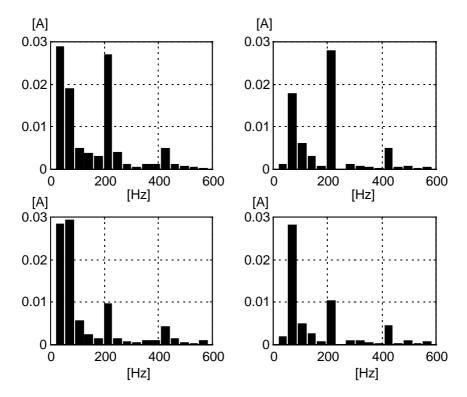

**Figure 3-9.** The integral of the terminal voltage, i.e. the terminal flux,  $\psi(k)$ , will grow to  $\psi(k+1)$  with the vector y(k) during the time between the sampling instants k and k+1.