# A Silicon Carbide Inverter for a Hybrid Vehicle Application

# **Oscar Haraldsson**

# **Martin Andersson**

Dept. of Industrial Electrical Engineering and Automation Lund University

## **Abstract**

This master thesis investigates how silicon carbide (SiC) bipolar junction transistors (BJT) can improve the power inverter in a hybrid car. Today's power electronics in a hybrid car needs a cooling system separated from the main cooling system. A separated cooling system increases the cost. The idea is to replace silicon transistors with silicon carbide transistors which can withstand higher temperatures. To study a complete three-phase inverter a PSpice model of a SiC BJT is built. The SiC BJT is provided from the company TranSiC that is developing a SiC transistor called BitSiC. The BitSiC model is used to simulate an inverter for a 5 kW electric machine (EM). The EM is intended for a Belt driven Alternator Starter (BAS) in a hybrid car of medium size. The SiC semiconductors has several interesting advantages compared to Si based semiconductors:

- SiC can withstand high temperatures, up to 600°C.

- Higher thermal conductivity, lowering the junction to case thermal resistance.

- Positive temperature coefficient, easier to parallel.

- Faster and less reverse recovery, reducing switching losses

Through simulation this master shows that silicon carbide transistors can use the exiting cooling system of a car. With the SiC BJT low switching losses and low conduction voltage the efficiency reaches values of 98%.

Keywords: Silicon Carbide, SiC, Bipolar Junction Transistor, BJT, Inverter, Hybrid Car, BAS, PSpice.

# **Preface**

Although the master thesis did not turn out as planed, it could not have turned out any better. Through hard work and wise guidance it was possible to simulate and evaluate a three-phase inverter based on silicon carbide (SiC) transistors. This master thesis was formed when professor Mats Alaküla (Professor, IEA), Bo Hammarlund (CEO, TranSiC) and Lars Hoffman (Project Manager, Saab Automobile AB) recognized the potential of SiC components in a hybrid car. The first plan was to build an inverter with SiC components. But as often when working with cutting edge technology it is necessary to adapt the goals to what is possible. Instead of building an inverter PSpice models of TranSiC's SiC transistors is built. This led to a simulation of a 5 kW inverter with SiC transistors.

It has been a joy to work on our master thesis and with the people at the department of Industrial Electrical Engineering and Automation (IEA) at Lund Institute of Technology. We would especially like to thank Mats Alaküla that has inspired and guided us through the entire project. We also would like to thank Bo Hammarlund, Martin Domeij (CTO, TranSiC) and Lars Hoffman for their support.

Last but not least we would like to thank Gunnar Lindstedt (Assoc Prof., IEA), Hans Bängtsson (guest lecturer), Getacew Darge (Research Eng., IEA), Thomas Bergh (Tech. Lic., IEA), Dan Hagstedt (PhD student, IEA), Jonas Johansson (PhD student, IEA) and the rest of the people at IEA. Thanks for the hospitality, we have been well received and felt us like one in the staff at IEA, we especially appreciate all the cakes that has been given to us.

Thanks to our families for all the support and encouraging our studies trough all the years.

| Lund             | March 2007       |

|------------------|------------------|

| Oscar Haraldsson | Martin Andersson |

|                  |                  |

# **Contents**

| 1.  | Introduction.                                                                                                                                                                                          | 4                                            |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 2.  | The BitSiC 2.1. Silicon carbide 2.2. The silicon carbide transistor structure 2.3. The SiC market                                                                                                      | 5<br>5<br>5<br>7                             |

| 3.  | Path of simulation and design 3.1. Steps of the simulation path                                                                                                                                        | 8<br>10                                      |

| 4.  | Simulation of expected EM-size 4.1. Car model 4.1.1. BAS car model 4.2. Driving cycles 4.3. Simulation. 4.4. Conclusion 4.5. Choice of working point 4.6. Improvements                                 | 14<br>14<br>15<br>15<br>17<br>20<br>20<br>20 |

| 5.  | Transistor test rig                                                                                                                                                                                    | 21                                           |

| 6.  | Choice of simulation program 6.1. Bipolar Junction Transistor (BJT) model 6.2. The use of the test rig 6.3. The IEEE document. 6.4. The final model 6.5. Uncertainty of measured data 6.6. Conclusions | 23<br>23<br>24<br>26<br>28<br>30<br>30       |

| 7.  | Three-phase simulation                                                                                                                                                                                 | 31                                           |

| 8.  | Post processing of PSpice simulation 8.1. Interfacing MATLAB with PSpice 8.2. Efficiency Calculations 8.2.1. Efficiency improvements                                                                   | 36<br>36<br>39<br>42                         |

| 9.  | Thermal calculations 9.1. Calculating the maximum thermal heatsink resistance 9.2. Calculate the junction temperature                                                                                  | 46<br>47<br>48                               |

| 10. | Conclusions                                                                                                                                                                                            | 50                                           |

| 11. | Future work                                                                                                                                                                                            | 51                                           |

| 12. References                                          | 52  |

|---------------------------------------------------------|-----|

| 13. Appendix A- Simulink2Pspice.m                       | 54  |

| 14. Appendix B - Tektronix2Pspice.m                     | 56  |

| 15. Appendix C – Pspice2Matlab.m                        | 58  |

| 16. Appendix D1 The test rig.                           | 61  |

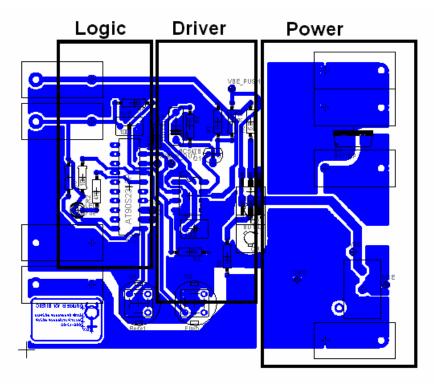

| 16.1. phase 1 – design study                            | 61  |

| 16.2. Phase 2 – testing the ideas                       | 63  |

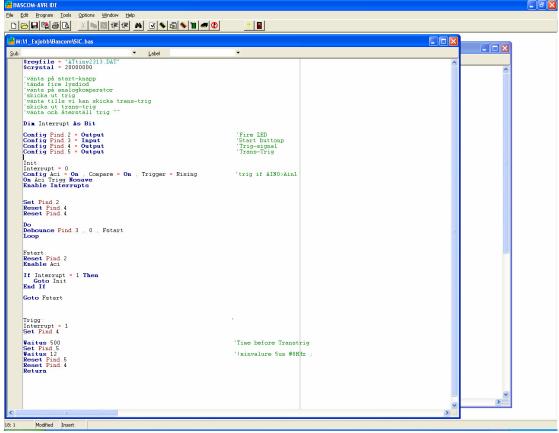

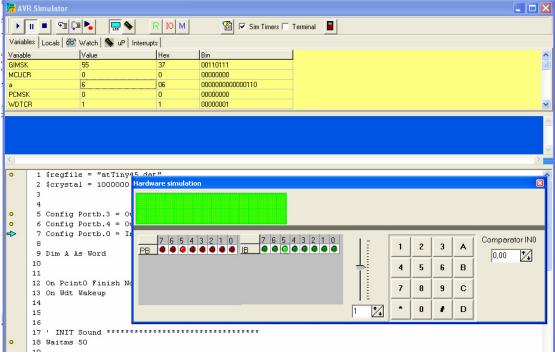

| 16.2.1. Microcontroller                                 | 64  |

| 16.2.2. Push-Pull                                       | 68  |

| 16.2.3. Comparator                                      | 71  |

| 16.2.4. The Baker clamp                                 | 72  |

| 16.2.5. Soft switching versus hard switching            | 73  |

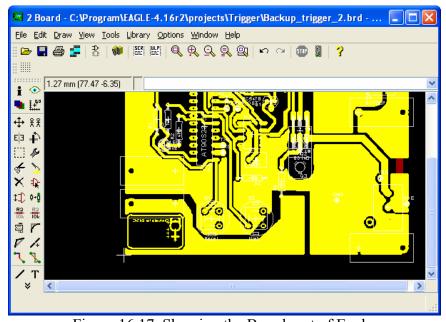

| 16.3. Phase 3 – Building the test rig                   | 74  |

| 16.3.1. Building the PCB                                | 76  |

| 17. Appendix D2 - The full BASCOM code                  | 82  |

| 18. Appendix E - BJT parameters                         | 83  |

| 19. Appendix F Theory of modelling components in PSpice | 85  |

| 19.1.1. Semiconductor diode model                       | 85  |

| 20. Appendix G Measuring model parameters               | 98  |

| 20.1.1. I-V curve                                       | 98  |

| 20.1.2. The Early effect                                | 99  |

| 20.1.3. Bf and Br.                                      | 100 |

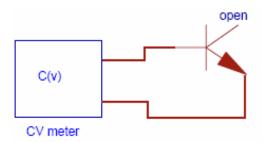

| 20.1.4. Junction capacitance                            | 101 |

| 21. Appendix H - The full three-phase inverter          | 103 |

| 22. Appendix I - Power and efficiency                   | 105 |

## **Abbreviations**

μC Microcontroller

AC Alternating Current

BAS Belt Driven Alternator Starter BJT Bipolar Junction Transistors

CMOS Complementary Metal Oxide Semiconductor

CSDF Common Simulation Data Format

DC Direct Current

DCB Direct Copper Bonded

DIL Dual In-Line

ECE Economic Commission for Europe

EM Electric Machine

EM Electrical Machine

EMF Electromotive Force

EMI Electromagnetic Interference EUDC Extra Urban Driving Cycle

Ib Basecurrent

Ic Collectorcurrent

ICE Internal Combustion Engine

IDE Integrated Development Environment

IEEE Institute of Electrical and Electronics Engineers

IGBT Insulated Gate Bipolar Transistor

LED Light Emitting Diode

MB Megabyte

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MVEG Motor Vehicles Emissions Group

PCB Printed Circuit Board

PWL Piece-Wise Linear

PWM Pulse Width Modulation

RISC Reduced Instruction Set Computer Rthch Thermal resistance case heatsink

Rthha Thermal resistance heatsink to ambient Rthjc Thermal resistance junction to case

sat Saturation

SCC Switched Current Controller

Si Silicon

SiC Silicon Carbide

TUT Transistor Under Test

UDC Urban Driving Cycle

Vbe Base-Emitter Voltage

Vce Colector-Emmiter Voltage

VSTIM Controlled voltage source in PSpice

## 1. Introduction.

This master thesis is planed to result in an inverter for a light hybrid vehicle. The inverters main component is silicon carbide (SiC) based power bipolar junction transistors (BJT). The advantage with silicon carbide semiconductors is that it has a larger bandgap, and it can withstand very high temperatures. In the vehicle industry this is especially interesting because it makes it possible to place the power electronics in the engine bay. In the engine bay the temperature can easily reach 120 degrees Celsius. With ordinary silicon semiconductors it is a problem to cool the electronics because the silicon cannot handle higher temperatures. With power electronics that can withstand higher temperatures one does not have to have a separate cooling system, which saves cost.

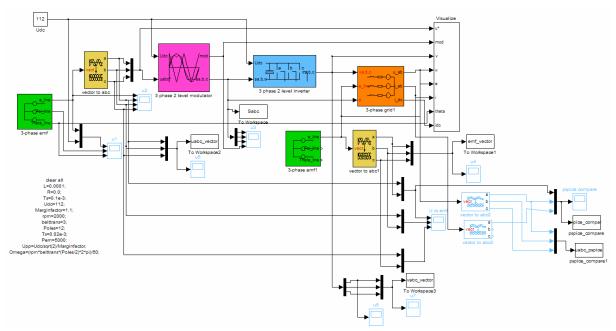

First the size of the Electrical Machine (EM) is determined. The EM is intended for a belt driven alternator starter (BAS). This EM will give both propulsion and act as a generator and starter for then internal combustion engine (ICE). The size of the EM will give the corresponding power ratings needed for the inverter. The optimal EM-size is obtained by different simulations with a hybrid car-Simulink program developed at IEA.

Due to a lack of SiC transistors the goal is to examine a SiC transistor and build a PSpice BJT model of it. With this model a complete three-phase inverter is simulated in PSpice.

Building the model of the transistor is rather difficult. The idea is to take a transistor model that have similar behaviour and "tweak" it to the behaviour of a SiC transistor. A test rig is built. With the test rig a single switching can be done which gives the behaviour of the transistor. During the construction of the test rig many different types of driver-circuits is tried out.

With a working model switching signals for the control of the inverter is needed. In the car-Simulink program the maximum load of the EM-size is simulated, and thus giving us the working speed of the EM. With another Simulink program a three-phase inverter is simulated which gives us the control signals for different types of switching.

Simulating a whole driving cycle takes to long time because of the calculations of transients in each switching. With the chosen working point the switching parameters and back electromotive force (EMF) with the initial load current is extracted from the Simulink program. With all these signals and parameters one fundamental period of the EM is simulated in PSpice with a reasonable time and accuracy.

The next step is to design a complete three-phase inverter, the work is started with the same type of drive circuit that is used in the test rig. Now complete simulations are done with different switching frequencies. When a simulation is done the efficiency of the converter is calculated to see how much power that is needed to be cooled away by the cooling system.

## 2. The BitSiC

The BitSiC is a silicon carbide (SiC) bipolar junction transistor from the company TranSiC [1]. This means that instead of using a doped silicon (Si) wafer the BitSiC is made out of doped SiC wafer. SiC have its pros and cons.

#### 2.1. Silicon carbide

One advantage with SiC is that it has about three times wider bandgap than Si. With a wider bandgap the electrons need higher activation energy to jump to the conduction band. Higher activation energy means that SiC devices can operate in a stable way at higher temperatures (over 200°C) with low leakage currents. Another advantage with SiC is that the electric breakdown field is about ten times higher than for Si and SiC can therefore withstand ten times higher electric fields than Si before breakdown. This advantage can be used in two ways, either is the SiC BJT made with a thinner and more highly doped collector region compared to a Si BJT or else it can be kept as the same size as the Si BJT. If the SiC BJT is made thinner it can withstand the same the electric fields as the regular Si BJT. A result of the thinner SiC BJT is that its turn-on and turn-off is made much faster as well as the on resistance becomes much lower. If the regular Si thickness is kept the SiC BJT will withstand much more electric field than the Si BJT [2].

#### 2.2. The silicon carbide transistor structure

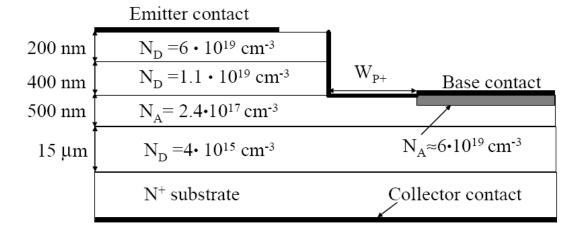

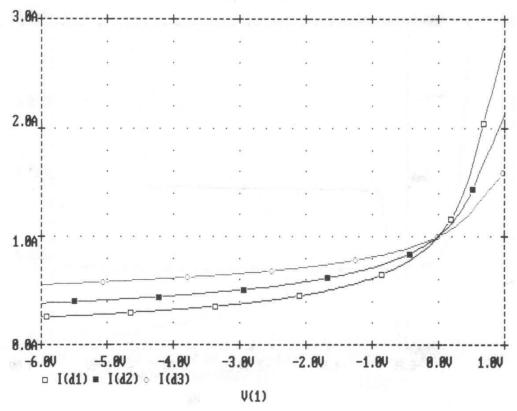

The SiC bipolar transistor (BitSiC) developed at TranSiC is made with epitaxial 4H-SiC wafers. The SiC BJT is built up with different doped layers as shown in figure 2.1.

Figure 2.1 A cross section of the BitSiC [3]

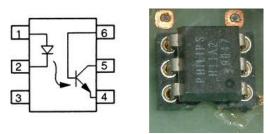

During this project two samples of the BitSiC transistor is examined. The first BitSiC (referred in this thesis as BitSiC1) has a TO-247 package as can be seen in figure 2.2.

Figure 2.2 BitSiC1 in a TO247 capsule.

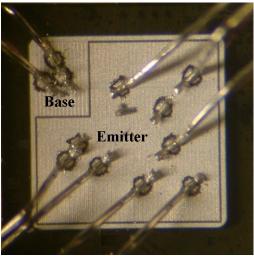

BitSiC1 have problems with contact resistances, this result in a rather low gain and power capability. The BitSiC1 is used to develop the test rig. When TranSiC have produced an updated version of the BitSiC, we were given a sample. The second sample of the BitSiC (referred in this thesis as BitSiC2) has an open capsule with a direct copper bonded (DCB) substrate (figure 2.3).

Figure 2.3 BitSiC2 magnified with bonding wires. The collector is glued with silver epoxy on the other side to the DCB substrate.

#### 2.3. The SiC market

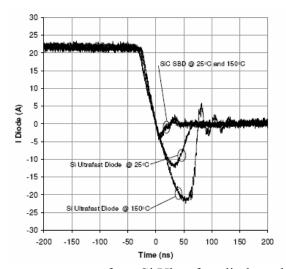

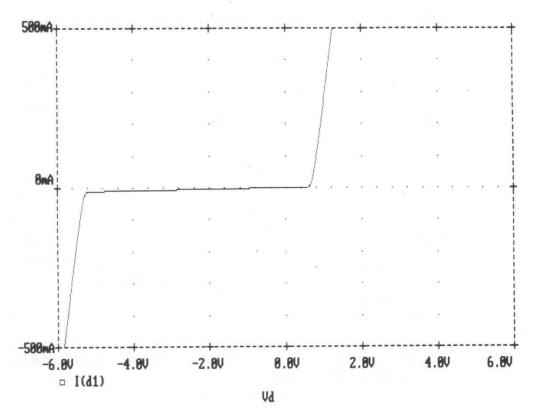

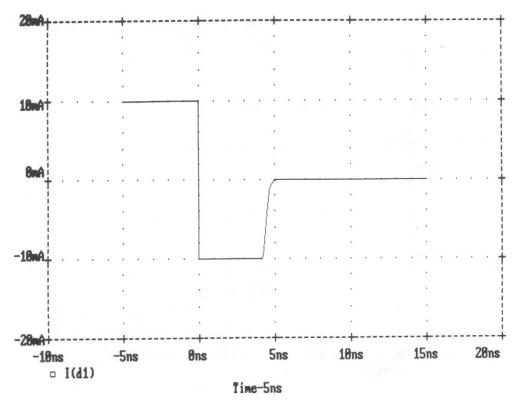

Currently there is no company that sells SiC transistors although there are a lot of researches being done. One example is the BitSiC that the company TranSiC is planning to start selling in the near future. However there are other SiC devices on the market. Currently two companies has released a SiC diode family, Infineon[4] and Cree[5]. Cree has released their Zero Recovery Rectifiers SiC family which include SiC diodes in three voltage ranges 10-20 A @300 V, 1-20 A @ 600 V and 5-20 A @ 1200 V. Zero Recovery refers to that a SiC diode has almost no reverse recovery due to the low capacitance. How this affect the switch and reverse recovery is seen in the figure 2.4. The figure is taken from an application note from Cree [6]

Figure 2.4 Reverse recovery current for a Si Ultra fast diode and a SiC Schottky diode @ 25 °C and 150 °C.

In the oscilloscope illustration one can see that the SiC Schottky diode has almost no reverse recovery. Neither does the SiC diode show any temperature dependence.

# 3. Path of simulation and design

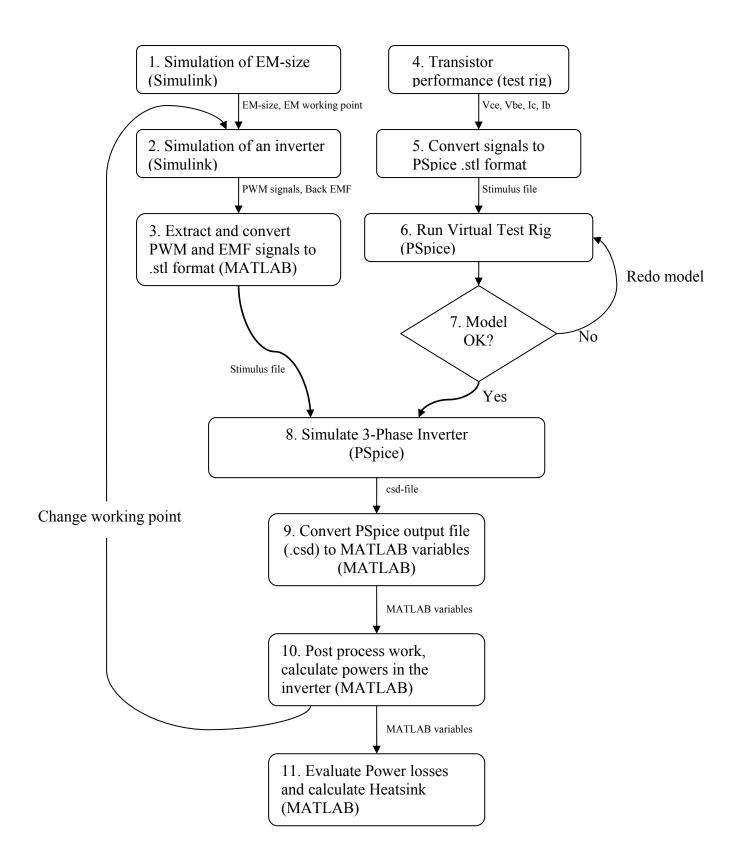

A 5 kW inverter will require allot of components that there is no possibility to get hold of due to the low current production. This led to a new heading of the master thesis. This shifts the focus to simulating a 5 kW inverter, leading to a whole new array of questions and problems. The biggest problem is that there is no working model of the SiC BJT, so a spice model has to be built. The master thesis is expanding to a complex working path. Working with the full span from building a model, to simulating a three-phase inverter. This means that every thing from laboratory work i.e. building the test rig to simulating in several simulation programs has to be done. Because of this complex working path it is decided to write this chapter to help the reader to see the big picture. In figure 3.1 one can see the path used to produce the simulation result of this master thesis.

Figure 3.1 Path of simulation and design.

#### 3.1. Steps of the simulation path

- 1. In the first step the optimal size for the electrical machine (EM) in a light hybrid car is simulated. To simulate a light hybrid vehicle a Simulink model developed at IEA is used. The simulation is simulating a parallel hybrid that can drive certain standard driving cycles. By monitoring the fuel consumption for different configurations an optimal size for the EM is given. The EM size in conjunction with the battery voltage gives the current rating for the three-phase inverter.

- 2. In the second step a simulated three-phase inverter with ideal switching is simulated in Simulink. The purpose of this simulation is to extract the pulse width modulation (PWM) signals and the back EMF of the EM. These control signals is later transferred to PSpice to control the "real" three-phase inverter. The back EMF is also extracted and transferred to PSpice to be implemented in the model of the electrical machine. In short the values of the battery voltage, modulation type and motor parameters are given to the Simulink program. In return the simulation is simulating the PWM signals and the back EMF for the electrical machine.

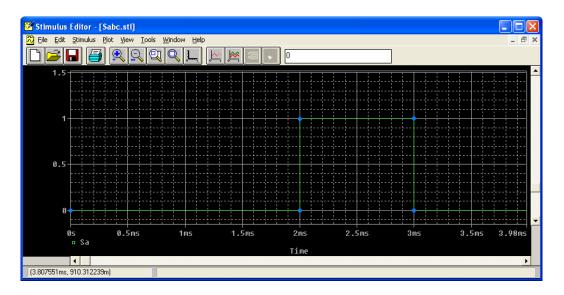

- 3. In PSpice there is a part named VSTIM. VSTIM is a voltage source that takes stl files as input. The purpose of VSTIM is to give the PSpice user a tool for creating user defined voltage sources. These voltage sources is used as a bridge from MATLAB to PSpice. The stl file format look something like the following:

```

.STIMULUS Sa PWL

+ TIME_SCALE_FACTOR = 1

+ VALUE_SCALE_FACTOR = 1

+ ( 0, 0 )

+ ( 0.002 , 0.000 )

+ (+0.000000001, 1.000 )

+ (+0.001 , 1.000 )

+ (+0.000000001, 0.000 )

```

From the STIM-file one can read out that the signal name is Sa and that it is a piece-wise linear (PWL) signal. The voltages are written in the following format + (time in seconds, voltage). The column of numbers will give a voltage signal as in figure 3.2.

Figure 3.2 A view of the VSTIM signal "Sa" in the Stimulus editor (data points marked out).

The first data point is (0, 0). This data point will give 0 V at time 0. Next line (0.002, 0) will also give 0 V but at time 0.002 i.e. 2 ms. The time in this example is in absolute values, However as much freedom as possible is needed. For example the exact back EMF time is needed to be trimmed to fit the simulation. Because of this the signal is formatted with differential time steps. (+0.000000001, 1.000), indicated with a plus sign in front of the time signal. This means that the time is not an absolute time but the time is relative to the previous time step. In this case the voltage signal is making a voltage step at 2 ms from 0 V to 1 V. The time +0.0000000001 will give a rise time of 1 ns. In the same manor will the next line (+0.001, 1.000) give a 1 V plateau with the length of 1 ms. This is the way that both the PWM-signal and the back EMF signal is built. A MATLAB m-file (Simulink2Pspice.m) that autonomously constructs the .stl files from MATLAB variables is written, see appendix A.

- 4. To be able to simulate a fully functional three-phase inverter with SiC BJT's it is needed to make PSpice models of the SiC BJT from TranSiC named BitSiC. To get a working and a realistic model of the BitSiC the performance and behaviour is extracted from a real transistors. These tests are made in a test rig. The test rig switches the transistor under test (TUT) and captures the voltages on an oscilloscope. When the transistor is switched the following signals are interesting: Vce, Vb voltages and the Ic, Ib current.

- 5. The captured signals are extracted from the oscilloscope with WaveStar [7], a program from Tektronix. The easiest way of extracting oscilloscope signals is to copy the signals from WaveStar and place them in a text document. The signals in the text document consist of two columns per signal. One time column with

the absolute time relative the trigger point and one column with the voltage values. This text document is then imported to MATLAB and (Tektronix2Pspice.m) converted to .stl files for PSpice, see appendix B for the complete m-file.

- 6. In this step a model of the test rig is simulated in PSpice. The real signals Vce, Ic, Vbe and Ib from step 5 are imported in to PSpice. In this way it is possible to evaluate the simulated switching versus the real switching. The process of modifying a BJT model to the BitSiC is a mixture of brute force and changing many of the parameters to get a feeling for what all the model parameters do.

- 7. When the model is changed the test rig is simulated. If the simulated switch does not match the real signals the model is changed a bit more. This process is looped allot of times until the BitSiC model matches the real signals. Cautions are advised when editing the model. The BJT is modelled as a stiff system. This means that there are several processes in work in different time scopes. On one side there is the dynamic properties i.e. switching behaviour and on the other side there is the DC-behaviour that for example sets the Vce (sat) voltage that slowly changes over time. All this is controlled with the same parameters.

- 8. When the model is satisfying it can be used in a more complex circuit. In this step the construction of the whole three-phase inverter with all the PWM-signals and back EMF is implemented. This also involves optimizing the drive circuit making sure it works as it is supposed to.

- 9. With a working three-phase inverter the simulation can store all the data in a "Common Simulation Data Format" (CSDF/CSD) file. When a PSpice simulation is calculated the solution data is saved with a time line in the .csd-file. This file tends to get massive and is saved in a sporadic format. This complicates the process of reading the file. MATLAB has no built in function for reading .csd-files so an m-file is written for this purpose. If the simulation is run for one fundamental period (1.6 ms) and saves the data in a .csd-file the file size will be in the reign of 1 Gigabyte (GB). This size of data file will kill even the best laboratory computer so a compromise is made. Only the most important signals such as power in the transistors and in the diodes etc are saved. With only the most important signals stored (approximately 26) the file size of the data file ends up in the region of 20 Megabyte (MB). This simulation file is red by our m-script (PSpice2Matlab.m) and converted to MATLAB variables. See Appendix C for the entire m-script.

- 10. When the PSpice signals is imported to MATLAB it is time for post processing work. By integrating the instantaneous power signals from i.e. a transistor the average power consumption for that transistor is calculated. With the total power consumption and power losses the efficiency can be calculated. This gives a pointer of how well the inverter works. If a different working point for the motor or a different modulation wants to be investigated the processes is repeated from step 2.

11. When all the simulation is done with a satisfying result the master thesis moves in to answer the core question. Is it possible to make an integrated belt driven alternator starter (BAS) that is cooled with a standard water cooling system with help of SiC technology? This question is answered with the help of calculating power looses and the heat sinks required.

# 4. Simulation of expected EM-size

The first Simulink studies are done to get an idea of an appropriate size of the Electrical Machine (EM). Knowing the size of the EM sets the power rating that the DC-AC inverter should be able to handle. By simulating a car under different conditions it is possible to estimate how much energy that is needed to drive a certain cycle. With the simulation it is also possible to determine the working point for the EM. The car model that is used in this thesis is developed in Simulink and uses maps and tables as input parameters. Simulink with its graphical interface and easy overview of complex systems rapidly gives a feedback of how the car model behaves.

#### 4.1. Car model

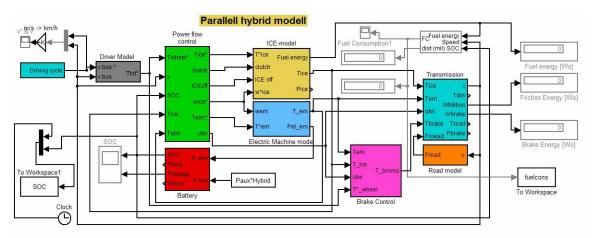

The car model used is a typical medium car like "Opel Astra" with different motor types, diesel or gasoline. The vehicle model [8] was originally developed by Mats Alaküla and Karin Jonasson and later modified by Thomas Bergh and Dan Hagstedt to be more realistic for a belt driven alternator starter (BAS) car model, see figure 4.1.

Figure 4.1 Parallel hybrid model in Simulink.

Technical specifications for the car:

```

Pice max = 79000;

% ICEsize [W]

Mv = 1300;

% Vehicle weight [kg]

rw = 0.30;

% wheel radius [m]

Cd = 0.26;

% air resistance

Cr = 0.007;

% roll resistance

Av = 2.56;

% Front area [m<sup>2</sup>]

% Air density [kg/m³]

rho air = 1.2;

% 180 km/h maximum speed [m/s]

vmax=180/3.6;

```

#### 4.1.1. BAS car model

The BAS is meant to replace the generator and starter in a car and is able to drive the car at low speeds and with zero-emission. When the model is simulated as a "regular" car of today the engine does not stop when the car is in stand still, and the EM does not help the car to get into motion. In BAS-mode the engine stops as soon as the car is at stand still. When the car start to move the EM gets both the engine started and helps the car accelerate. This type of hybrid-model is a light version of a parallel hybrid car. The hope is to create a cheap light hybrid car with little changes in the cars construction but with a significant reduction in fuel consumption.

## 4.2. Driving cycles

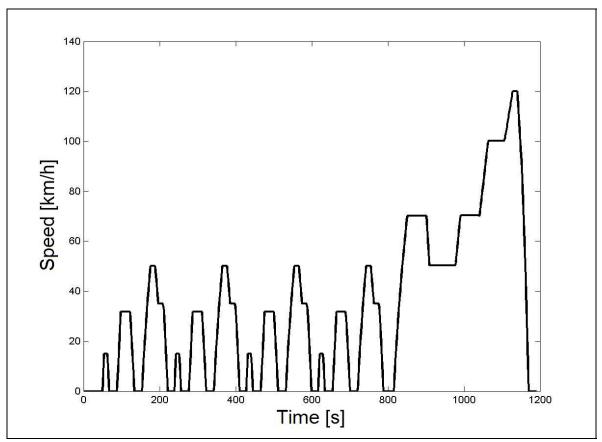

The driver is simulated as a PI-regulator with anti windup giving a simple and repetitive model of a driver. In the simulation different driving cycles is used, European standard ECE+EUDC test cycle and United States standard US06.

The ECE+EUDC also known as the MVEG-A cycle is used by the European light duty vehicle industry for emission certification. The cycle contains four ECE cycles without any interruption and is then followed by one EUDC cycle. The four ECE cycles is also known as the UDC (Urban Driving Cycle) and represents city driving cycles e.g. in Paris or Rome. This type of driving represents low speed, low engine load and low exhaust temperature. The EUDC (Extra Urban Driving Cycle) represents more aggressive and high speed driving modes. The ECE+EUDC-cycle is shown in figure 4.2.

Figure 4.2 The ECE+EUDC velocity cycle model [8].

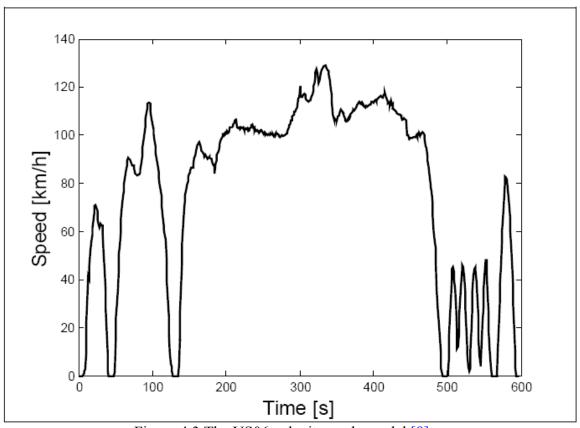

The US06 driving cycle represents highway driving with aggressive accelerations, high speed driving and rapid speed fluctuations giving transient fuel consumption. The US06 is developed because of the lack of aggressive driving in the United States standard FTP-75 cycle. The light duty vehicle industry uses FTP-75 for emission certification in the U.S. The US06 is shown in figure 4.3.

Figure 4.3 The US06 velocity cycle model [8].

#### 4.3. Simulation.

To simulate the appropriate size of the power converter several simulations with different sizes of the EM is done, two types of engines (gasoline and diesel) and two driving cycles (ECE+EUDC and US06). The optimal solution varies with different motor types and different driving cycles.

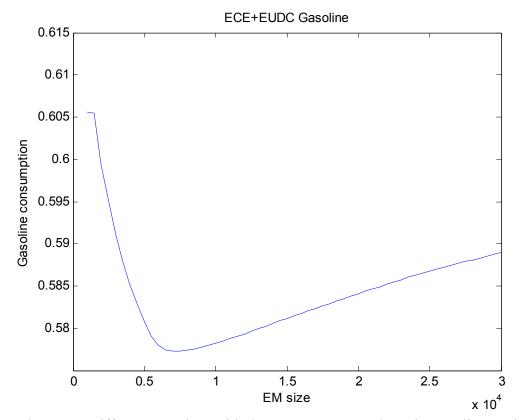

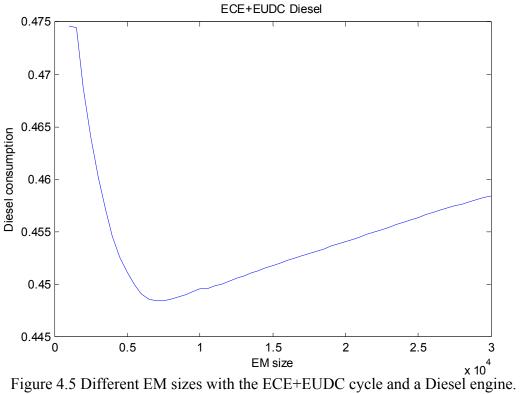

With the European standard driving cycle the optimal BAS-size is around 7 kW for and gasoline engine and around 7.5 kW for a diesel engine see figure 4.4 and figure 4.5.

Figure 4.4 Different EM sizes with the ECE+EUDC cycle and a gasoline engine.

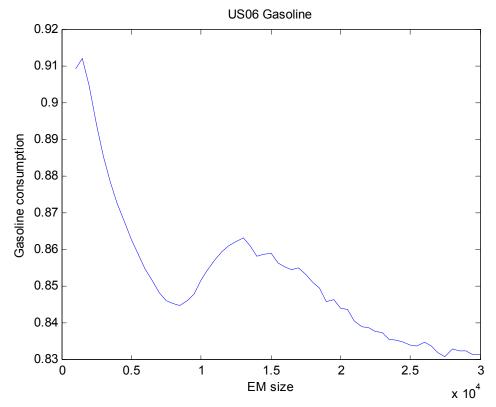

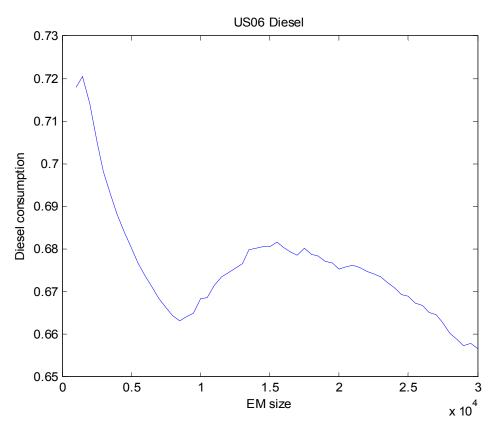

With the United States driving cycle the optimal BAS-size is around 8,5 kW for a gasoline engine and for a diesel engine, see figure 4.6 and 4.7.

Figure 4.6. Different EM sizes with the US06 cycle and a gasoline engine.

Figure 4.7. Different EM sizes with the US06 cycle and a Diesel engine.

#### 4.4. Conclusion

Looking at the diagrams, the saving in fuel consumption is very small when going from an EM of 7-9 kW to a 5 kW EM. We come to the conclusion that an EM of size 5 kW is a good size for the EM. This will give a fair size of the EM as well as low fuel consumption.

## 4.5. Choice of working point

To simulate the inverter the EM-speed is needed. Running the first simulation of the hybrid car in Simulink, the car ran at average engine speed of 2000 rpm. This speed is then converted to the speed of the electrical machine so that the back EMF can be extracted. This together with the chosen PWM frequency gives the inverter's working point.

## 4.6. Improvements

The BAS model is used to get an idea of how the BAS-unit should be designed. There are many uncertain variables in the model that should be checked, for example the battery weight, how the battery should be charged, how the ICE efficiency map reflects a real engine and many more variables.

# 5. Transistor test rig

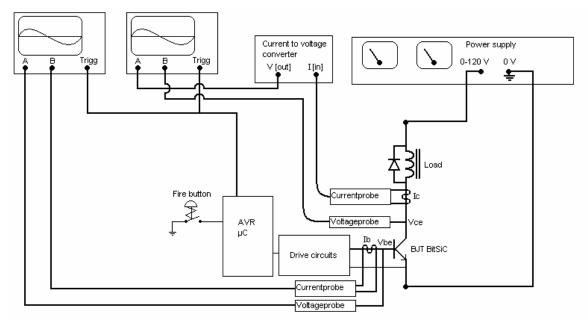

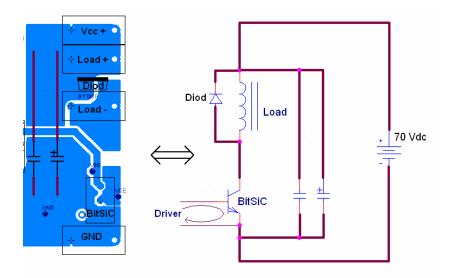

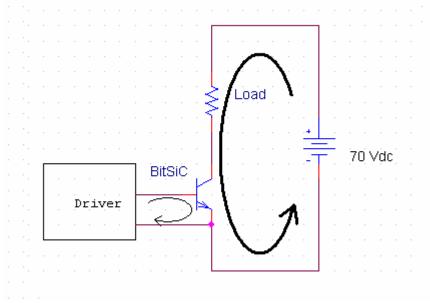

The purpose of this master thesis is to evaluate a new type of transistor (BitSiC). The idea is to test how the transistor will work in a motor driver for a belt driven alternator starter (BAS).

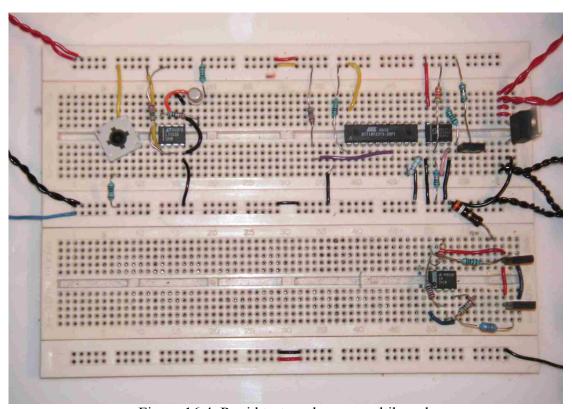

To be able to test the BitSiC transistor a high quality laboratory test rig is needed. The reason for this is to get high quality data and to be able to easily change or modify the drive circuits and the evaluated transistor. When brainstorming ideas for the test rig three main goals are decided.

- 1. The test rig shall control a real transistor at an accurate working environment to see the switching behaviour.

- 2. A high quality circuit is needed to shield the test rig from noise.

- 3. Last but not least a good interface for importing the measured data to a computer for post process in MATLAB and other computer programs is needed.

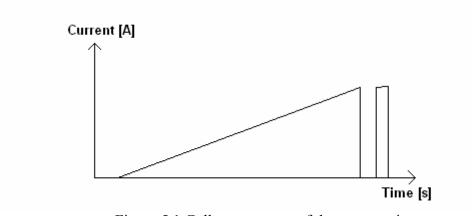

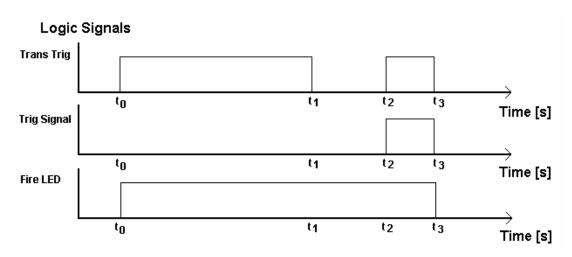

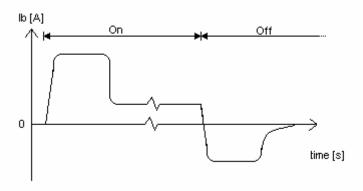

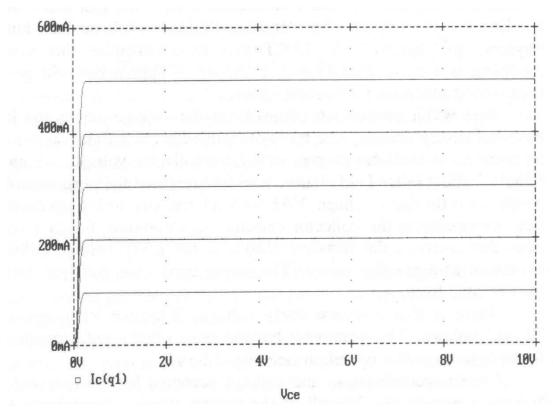

The idea of the test rig is to simulate a working environment for a transistor in a motor drive for BAS i.e. correct currents and load. To do this it is necessary to be able to change the load, voltages and currents in a controlled matter. To simulate the battery of a hybrid car the input to the test rig is made voltage stiff. Instead of a battery a regular power supply and a DC capacitor bank is used. To simulate an electrical machine a stiff current load is used. The test rig uses a big inductor as load, the bigger the better. The ideal is for the test rig to ramp up the current in the BitSiC as seen in figure 5.1.

Figure 5.1 Collector current of the test transistor.

The test rig is able to ramp up the current in the inductor to a specific value specified by the working point that is investigated. Then the test rig makes a switch, i.e. turn on the transistor and turn it off again. This course of events is controlled by an AVR microcontroller ( $\mu$ C). The "switch" i.e. the switching after the ramp is the part that gives useful data. Datasheets of power electronic switches is specified for an inductive load. Since the test rig is using a large inductor (1340 mH) as a load the criteria of an inductive load is fulfilled.

The current ramp can be explained if one studies the equations for an inductor

$$u = L \frac{di}{dt} \cong L \frac{\Delta i}{\Delta t} \Leftrightarrow \frac{u * \Delta t}{L} = \Delta i$$

(5.1)

With a fixed voltage u, and a fixed inductance L, one time step can only increase the current a certain amount. This is the meaning of a current stiff load and is the reason for the current ramp. When the test rig is executing a switch at a specific current e.g. one ampere the test rig ramps up the current to one ampere and then makes the switch. If the switch is fast enough the current through the load will not have time to change because of the current stiffness. This will make sure that the current stays constant at one ampere through the load during the whole switch.

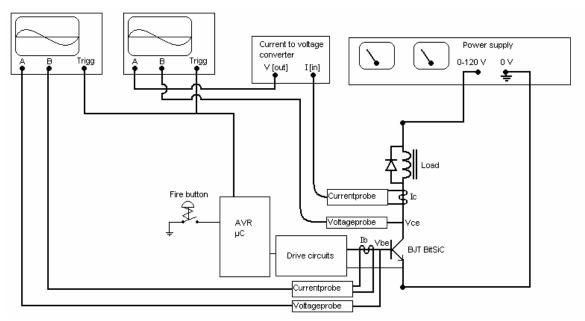

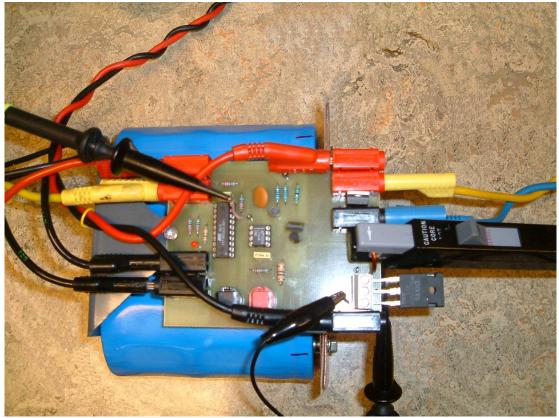

The test rig system is rather complex, the test rig system is shown in figure 5.2.

Figure 5.2 A schematic view of the most important instruments for the test rig.

In centre of the test rig system is an AVR microcontroller ( $\mu$ C). This  $\mu$ C controls the switching of the investigated transistor. When the BitSiC is turned on the current starts flowing in the load. With the help of the load and the free-wheeling diode the BitSiC gets a realistic switching. The switching behaviour of the BitSiC is captured by the oscilloscopes. This captured data is then imported to PSpice were the BJT model is built. To build the model the signals Vce, Ic, Vbe and Ib are captured. The Test rig makes it possible to extract behaviour from the transistor and import it to PSpice to create a model.

A detailed description of the design and outcome for the test rig can be red in appendix D1.

# 6. Choice of simulation program

The Department of Industrial Electrical Engineering and Automation (IEA) uses two programs for simulating electronic designs, the Orcad's PSpice [9] and Linear technology's SwitcherCAD III [10]. There are several other simulation programs, but in the industry the most widely used program is the cadence program suite including PSpice. Many of the programs are using a type of simulator called spice. Spice have a set of commands and certain ways of building different models of components, many of these programs have the same set of commands and models. The program SwitcherCAD III is license free, easy to use and powerful but PSpice have a well developed model editor and is the most used program in the industry. This is why the simulation of the three-phase inverter is done in PSpice.

## 6.1. Bipolar Junction Transistor (BJT) model

The most important BJT parameters [11] are listed below, a full list can be read in appendix E. These have a short description of what they do and some of them are self explaining just by reading the description. The theory for most of the parameters can be red in appendix F. A first attempt is made to measure the different parameters, this can be seen in appendix G.

Table 6.1 Parameter Description.

| IS   | transport acturation ourrent               |  |  |  |

|------|--------------------------------------------|--|--|--|

|      | transport saturation current               |  |  |  |

| BF   | ideal maximum forward beta                 |  |  |  |

| NF   | forward current emission coefficient       |  |  |  |

| VAF  |                                            |  |  |  |

| (VA) | forward Early voltage                      |  |  |  |

| IKF  | corner for forward-beta high-current roll- |  |  |  |

| (IK) | off                                        |  |  |  |

| ISE  | base-emitter leakage saturation current    |  |  |  |

| NE   | base-emitter leakage emission coefficient  |  |  |  |

| BR   | ideal maximum reverse beta                 |  |  |  |

| NR   | reverse current emission coefficient       |  |  |  |

| VAR  |                                            |  |  |  |

| (VB) | reverse Early voltage                      |  |  |  |

| ISC  | base-collector leakage saturation current  |  |  |  |

|      | base-collector leakage emission            |  |  |  |

| pNC  | coefficient                                |  |  |  |

| RB   | zero-bias (maximum) base resistance        |  |  |  |

| IRB  | current at which Rb falls halfway to       |  |  |  |

| RBM  | minimum base resistance                    |  |  |  |

| RE   | emitter ohmic resistance                   |  |  |  |

| RC   | collector ohmic resistance                 |  |  |  |

| CJE  | base-emitter zero-bias p-n capacitance     |  |  |  |

| VJE  |                                          |

|------|------------------------------------------|

| (PE) | base-emitter built-in potential          |

| MJE  |                                          |

| (ME) | base-emitter p-n grading factor          |

| TF   | ideal forward transit time               |

| CJC  | base-collector zero-bias p-n capacitance |

| VJC  |                                          |

| (PC) | base-collector built-in potential        |

| MJC  |                                          |

| (MC) | base-collector p-n grading factor        |

|      | forward and reverse beta temperature     |

| XTB  | coefficient                              |

| XTI  |                                          |

| (PT) | IS temperature effect exponent           |

## 6.2. The use of the test rig

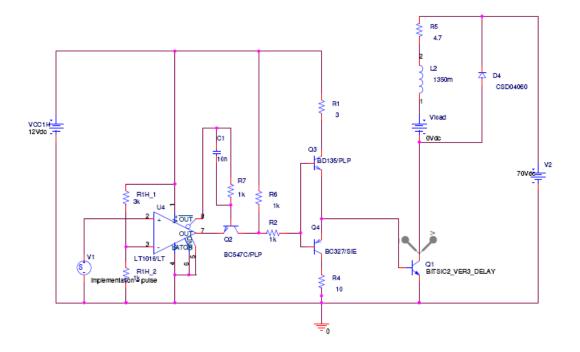

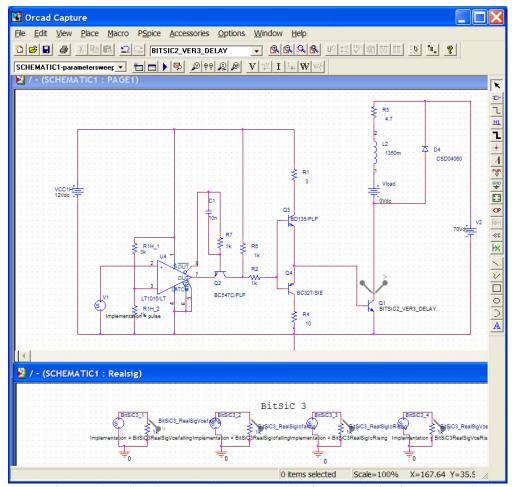

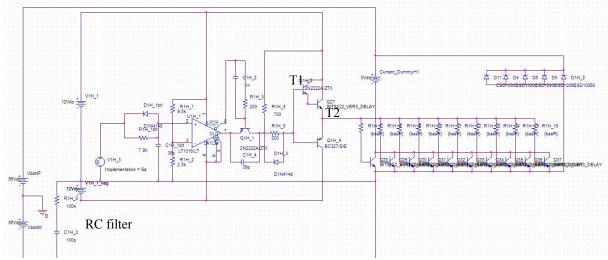

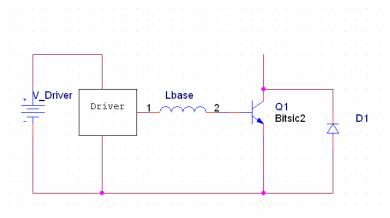

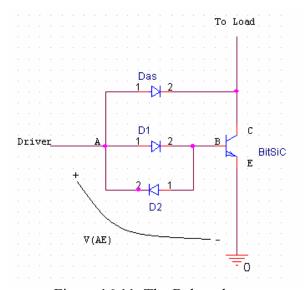

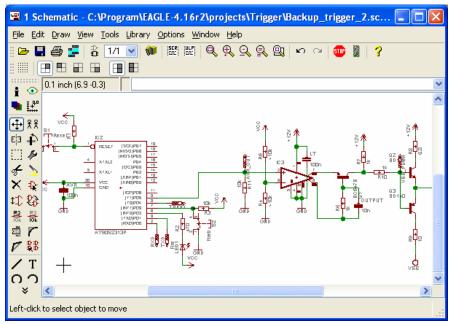

The idea is to use an existing model of a BJT and tweak it to get the desired behaviour. With the test rig it is easy to see the BitSiC switching behaviour. To see the difference between the model behaviour and the measured signal a simulation model of the test rig is built in PSpice, see figure 6.1.

Figure 6.1 Simulated test rig in PSpice.

With both the simulated model behaviour and the measured signal in the same window it is easier to tweak the BJT model. The measured signals are captured with Tektronix WaveStar. WaveStar has different types of data capturing procedures; one can choose between a graphic picture just like the oscilloscope or get a data table. With the data table every signal matrix contains a time vector and a data vector. To get the measured

data into PSpice a working path is created. First one has to copy the matrix in to Microsoft Excel spreadsheet and then save it as a tabular structured text format, see the text structure below.

```

[Tek TDS200 Series].Data.Waveforms.CH 1,,[Tek TDS200

Series].Data.Waveforms.CH 2,,

S, Volts, S, Volts

tidVce, Vce,

tidIc,

-0.000104,

13.3599997,

-0.000104,0.00039999999

-0.0001036,

13.2799997,

-0.0001036,0.00079999998

13.4399996,

-0.0001032, -0.00039999999

-0.0001032,

-0.0001028,

13.1999998,

-0.0001028,

```

The signals in the text document will consist of two columns per signal. One time column with the absolute time relative the trigger signal and one column with the voltage values. This text document is imported to MATLAB and via (Tektronix2Pspice.m) converted to a stimulus (.stl) file for PSpice. The .stl file can be used by the PSpice part VSTIM to create signals and be measured into the PSpice A/D program. A dummy resistor is used in series with the VSTIM, then the signals is measured over the resistor, see figure 6.2.

Figure 6.2 Picture showing the Orcad Capture with the test rig in the upper window, and the voltage sources to create the measured signals in PSpice A/D in the lower.

A search for a similar transistor to "tweak" to the wanted behaviour started. This was proven to be very difficult, starting with the BUX11A it did not give the desired result. After a lot of trail and error with other types of transistors, the idea of getting a working model of the SiC transistor seems unreachable.

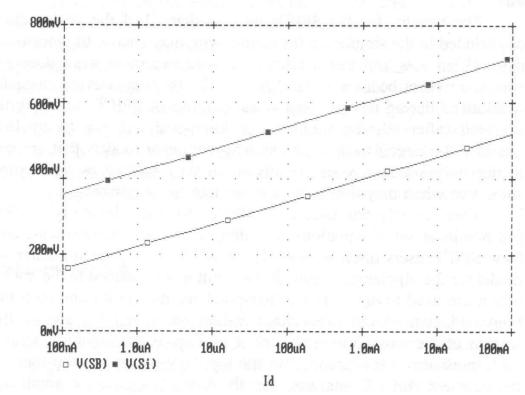

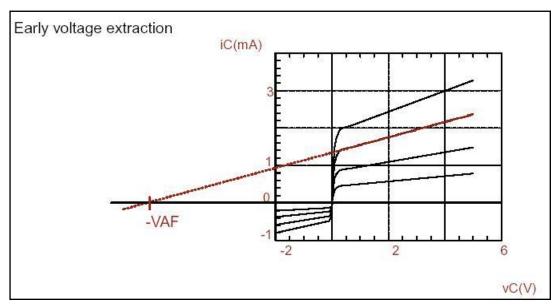

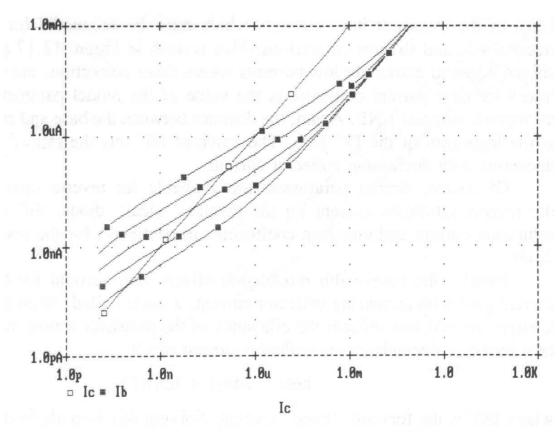

#### 6.3. The IEEE document.

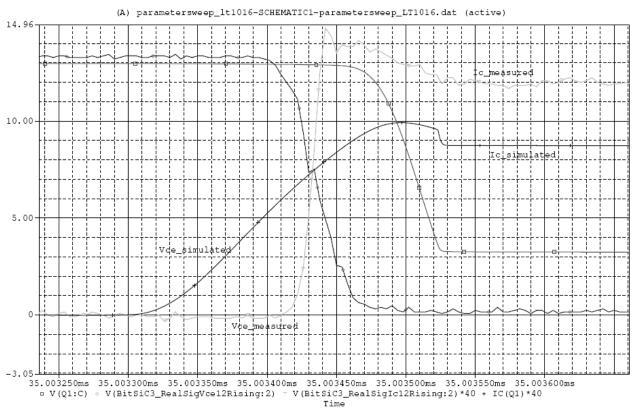

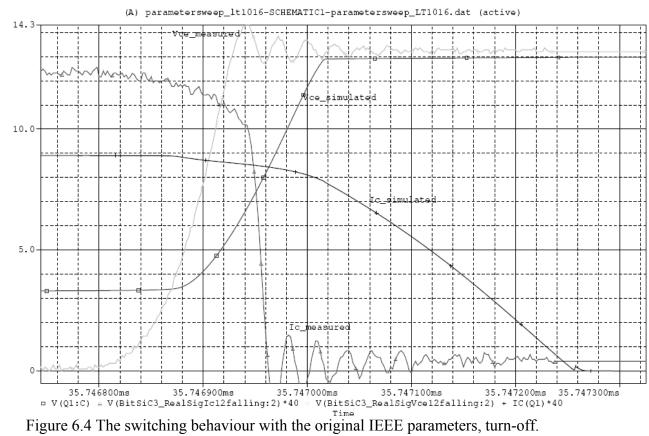

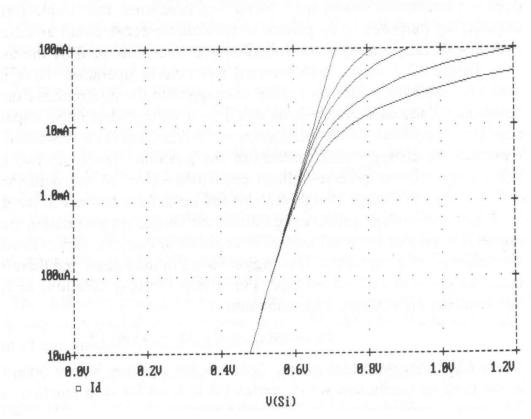

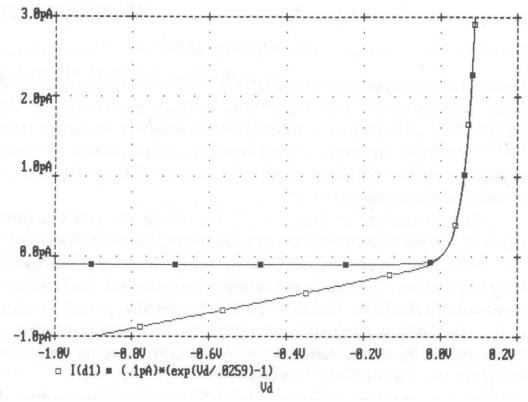

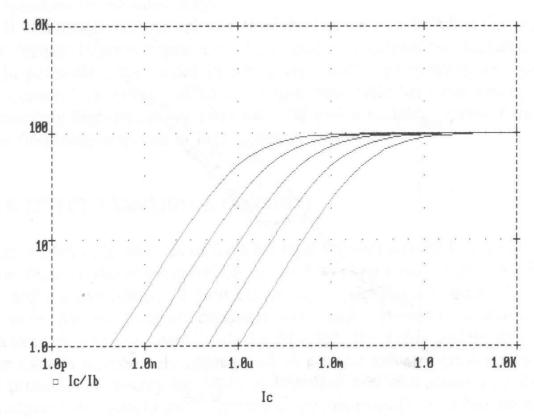

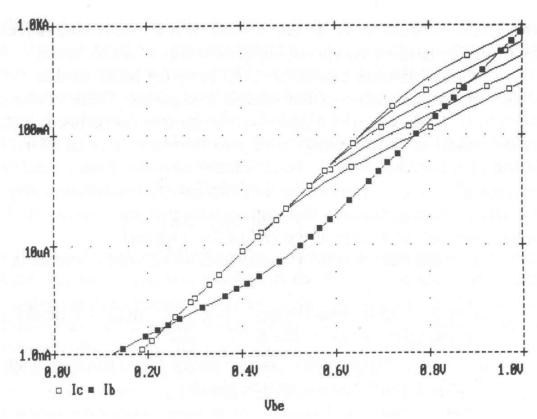

While searching the internet for information on SiC BJT an IEEE report studying 4H-SiC power BJT is found [12]. The purpose of this paper is to study the effectiveness of the SPICE Gummel-Poon model in predicting the behaviour of a SiC BJT. Instead of tweaking an existing Si BJT model a default transistor containing the parameters found in the IEEE study is created. Surprisingly the model is behaving quite near the behaviour of the real transistor, see figure 6.3 and 6.4. Notice that in the picture of the simulation with original IEEE parameters the voltage is set to 12 V. If it would be set to 70 V the IEEE switching would not even remind of the real switching.

Figure 6.3 The switching behaviour with the original IEEE parameters, turn-on.

The parameters the IEEE study has extracted are in table 6.2, the rest PSpice parameters are set to default:

Table 6.2 Parameters in the IEEE report.

| IS       | = | 4.31e-038 A  |

|----------|---|--------------|

| BF       | = | 18           |

| NF       | = | 1.323        |

| VAF (VA) | = | 130 V        |

| IKF (IK) | = | 0.728 A      |

| ISE      | = | 3.37e-019 A  |

| NE       | = | 3.243        |

| BR       | = | 0.09         |

| NR       | = | 0.99         |

| VAR (VB) | = | 21 V         |

| ISC (C4) | = | 1.845e-016 A |

| NC       | = | 4.064        |

| RB       | = | 23.85 ohm    |

| IRB      | = | 0.005676 A   |

| RBM      | = | 22 ohm       |

| RC       | = | 11 ohm       |

| CJE      | = | 4.96e-011 F  |

| VJE (PE) | = | 2.466 V      |

| MJE (ME) | = | 0.3451       |

| TF       | = | 6e-8 s       |

| CJC      | = | 1.658e-011   |

| VJC (PC) | = | 2.449 V |

|----------|---|---------|

| MJC (MC) | = | 0.4058  |

| XTB      | = | -0.9356 |

| XTI (PT) | = | 73.04   |

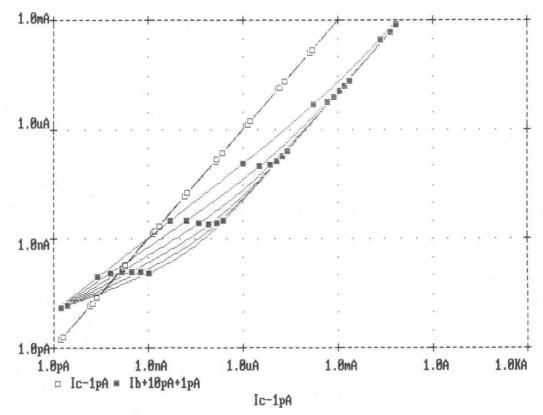

#### 6.4. The final model

With a lot of testing and tweaking the wanted behaviour of the transistor model is found. The result is four BitSiC models, the first is the one most similar to the first BitSiC we had. The other three versions are improvements made from the first BitSiC model to fit the second real BitSiC (BitSiC2) meaning that version three is the most similar to the real second BitSiC tested. Beneath there is a list of the changed parameters relative the IEEE report and the reason for the change, see table 6.3.

Table 6.3 Changed parameters relative to the original IEEE report

|     | IEEE01355311 | BitSiC2_ver3_delay | BitSiC2_ver3 changed relative IEEE original.               |

|-----|--------------|--------------------|------------------------------------------------------------|

| BF  | 18           | 30                 | Increased to get higher gain.                              |

| IKF | 0.728 A      | 40.728 A           | Increased, moving up DC knee high current.                 |

| NR  | 0.99         | 1.3                | Increased, making the Vce level to be higher.              |

| RB  | 23.85 ohm    | 0 ohm              | Decreased, to get better frequency response and noise      |

| RC  | 11 ohm       | 0.16 ohm           | Decreased, less Ic depending.                              |

| CJC | 1.658e-011 F | 1.558e-010 F       | Increased, slower falling, faster rising                   |

| VJC | 2.449 V      | 8.949 V            | Increased to get an increasing slope in the switch moment. |

| MJC | 0.4058       | 0.2558             | A factor to the slope.                                     |

| TF  | 6,00E-08     | 2.95e-010          | Decreased, faster internal current fall.                   |

| TR  | 1,00E-08     | 1,00E-12           | Decreased, lowering the time to turn on.                   |

| EG  | 1.11 eV      | 0.69 eV            | Does not have any larger effect (fine adjustments).        |

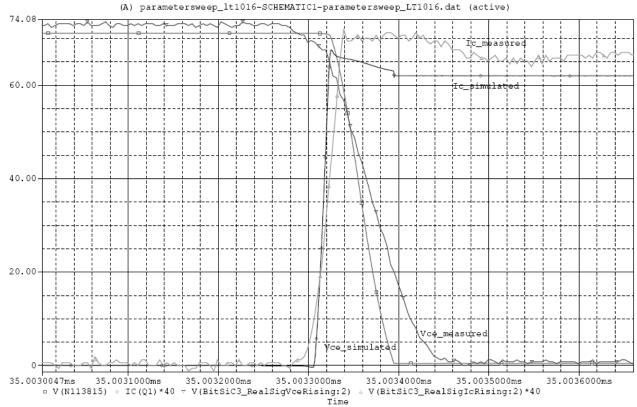

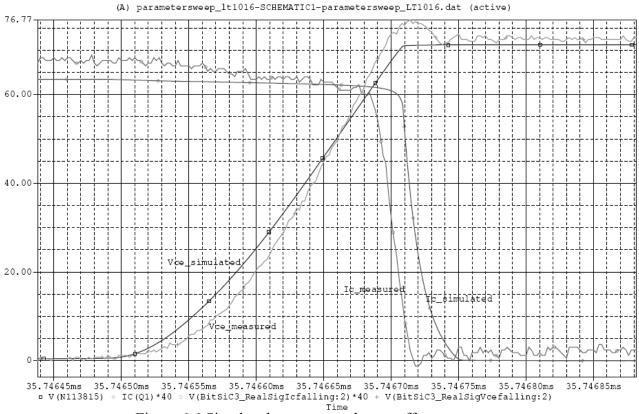

The result is very close to the measured data, with the final version of the BitSiC model it is easy to simulate and verify it with 70V, see figure 6.5 and 6.6.

Figure 6.5 Simulated vs. measured, turn-on.

Figure 6.6 Simulated vs. measured, turn-off.

#### 6.5. Uncertainty of measured data

There is a problem with the measured data that is used when trying to get a correct model. When measuring the real transistor the different instruments used has different delays. The current is measured with a current probe connected to an amplifier that is then connected to Tektronix oscilloscope, this setup can have a propagation delay of up to 30 ns with a rise time less than 7 ns. The voltage is measured with a 10x probe directly connected to the oscilloscope. Because of the different delays between the collected data we tried to alter the model and reduce the time difference. But the change did not succeed in the wanted way, this can effect later power loss calculations negatively. The goal was to verify the model with a 112 V simulation but because the lack of time the model could only get verified with 70 V.

#### 6.6. Conclusions

This part of the master thesis, modelling the transistor is perhaps the most difficult. The idea is to tweak an existing transistor model to get the wanted behaviour. The IEEE report supplied a good starting point that made it possible to create a model that is behaving similar to the measured BitSiC transistor.

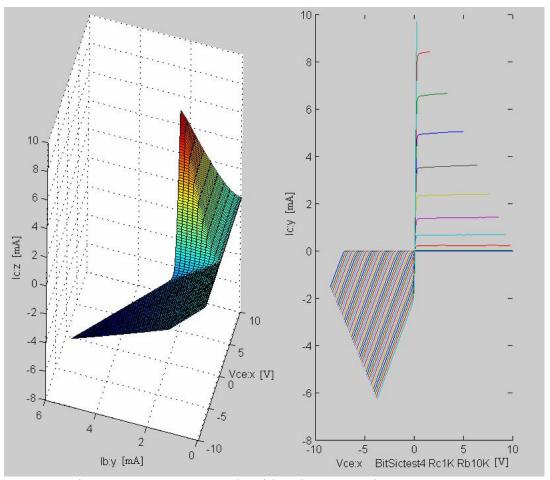

# 7. Three-phase simulation

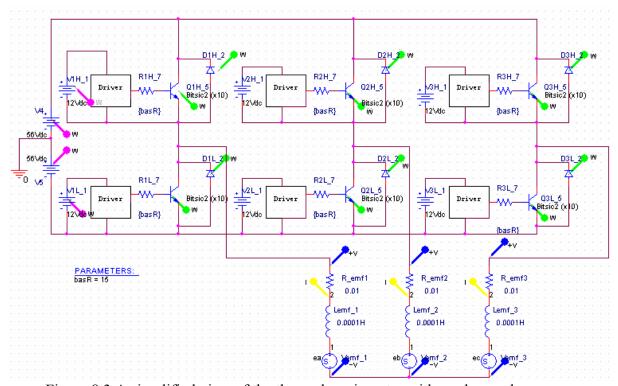

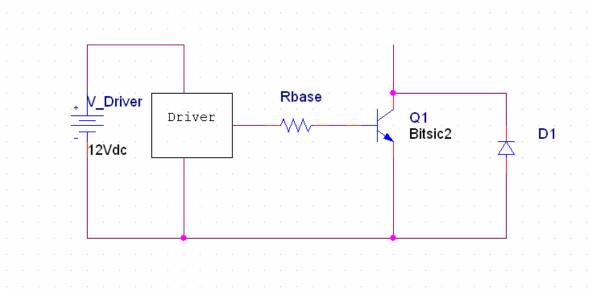

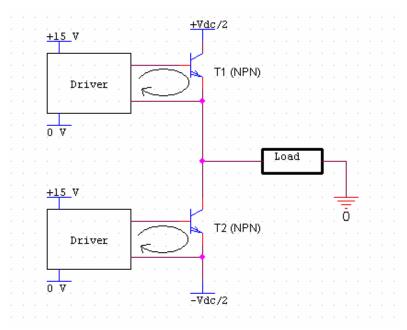

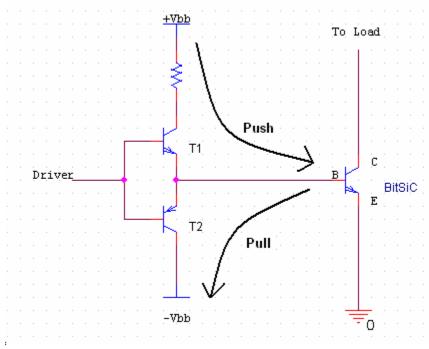

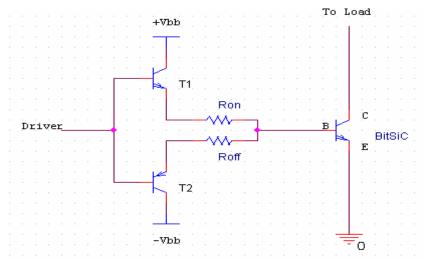

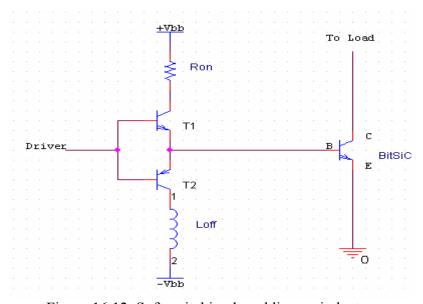

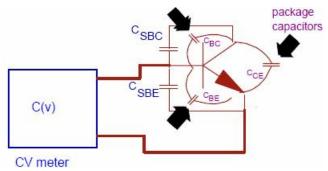

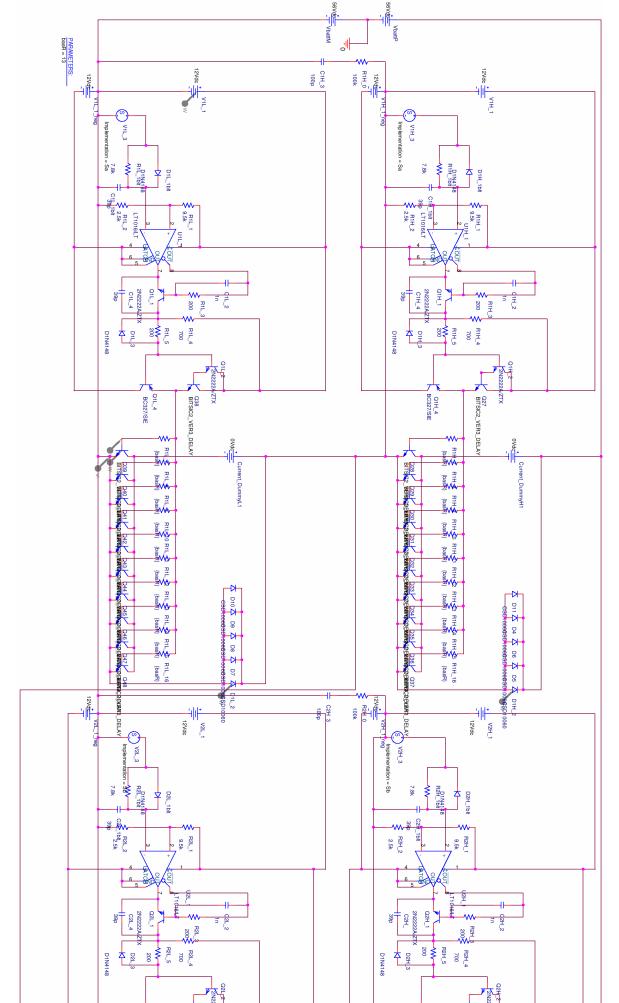

With the BJT model in the foregoing chapter the work is now to build a complete three-phase inverter in PSpice. Most of the design work is already done while creating the test rig, the main design of the driver is copied directly from the test rig. To be able to handle the current levels when simulating with the BitSiC, the transistors are placed in parallel. When normal Si BJT's is placed in parallel there might be stability problems due to the negative temperature coefficient, however SiC has positive temperature coefficient. This makes it easier to place the BitSiC BJTs in parallel, the only problem is that the driver has to handle the higher base current. Our test rig driver can not handle that amount of current. Using power BJT is not that common today, a solution to the problem is found by studying old literature. The problem is that the driver has to be very fast with relative high current. There is not any single BJT fast enough that can handle enough current, the solution is to use a Darlington bridge with the BitSiC, see figure 7.1.

Figure 7.1 One sixth part of the three-phase driver circuit, highside.

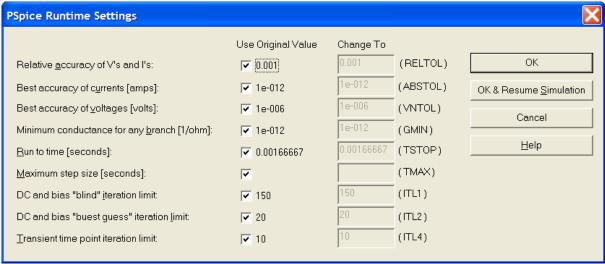

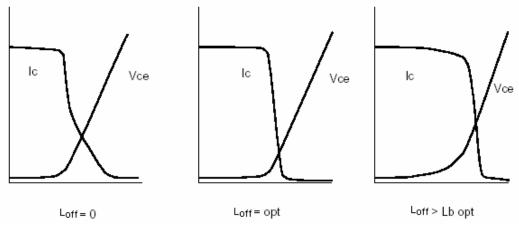

The problem with this solution is that the voltage across the Darlington is equal to Vce at transistor one (T1) plus the Vbe of transistor two (T2), in our case the BitSiC. The problem is that the Vbe of the BitSiC is almost 3 V. This will cause a very high power loss in the Darlington with a large current. The next idea is to use a MOSFET instead of a BJT for turning on the base current. But this solution did not work in the simulation program. Doing simulations in PSpice the transient sometimes changes to fast. By reducing the accuracy in the current (ABSTOL) some of the small transients will disappear making it possible to simulate, see figure 7.2.

Figure 7.2 PSpice runtime settings.

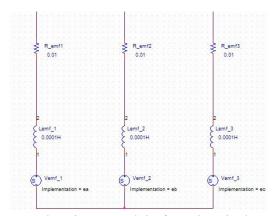

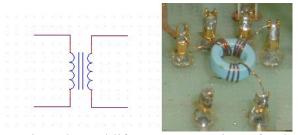

With the simulation problems the accuracy sometimes has to be as low as 1e-005 A. To reduce the transient problems a RC filter is made for the drivers, see figure 7.1. Running out of time the decision is to use the Darlington and concentrate on getting the whole simulation of the inverter to work. With the main idea of how the inverter shall be constructed a model of the EM is made. The specifications were already made, and the standard way of simulating an EM was used. An EM consists of three main parts, a resistance, an inductance and a back EMF for every phase, see figure 7.3.

Figure 7.3 Showing a model of an electrical machine.

The resistance and inductance values are determined with the help from Mats Alaküla. The back EMF is extracted from a Simulink model, explained later. The whole inverter can be seen in appendix H.

After a lot of struggle everything started to work properly, the next step is to start the simulation in the selected working point as if it is in stationary running condition. Because the simulation takes a long time with all the detailed switching, the idea is to just simulate one fundamental period for the EM. To get the simulation to start as if in stationary, the initial currents and back EMF had to be extracted and set as initial condition in PSpice.

To get the right switching signals, back EMF and initial currents to the inverter a Simulink program used at IEA at Lund's University is used. The Simulink model simulates a three-phase inverter with different current control methods, see figure 7.4.

Figure 7.4 Simulink model of the three-phase inverter.

The model is changed to better fit the application. The graphs and data collections are inserted to collect the data that is needed for the PSpice inverter to work in the stationary point. This model can easily be changed to use other types of switching and different EM parameters. With the model it is easy to change the battery voltage and the EM-size. The selected parameters for the three-phase inverter are in table 7.1 below.

Table 7.1 Showing the selected three-phase inverter parameters.

| clear all                                |

|------------------------------------------|

| Cical all                                |

| L=0.0001;                                |

| R=0.0;                                   |

| Udc=112;                                 |

| Marginfactor=1.1;                        |

| rpm=2000;                                |

| belttrans=3;                             |

| Poles=12;                                |

| Ts=0.02e-3;                              |

| Pem=5000;                                |

| Upp=Udc/sqrt(2)/Marginfactor;            |

| Omega=(rpm*belttrans*(Poles/2)*2*pi)/60; |

#### Where:

L = inductance in the EM windings [H].

$R = \text{resistance in the EM windings } [\Omega].$

$Udc = battery \ voltage \ [V].$

Marginfactor = Factor to keep the regulation within its boundaries. rpm = revolutions per minute of the engine [rpm]. belttrans = Transmission factor between the engine and EM. poles = number of poles of the EM. Ts = sampling interval [s].

All of these parameters are easy to change, and the chosen settings are made together with Mats Alaküla [13] to get a realistic simulation. The battery voltage is given by GM powertrain, for a light hybrid car is in the region of 112 V. The three-phase 2 level carrier modulator uses symmetriezed fixed frequency modulation, this can also be changed. The fixed frequency modulation uses 1/(2Ts) as modulation frequency. With a sampling frequency of 50 kHz the PWM frequency is 25 kHz. Using the part VSTIM, mentioned earlier, both the switching pattern and the back EMF from the Simulink three-phase inverter is imported to the PSpice. With all the signals connected to the PSpice inverter model the simulation of the total behaviour started. The result is seen in figure 7.5.

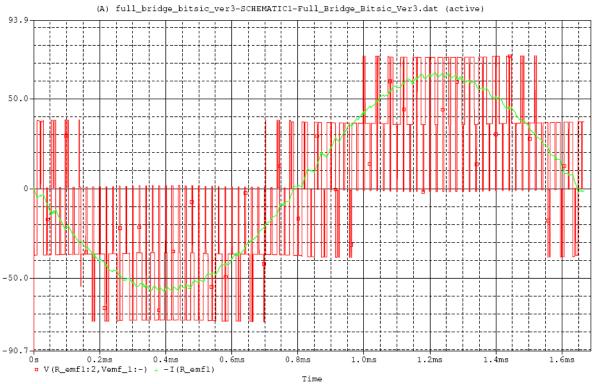

Figure 7.5 Voltage and current in one phase of the 5 kW EM at 25 kHz switching.

Figure 7.5 is showing one phase voltage and current. Both the driver and the BitSiC transistors are very fast and it is not any problem to increase the switching frequency. The extraction of the initial current in the EM inductors are a problem. Although the Simulink gives a value when using ideal switching it is not exactly the same for non-ideal switching. Seen in figure 7.6, when the initial current is not exactly correct there is a difference in the phase current. In the figure this phenomena results in that the top values differ slightly between the phases although the inverter is symmetrical.

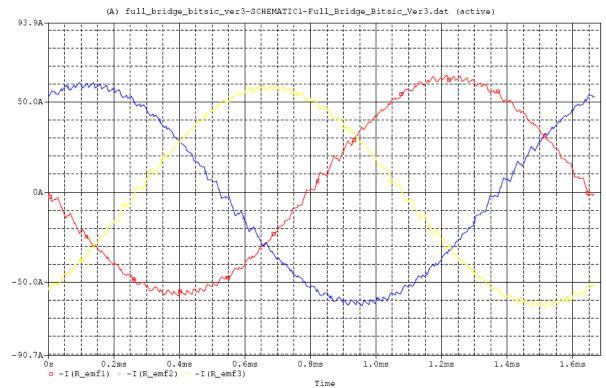

Figure 7.6 Currents in the 5 kW EM at 25 kHz switching.

With the three-phase inverter working properly the next step is to determine the efficiency of the inverter. Doing the simulations at a certain working point it is possible to calculate the efficiency and see how much power that is dissipated. With this data a calculation of how the cooling system shall be designed is possible.

# 8. Post processing of PSpice simulation

With the simulation of the three-phase inverter an evaluation of the performance is made. The post processing and evaluation of the performance is done in MATLAB. When running PSpice simulation there is an option to save the data points in a Common Simulation Data Format (.csdf/.csd). The csd-format will save all the data points that the simulation calculates with accordingly time stamps. To import the data points from the csd-file in to MATLAB variables an m-script file is written. MATLAB have a powerful set of mathematical scripts and inspections routines such as plotting.

#### 8.1. Interfacing MATLAB with PSpice

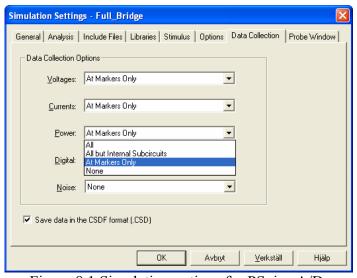

Normally when PSpice runs a simulation it saves all data (voltage, current, power, digital and noise) in a binary .dat-file. This file is then red by PSpice A/D where the signals can be viewed. PSpice A/D offers a wide set of tools for viewing signals such as zoom options and capability of performing simpler mathematics on signals. To import the simulated signals in to MATLAB a script is made to read a data format called Common Simulation Data Format (.csdf/.csd). To make PSpice save the data point to a .csdf-file the simulation settings is changed as viewed in figure 8.1.

Figure 8.1 Simulation options for PSpice A/D.

With the simulation settings it is decided what types of signals to save and in what format to save them in. These options are of great importance. In a regular simulation of the three-phase inverter there will be a massive size of the data file. If one fundamental period of the load (1.6 ms) is simulated the file size will be around 1 GB. This is far too much data to be handled smooth and easy. To be able to do some post processing work on the data, it is crucial to get rid of all the unnecessary data to get the file size down. This is done by configure the simulation setting (figure 8.1). By only saving the data from voltage-, current- and power-markers the size is reduced. A

marker is a probe that is placed in the schematic to view a specific signal. By limiting the signals, only the most important signals (around 29) will be saved this cut down the file size to around 20 Megabytes.

This file is then read by the MATLAB script "Pspice2Matlab.m". It soon became clear that it was not that easy to develop a MATLAB script to import the csd-file. The csd-file is not consistent in its file structure i.e. on every line there is a random number of variables. This made it hard to develop a MATLAB script that could read the csd-file. One other thing also makes it more complicated. In PSpice it is possible to use a differential voltage probe. This means that signal is the difference in voltage between the two differential probes. This is not represented with one variable per data point in the csd-file but with two data points relative ground. The script needed to recognize when a variable is a differential variable and subtract the two data point to get a true differential signal. To let the script know that a variable is a differential variable the variable names is fitted with an index notation. For example can a name line in the csd-file look like the following line:

name: wVbattP wQ1H 5 iR emf1 iR emf2 iR emf3 d1emf1 d2emf1

The script is able to tell what type of signal it is by checking the first letter.

- w noted that the signal is a power signal

- v noted that the signal is a voltage signal

- i noted that the signal is a current signal

- d1 noted that the signal is the first potential of a differential probe

- d2 noted that the signal is the second differential probe

In the case of the differential probe MATLAB creates the true differential probe by subtracting the data points:

$$d(t)=d1(t)-d2(t)$$

(8.1)

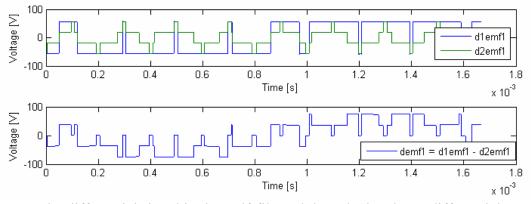

In figure 8.2 the result from the differential probe over one of the phases on the load is seen.

Figure 8.2 The differential signal in the csdf-file and the calculated true differential signal.

One can see that the zero and the switching becomes a sinusoidal like wave when subtracted.

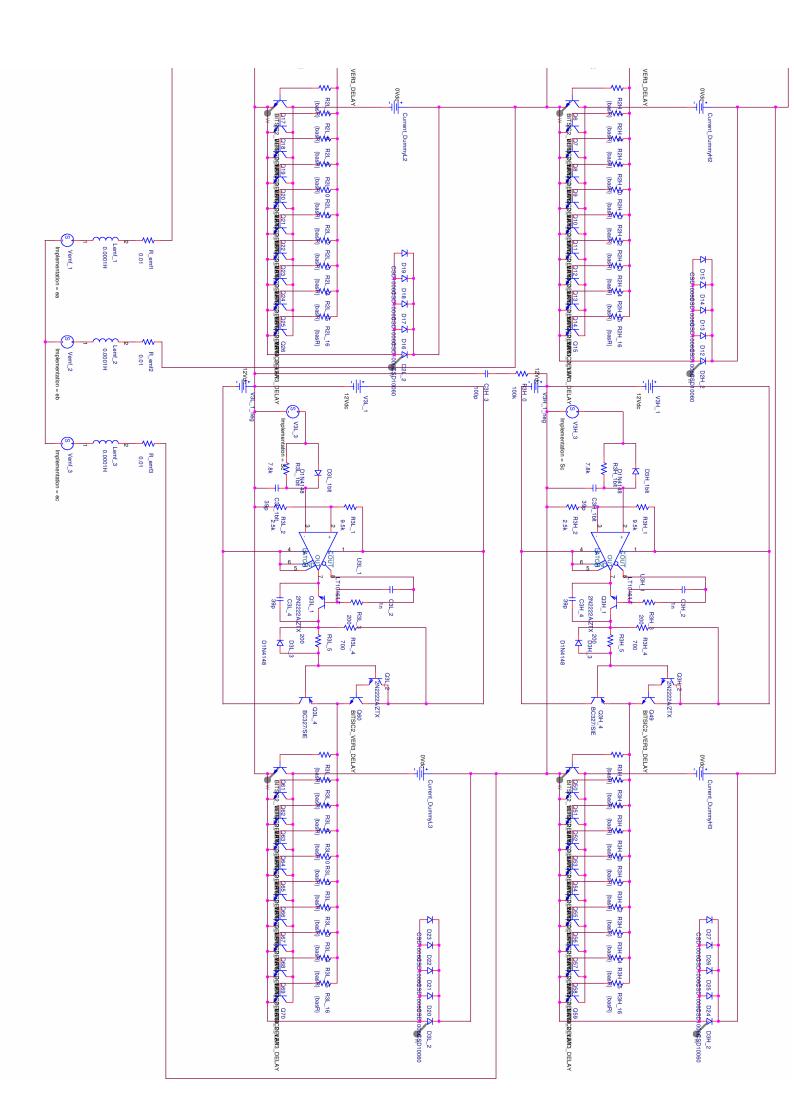

To get a full insight of how the three-phase inverter consumes power a certain signals is exported to MATLAB. First off the power is divided into two categories, the power providers and the power consumers. All the probes selected and imported in to MATLAB can be viewed in figure 8.3.

Figure 8.3 A simplified view of the three-phase inverter with marker probes.

I figure 8.3 all the power providing components are pink. For example the main batteries (V4, V5) and the driver batteries (V1H1, V1L\_1) give power to the circuits and the load. The driver's battery power is consumed inside the driver circuits, the base resistant and in the BitSiC transistors. The base current gives the power contribution Ib\*Vbe in the transistors. This base power contribution is the only part that influences the power in the inverter as a whole. The main battery power is consumed in the transistors, the diodes or the load. This is the reason why there are green power probes at the transistor and the diodes. These probes register all the power consumed in the transistors and the diodes. Power probes are not used in the load because the load does not consist of one component. Instead the voltages over the phases using (blue) differential probes and the current in the phases using current probes (yellow) is saved. When these are multiplied they give the power consumed in the load.

#### 8.2. Efficiency Calculations

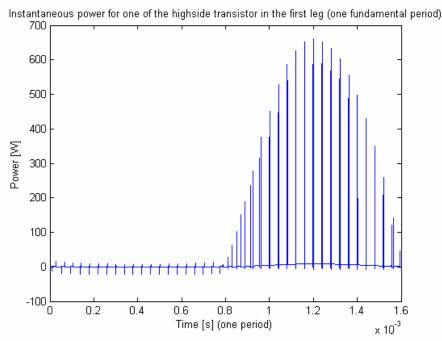

When the power of the upper transistor in the first leg is imported to MATLAB it looks like figure 8.4.

Figure 8.4 Instantaneous power for Q1H 5 (high side transistor for one of the phase).

The signal is represented in MATLAB with two data vectors one containing the power data and one containing the time. The time vector is the same for all the probes. The solver in PSpice A/D calculates the data points for all the markers at different time samples. It is of most importance to remember that the solver uses variable time step. When the signals changes the time step is smaller than when the signal is constant. Figure 8.4 shows the instantaneous power consumption in the transistor Q1H\_5. Notice that during the first half period the transistor almost does not consumes any power. Instead it is the diode in anti parallel with the transistor that leads the current and consumes power. To calculate the power equation 8.2 is used.

$$P = V * I \tag{8.2}$$

However equation 8.2 uses average values of current and voltages. In this case it is necessary to integrate the average power for one second to get the true average power consumption, see equation 8.3.

$$P = \int_{t=0}^{t=1} p(t)dt$$

(8.3)

Because the power signal in figure 8.4 is not a continues signal it is needed to approximate the integral with a sum of the signal.

$$P = \int_{t=0}^{t=1} p(t)dt \approx \sum_{k=1}^{k=N} (p(t) * dt)$$

(8.4)

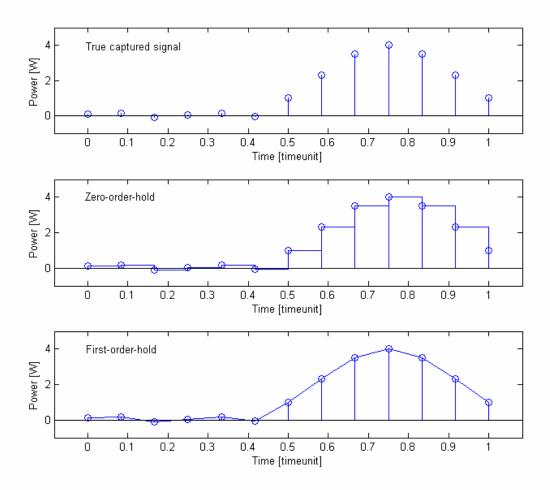

In equation 8.4 the signal is approximated with a sum. This approximation can be viewed in figure 8.5. In Figure 8.5 there is a "made up" signal to illustrate the problems with approximations.

Figure 8.5, Top: True sampled signal. Mid: Zero-order-hold approximation. Bottom: First-order-hold approximation.

In the sampled signal of figure 8.5 there is no power defined because it is a discrete signal. It is of course not true that there is no power in the signal. To calculate the signal an approximation of how the signal looks in between the samples is made. One way of doing this is shown in the middle of figure 8.5. The signal is approximated with a zero-order-hold. With zero-order-hold one sample is used and prolonged with no derivate to the next sample. With a zero-order-hold it is possible to calculate the power in the example according to equation 8.5.

$$P_{ZOH} = \sum_{n=1}^{N} p(n) * \Delta t = 1.4083 \text{ W}$$

(8.5)

However a zero-order-hold approximation leaves triangle gaps, it is not likely that the signal look like a zero-order-hold. The higher the derivate or the time step the more error a zero-order-hold approximation will give. This is the reason to use another approximation method to get a more realistic approximation. This is done via a first-order-hold. In a first order hold the first derivate is calculated and added to the samples. This results in triangles being added to the zero-order-hold. To use a first-order-hold to approximate an integral is called a trapezoidal numerical integration [14]. MATLAB has a built in commando for a trapezoidal numerical integration called "trapz".

$$P_{FOH} = \sum_{n=1}^{N} \frac{\Delta t}{2} (p(n) + p(n+1)) = 1.4458 \text{ W} \quad [15]$$

(8.6)

One other thing that is different from ordinary analytic maths is that there are not equivalent time steps. Because the time step changes over time this has to be taken in to account. The "trapz" command has an optional input argument, the time vector. With this optional time vector the trapz function can calculate the true trapezoidal integration and taking the variable time in to account. The trapz function calculates the integral as equation 8.7.

$$P_{FOH} = \sum_{n=1}^{N} \frac{t(n+1) - t(n)}{2} (p(n) + p(n+1)) = 1.4458 \,\text{W}$$

(8.7)

Now all the tools for calculating the power in the three-phase inverter are found.

To calculate the efficiency the equation 8.8 is used.

$$\eta = \frac{Useful \ power \ output}{Total \ Power \ input}$$

(8.8)

The "useful power output" is the power that the load draws. The "total power input" is the power that the batteries give. In this case the total "power input" can be divided into two components, the main battery consisting of two 56 V voltage sources (V4, V5) and the batteries for the drive circuits. The efficiency is presented in both with and with out the driver. This has to do with the efficiency of the driver. The driver is not optimized for efficiency and has efficiency around 26%. This is the reason for giving the efficiency numbers with and without driver to give a more independent and fair number of the BitSiC's performance. This concept will give two definitions of the efficiency; see equation 8.9 and equation 8.10.

$$\eta_{With driver} = \frac{Load \ Power}{Main \ Battery \ Power + Driver \ Power}$$

(8.9)

$$\eta_{Without driver} = \frac{Load \ Power}{Main \ Battery \ Power}$$

(8.10)

Three different PWM frequencies are simulated 5 kHz, 25 kHz and 100 kHz. These frequencies show how versatile the BitSiC is. PWM frequency of 25 kHz will give a good performance in regard to the load ripple and three-phase inverter performance. 5 kHz is perhaps considered a low-end value for the load, with another load or different ripple ratings the PWM frequencies can be lowered considerably lower than 5 kHz. However it shows how the efficiency increases at lower PWM frequencies. The High-End value 100 kHz shall not be considered a max operating PWM frequency. The choice of 100 kHz is made because it is the PWM frequency of SEMIKRON's [16] high-end drive circuits. The BitSiC showed good performance at this high frequency. The PWM frequency can probably increased to a higher value, but at 100 kHz the other element than the BitSiC showed signs of being in need to get optimized or changed in order to increase the PWM frequency. The result of the simulation can be viewed in table 8.1. For a full investigation of power consumption and efficiency for the three-phase inverter the reader is referred to Appendix I.

Table 8.1, Efficiency with and without diver for different PWM frequencies.

|                           | 5 kHz | 25 kHz | 100 kHz |

|---------------------------|-------|--------|---------|

| efficiency with driver    | 0.94  | 0.94   | 0.91    |

| efficiency without driver | 0.98  | 0.96   | 0.92    |

An efficiency of 0.91 to 0.98 seams to be a rather good number. It is hard to make comparison because the efficiency is so dependent on the working point and what to include. But it seams like the SiC technology can fulfil the prediction made in [17], that the SiC can improve the efficiency from today's 0.93.5 % to 0.98%.

#### 8.2.1. Efficiency improvements

There are several things that lower the efficiency, the most apparent is the driver. But the rather low main voltage (112 V) will also give higher losses. Thinking in terms of efficiency a BJT might seem as a bad choice in comparisons with a MOSFET or IGBT, but it is not as bad as one might think. Let's study BJT driving in detail (figure 8.6).

Figure 8.6 Schematic figure for driving the BJT.

The problem with a BJT is that one need continues base current to drive the transistor. The driver selected in this master thesis has a rather low efficiency. This can however certainly be greatly improved. The required power that the BJT needs to be driven can be calculated as in equation 8.11.

$$P_{\text{required}} = Vbe * Ib \tag{8.11}$$

The total power ratings for the six drivers are 128.30 W. With a 25 kHz switching frequency the total power dissipated in the BitSiC transistors (Required) is 33.74 W. The rest of the power is dissipated in the base resistor and in the Darlington transistor that drives the base resistor. There are several things that can be done to improve the efficiency of the driver. One way is to decrease the voltage of the driver (V\_driver). If the voltages is decreased it will lower the voltage drop over the base resistor and thereby remove most of the unnecessary power losses in the driver. One other thing to do is to remove the base resistor entirely. The current still needs to be restricted at 3.44 A per position and leg. This could perhaps be solved with working the transistors in the driver box in the active area. But this will also give high losses. One method that improves the driver efficiency is to build the driver as a switched current controller (SCC). This is perhaps the method that will give the best driver efficiency. With a SCC-driver the efficiency would probably be greater than 90%. A SCC will work like the three-phase inverter but as a miniature. The SCC will in principle be constructed like in figure 8.7.

Figure 8.7 Switched current controller driver.

In a SCC the base resistor will be replaced with an inductor. This inductor shall then be driven with a PWM-pulse to regulate the current in the inductor. The efficiency with driver will approach the numbers as calculated without a driver. Using a SCC will also solve the problem of supplying the driver with a high current 12 V supply. With a SCC it is possible to drive the base inductor with the main DC voltage. This will greatly decrease cost and space for the drivers DC-DC converter.

One other technique to improve the efficiency is to increase the main voltage of the inverter. With the help of a rough and general calculation of the static conduction power loss the benefit of an increased voltage can be seen.

#### Calculation:

With a setup of a main voltage of 112 V and two transistors in series, each with a voltage drop of approximately 1.4 V and a current of 45 A DC. It is possible to calculate the power loss in the transistors:

$$P_{phase} = 2 * V_{ce(sat)} * I_{load} = 2 * 1.4 * 45 = 126 W$$

(8.12)

If the remaining voltage is assumed to end up across the load, the load voltage will be:

$$V_{Load} = V_{Main} - 2 * V_{ce(sat)} = 112 - 2 * 1.4 = 109.2 V$$

(8.13)

This will give an efficiency of:

$$\eta_{With driver} = \frac{V_{Load} * I_{Load}}{V_{Load} * I_{Load} + 2 * V_{ce(sat)} * I_{load}} = \frac{109.2 * 45}{109.2 * 45 + 2 * 1.4 * 45} = 0.975$$

(8.14)

If the voltage now is increased three fold to 336 V it is possible to decrease the current three fold, which will give a DC current of 15 A. This will give a new power loss in the transistors:

$$P_{phase} = 2 * V_{ce(sat)} * I_{load} = 2 * 1.4 * 15 = 42 W$$

(8.15)

In the same way as before, the load voltage will be:

$$V_{Load} = V_{Main} - 2 * V_{ce(sat)} = 336 - 2 * 1.4 = 333.2 V$$

(8.16)

and the efficiency will be:

$$\eta_{With \ driver} = \frac{V_{Load} * I_{Load}}{V_{Load} * I_{Load} + 2 * V_{ce(sat)} * I_{load}} = \frac{333.2 * 15}{333.2 * 15 + 2 * 1.4 * 15} = 0.992$$

(8.17)

This example shows how the efficiency is increased when the voltage increases. The change from 0.975 to 0.992 might seem trivial, but this small change will have a big effect on reduction of the power dissipation in the switching transistors, as a matter of fact if one increase the voltage three times it decreases the static power dissipation in the transistor by three times.

This is why the Toyota's hybrid car Prius is using a voltage step-up converter [18]. The Prius battery has a nominal voltage of 201.6 V. The battery voltage is then transformed with a buck-boost converter to maximum 500 V that then drives the EM. With the bigger bandgap of the SiC BJT it is also more appropriate to work with higher voltages than for regular Si BJT's.

### 9. Thermal calculations

To get a good reliable design it is necessary to estimate the power loss that occurs in the inverter so that it can be cooled in the right way. To keep the electronics reliable, working and not overheating it has to be kept under a certain temperature. This temperature level is different for different types of components, also there are other problems with higher temperatures like thermal stress. In this master thesis it is especially interesting to look at the power electronics components, these are made of silicon carbide. Silicon carbide can withstand much higher temperatures than ordinary silicon components.

Calculating the losses in the inverter is done in different ways. One way is to calculate the losses with datasheets and get an estimation of the dissipated power. Another way is to simulate the switching losses in a simulation program. A third way is to build a test rig and measure the losses for one switching under different currents and voltages. TranSiC does not have any datasheets for the BitSiC so a test rig is built. With the test rig it is possible to measure the voltages and currents and use it to do a model of the transistor. With the test rig it is easy to run a single switching for different types of drive circuits and for different transistors. After the model is built, the design of the entire three-phase inverter is simulated.

To get an approximation of the power dissipation that has to be cooled away, several three-phase simulations are performed. The power dissipation turns into undesired heat that travels thru different layers of material with different properties in the BJT. Convention, radiation and conduction are the three different types of heat transfer. Convention is the most complicated process to get an accurate model for. For both radiation and conduction there exist accurate models.

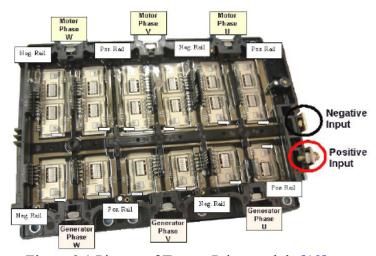

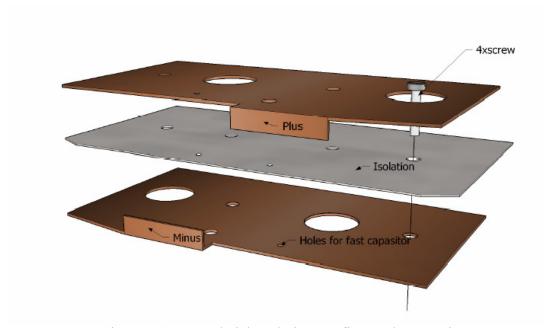

The packaging of common power electronics component is not suitable for higher temperatures than up to 175 °C. This is a disadvantage for silicon carbide. Ordinary silicon BJT components losses its current gain abilities at temperatures around 150 °C. Silicon carbide can easily operate in temperatures above 250 °C, see [19]. The problem is to make a reliable packaging of the chip, with today's technology it will be possible do a package that can withstand temperatures up to 200 °C. This will mean that it will not be the SiC junction that limits the maximum temperature. TranSiC has at current time not decided on what type of case the BitSiC component will have. A car manufacture will get the highest performance if they design a special made case like the one in Toyota Prius, see figure 9.1.

Figure 9.1 Picture of Toyota Prius module [18].

Because the BitSiC do not have a capsule, and thereby do not have any packaging specification. The choice is to take temperature coefficients for an IGBT-module that will fit the specifications. The thermal specifications for SiC and Si are not the same. SiC has around three times better thermal conductivity than Si, but today the Si-chip wafers can be made almost three times thinner than SiC wafers, also the Si transistor chip has large area. So an expected SiC module going out on the market at this time are likely to have the same thermal conductivity as for a Si –module [20].

The SEMIKRON's SKM 75GD123DL IGBT-module has about the same current / voltage ability as expected for the SiC module. The module has 0,32 °C/W as thermal conductivity. Looking at the junction temperature one must see if the temperature changes fast or if it can be seen as stationary, depending on the time constants of the cooling system. The highest thermal capacitance in the module has a time constant of 0.08 s. This is far less than the power fluctuation for a BAS. In this time range it is possible to see the calculations as stationary and thereby exclude thermal impedance.

## 9.1. Calculating the maximum thermal heatsink resistance

Approaching the problem with the undesired heat it is interesting to see if it is possible to cool the power inverter with the combustion engines cooling water. After studying different methods to calculate the maximum value of the thermal resistance for the heatsink, the method taught at the power electronics course at LTH Lund's University is chosen. This method follows three steps.

1. Determine the needed heatsink temperature for all components with a maximum junction temperature. For each component calculate.

$$T_{hj} = T_{Jj} - P_{Dj} * (R_{thjc,j} - R_{thch,j})$$

(9.1)

2. The component requiring the lowest heatsink temperature will determine the maximum heatsink temperature. Use this as the heatsink temperature.  $T_h = \min(T_{hi}) \tag{9.2}$

3. This selection of heatsink will make some components to have lower silicon temperature than the maximum allowed. The maximum allowed thermal

heatsink resistance can be calculated as:

$$T_h = T_a + R_{thha} * \sum_{j=1}^{n} P_{dj} \Rightarrow R_{thha} = \frac{T_h - T_a}{\sum_{j=1}^{n} P_{dj}}$$

(9.3)

In worst case the temperature in the cooling water will reach up to 130 °C. Maximum temperature for a SiC-junction is 250 °C and for a Si-junction 150 °C. In practical designs a margin of 20-40 °C below the rated maximum junction temperature is desired. For a SiC component it is possible that the capsule will restrict the maximum temperature. Because of this a restriction for the maximum temperature for the SiC component will be 200 °C. With a margin of 25 °C for the SiC module the junction temperature will be 175 °C. Using the lowest margin (20 °C) for a Si module the junction temperature will be at 130 °C. This shows that it is not possible to use Simodule as a reliable power electronic component for the inverter cooled with the combustions engine cooling water. Some of the surrounding electronic components can withstand this high temperature, and those that cannot, should be shielded with a heat shield and other precautions. The most important is that the power handling part of the inverter is close to the EM, minimizing the losses in cables and with the engine bay shielding of the Electromagnetic interference (EMI).

Calculation of the thermal heatsink resistance (25 kHz):

1. With a junction temperature of 175 °C.

$$T_{Transistor} = 175 - 171.6 * (0.32 - 0.14) \approx 161.84 \,^{\circ}\text{C}$$

(9.4)

$$T_{Diode} = 175 - 47.3 * (0.6 - 0.14) \approx 169.17 \,^{\circ}\text{C}$$

(9.5)

2. This shows that the transistor needs the most cooling and the heatsink maximum temperature will be:

$$T_h = 161.84 \,^{\circ}C$$

(9.6)

3. The maximum allowed thermal heatsink resistance is:

$$R_{thha} = \frac{161.84 - 130}{218.92} \approx 0.145 \,^{\circ}\text{C/W}$$

(9.7)

This is a rather high value and will not be any problem to meet for a liquid cooled heatsink. Looking at standard cooling plates, Austerlitz liquid cooling has a cooling plate (75-631-17 at ELFA's homepage [21]) that has 0.025 °C/W thermal resistance at 10 l/min. There are many other specialized companies in cooling electronics that has lower thermal resistance, Tykoflex [22] has cooling plates that has thermal resistance below 0.008 °C/W at 5 l/min.

## 9.2. Calculate the junction temperature

The calculation in the previous section resulted that there is no problem to find a heatsink for a SiC three-phase inverter. In the following calculation the goal is to step backward and start with a specified heatsink and then calculate the junction temperature.

For the calculation the following is given:

Temperature for the ambient water:  $Ta = 130 \, ^{\circ}C$

Heatsink thermal resistance: Rthha = 0.025 °C/W (ELFA) Power dissipation for the transistors: Pbjt = 171.61 W Thermal resistance for junction-case: Rthjc = 0.34 °C/W Thermal resistance for case-heatink: Rthch = 0.6 °C/W

The maximum temperature of the heatsink can be calculated according to equation 9.8.

$$Th = Rthha * Pbjt + Ta = 0.025*171.61+130 = 134.29 °C$$

(9.8)

The junction temperature will be:

$$T_j = Th + Pbjt * (Rthjct + Tthch) = 135.47 + 218.92 * (0.34 + 0.6) = 147.45 °C$$

(9.9)

What this means is that with the given data, a standard water heatsink from ELFA the junction temperature for the SiC transistors will be 147 °C. This is far from the maximum junction temperature for the SiC at 250 °C. Even the most standard BJT or IGBT is rated up to 150 °C. Although there is one major problem with standard Si components, at degrees above 100 °C the performance is so degraded that it is almost impossible to find a transistor that work's.

### 10. Conclusions

This master thesis started with the task to figuring out an appropriate size of the electrical machine in a BAS. After many Simulink simulations with different types of engines and driving cycles, an EM-size of 5 kW is a good size, giving both low fuel consumption as well as keeping the EM-size to a minimum.

Knowing the appropriate size of the EM the design of an actual three-phase inverter started. The main component in the inverter is supposed to be a SiC-based transistor (BitSiC). But the limited access to components forced us to do a simulation of the inverter instead. When doing simulations a model of the transistor is needed.

To see the BitSiC behaviour a test rig is constructed.