# Auxiliary Module for Unbalanced Three Phase Loads with a Neutral Connection

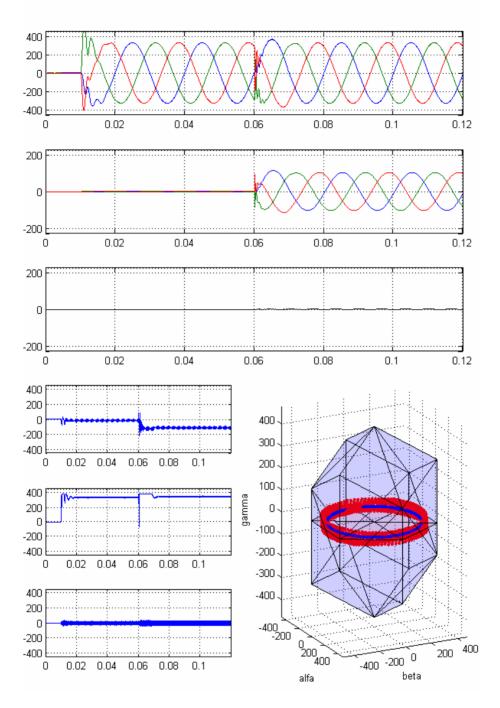

## Nils Lundström

## **Rikard Ströman**

Dept. of Industrial Electrical Engineering and Automation Lund University

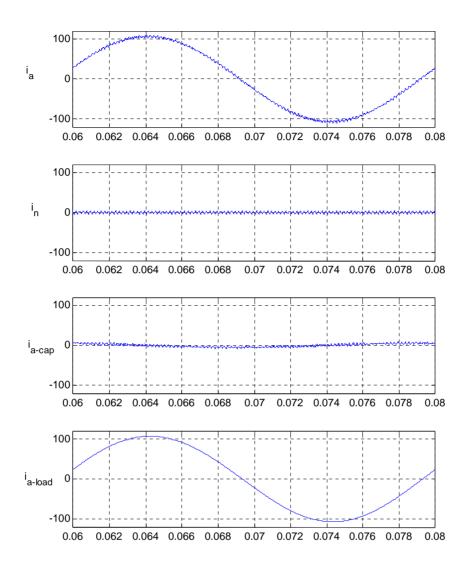

### Abstract

The company *Land Systems Hägglunds AB* is a leading manufacturer of combat vehicles and all terrain vehicles. One of Land systems Hägglunds projects for the future is the multi purpose combat vehicle, SEP, using a hybrid diesel-electrical drive train. Because of the diesel-electrical drive train, all the mechanical power produced by the diesel engines is transformed into electricity. The electrical system of the vehicle is by that dimensioned for high electrical power. This power could be used, besides for traction of the vehicle, for numerous purposes. For example external electrical tools, motors, PC:s, radios, radar equipment etc.

To make the electrical power useful for an arbitrary load, it needs to be transformed into a four wire three-phase 230/400V 50Hz AC system, using the dc-link voltage of the SEP as raw material. Ideally, the three phase system should act similar to an ordinary connection to the main electric grid. The purpose of the thesis is to examine the possibility to achieve this by using a 50 kVA DC/AC power electronic converter with four half bridges, providing three phase terminals and one neutral terminal. The converter is called *ACM (Auxiliary Converter Module)*

The thesis deals in a structured way with the problems and issues concerning design of the converter and especially its control. Effects of unbalanced three phase loads, voltages and currents, in a four wire system, are highlighted. It covers theory of three-phase systems and their representation in phasors, sequences and vectors. The vectors are presented in stationary (a - b - g) and rotating (d-q-0) coordinate systems. It also covers the theory of pulse-width modulation as well as circuit models and design methods for vector control in rotating d-q-0-coordinates. Dimensioning aspects of main physical components and loss calculations of the semiconductors are covered but not highlighted. Finally some issues concerning the implementation of a digital control are dealt with.

A model of the designed converter, including control systems, is built in Matlab/Simulink. The model contains the important aspects of a physical converter. Specified load scenarios are simulated and the results are presented.

## Acknowledgements

First we would like to thank our supervisor Per Karlsson for his advice, expertise and support. We also want to thank our examiner Mats Alaküla for, during the years, strongly contributing to our interests in power electronics. Anders Robertsson (department of Automatic Control, LTH) has also been very helpful to us in our work. The people we were connected with at Land Systems Hägglunds deserve a special appreciation for providing a nice and friendly working environment. Especially Örjan Sjöström, Urban Lundgren, Svante Bylund and Lars-Gunnar Larsson. Finally we want to thank our families for their support during our years of studies at Lund Institute of Technology, LTH.

Nils Lundström Rikard Ströman

## Contents

| Abstract                                                                                                                                                                                    | 1                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Acknowledgements                                                                                                                                                                            | 2                                                                                |

| Contents                                                                                                                                                                                    | 3                                                                                |

| 1. Introduction                                                                                                                                                                             | 5                                                                                |

| 1.1 Background                                                                                                                                                                              | 5                                                                                |

| 1.2 Problem                                                                                                                                                                                 | 6                                                                                |

| 1.3 Purpose                                                                                                                                                                                 | 6                                                                                |

| 1.4 Delimitation                                                                                                                                                                            | 7                                                                                |

| 1.5 Outline                                                                                                                                                                                 | 8                                                                                |

| 2. Theory                                                                                                                                                                                   | 9                                                                                |

| 2.1 Three-phase systems                                                                                                                                                                     | 9                                                                                |

| 2.1.1 Three-phase systems in phasor representation                                                                                                                                          | 9                                                                                |

| 2.1.2 Three-phase systems in sequense representation                                                                                                                                        | 10                                                                               |

| 2.1.3 Y- and $\Delta$ -connections                                                                                                                                                          | 12                                                                               |

| 2.1.4 Three-phase systems in vector representation in fixed co                                                                                                                              | ordinates                                                                        |

|                                                                                                                                                                                             | 13                                                                               |

| 2.1.5 Vector representation in synchronous coordinates                                                                                                                                      | 15                                                                               |

|                                                                                                                                                                                             |                                                                                  |

| 2.1.6 Unbalanced system                                                                                                                                                                     | 17                                                                               |

| <ul><li>2.1.6 Unbalanced system</li><li>2.2 Loads to evaluate</li></ul>                                                                                                                     |                                                                                  |

| ·                                                                                                                                                                                           | 21                                                                               |

| 2.2 Loads to evaluate                                                                                                                                                                       | 21<br>24                                                                         |

| <ul><li>2.2 Loads to evaluate</li><li>2.3 Three leg converters</li></ul>                                                                                                                    | 21<br>24<br>24                                                                   |

| <ul><li>2.2 Loads to evaluate</li><li>2.3 Three leg converters</li><li>2.3.1 The three leg bridge</li></ul>                                                                                 | 21<br>24<br>24<br>26                                                             |

| <ul> <li>2.2 Loads to evaluate</li> <li>2.3 Three leg converters</li> <li>2.3.1 The three leg bridge</li> <li>2.3.2 Pulse-width modulation</li> </ul>                                       | 21<br>24<br>24<br>26<br>29                                                       |

| <ul> <li>2.2 Loads to evaluate</li> <li>2.3 Three leg converters</li> <li>2.3.1 The three leg bridge</li> <li>2.3.2 Pulse-width modulation</li> <li>2.3.3 Symmetrized modulation</li> </ul> | 21<br>24<br>24<br>26<br>29<br>30                                                 |

| <ul> <li>2.2 Loads to evaluate</li> <li>2.3 Three leg converters</li></ul>                                                                                                                  | 21<br>24<br>24<br>26<br>29<br>30<br>31                                           |

| <ul> <li>2.2 Loads to evaluate</li></ul>                                                                                                                                                    | 21<br>24<br>24<br>26<br>29<br>30<br>31<br>32                                     |

| <ul> <li>2.2 Loads to evaluate</li></ul>                                                                                                                                                    | 21<br>24<br>24<br>26<br>29<br>30<br>31<br>32<br>34                               |

| <ul> <li>2.2 Loads to evaluate</li></ul>                                                                                                                                                    | 21<br>24<br>24<br>26<br>29<br>30<br>31<br>32<br>34<br>35                         |

| <ul> <li>2.2 Loads to evaluate</li></ul>                                                                                                                                                    | 21<br>24<br>24<br>26<br>29<br>30<br>31<br>32<br>34<br>35<br>37                   |

| <ul> <li>2.2 Loads to evaluate</li></ul>                                                                                                                                                    | 21<br>24<br>24<br>26<br>29<br>30<br>31<br>32<br>31<br>32<br>34<br>35<br>37<br>37 |

| 2.5.2 The system in d-q-0-coordinates                       | 40  |

|-------------------------------------------------------------|-----|

| 2.6 Dimensioning                                            | 43  |

| 2.6.1 Dc-link voltage                                       | 43  |

| 2.6.2 Power electronic switches                             | 44  |

| 2.6.3 Switching frequency and converter losses              | 45  |

| 2.6.5 Dc link capacitor                                     | 52  |

| 2.7 Control of the system                                   | 54  |

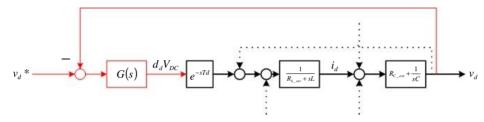

| 2.7.1 Model of the system to control                        | 55  |

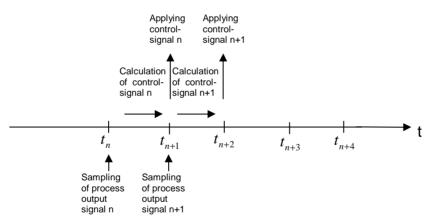

| 2.7.2 Delays                                                | 56  |

| 2.7.3 Voltage control                                       | 56  |

| 2.7.4 Control methods                                       | 57  |

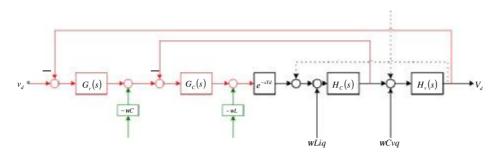

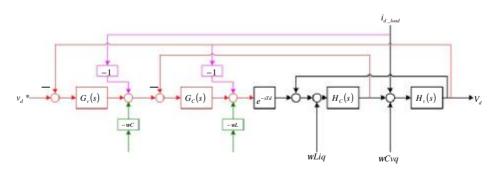

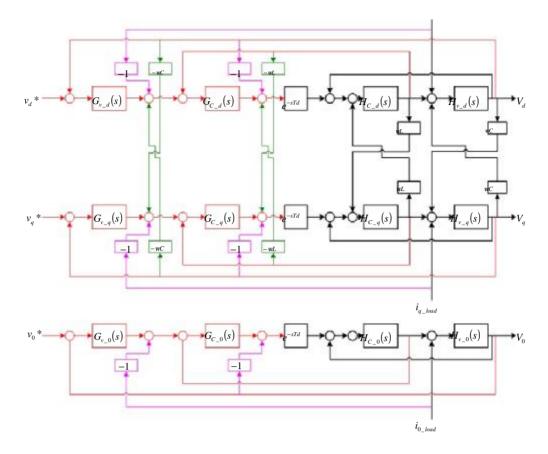

| 2.7.5 Model of the system, including controllers and delays | 64  |

| 2.7.6 Parameters of the controllers                         | 65  |

| 3. Method                                                   | 67  |

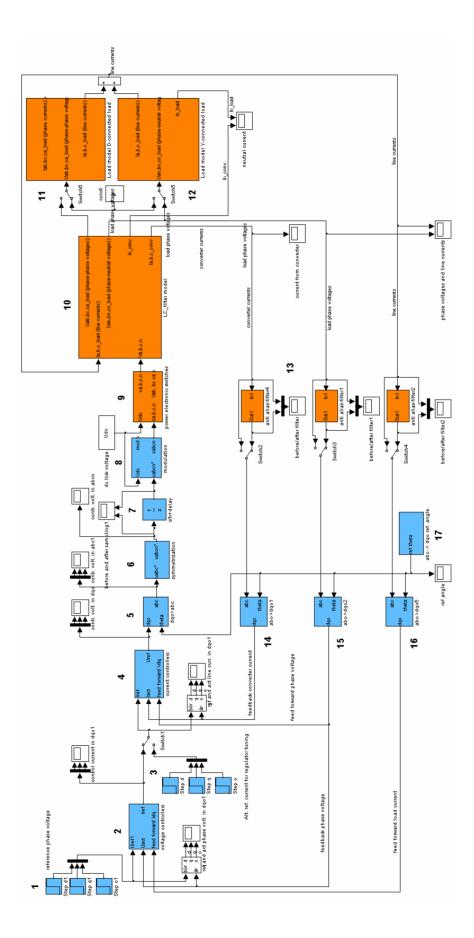

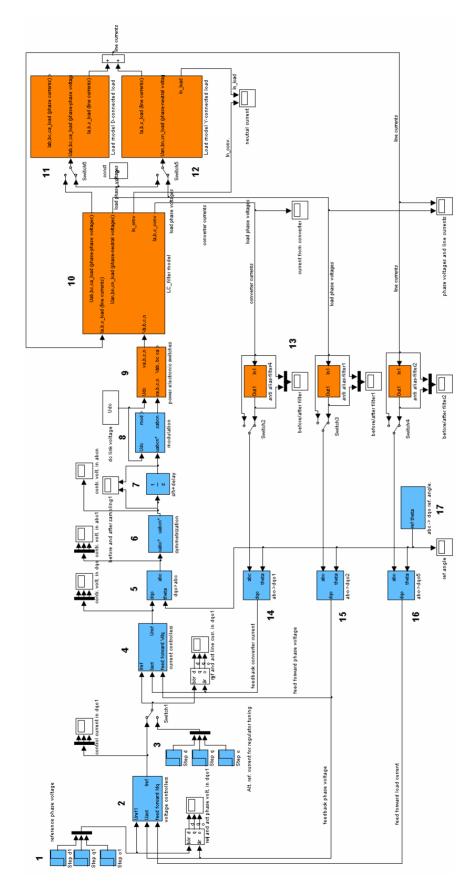

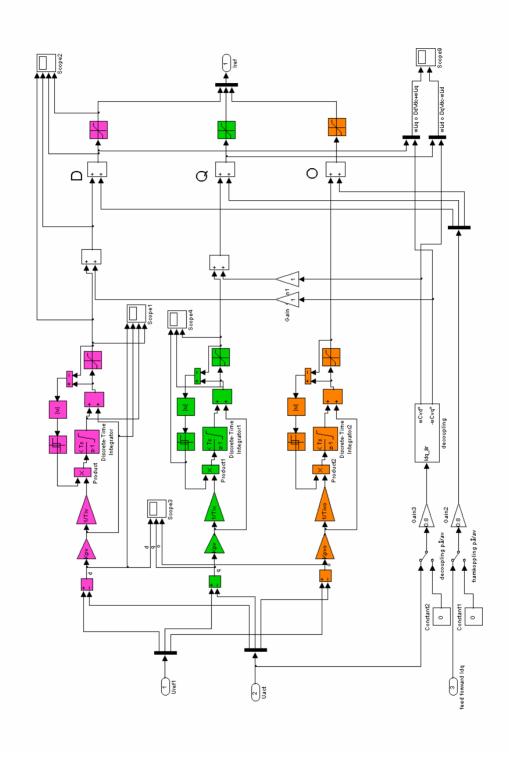

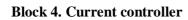

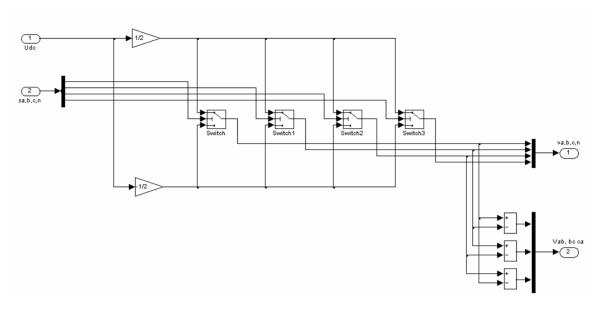

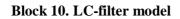

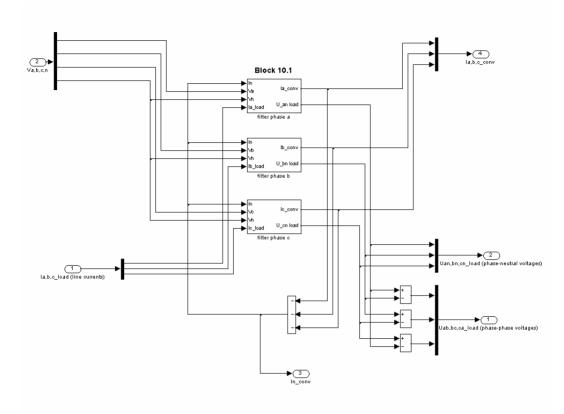

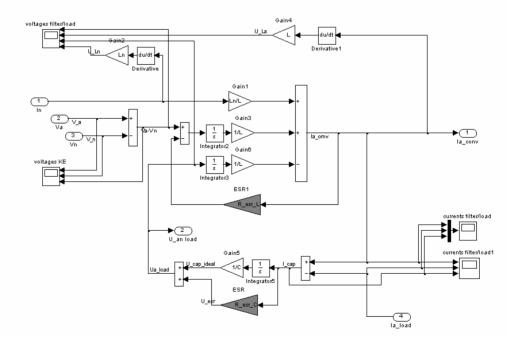

| 3.1 The simulink model of the converter                     | 67  |

| 3.2 Simulations and tests                                   | 76  |

| 3.2.1 Simulated load scenarios                              | 76  |

| 3.2.2 Settings of simulated converter model                 | 77  |

| 4. Results                                                  | 79  |

| 5. Implementation                                           | 92  |

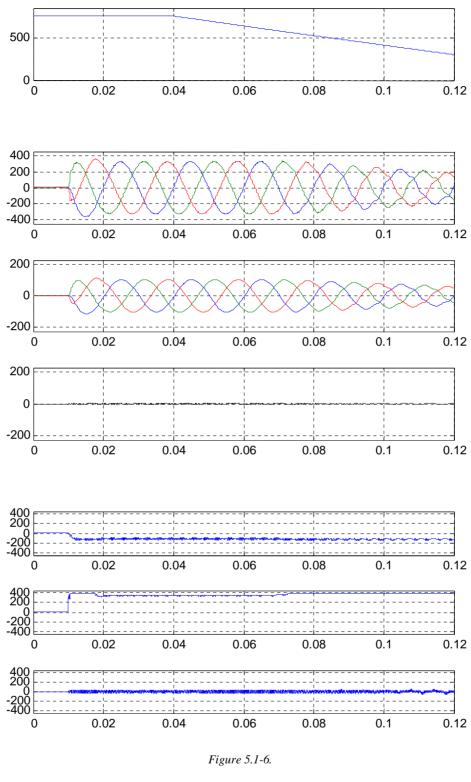

| 5.1 Digital control                                         | 92  |

| 5.2 Proposed main components                                | 96  |

| 6. Conclusions                                              | 97  |

| 6.1 Summary                                                 | 97  |

| 6.2 Discussion for the future                               | 99  |

| References                                                  | 101 |

| Appendix A – Dimensioning the dc link capacitance           | 103 |

| Appendix B – The Simulink model                             | 106 |

| Appendix C – init.m                                         | 113 |

| Appendix D – losscalc.m                                     | 114 |

| Appendix E - Detailed representation control signals        | 117 |

| Appendix F - Losses semiconductors                          | 133 |

| Appendix G - Nomenclature                                   | 137 |

## 1. Introduction

#### 1.1 Background

The company *Land Systems Hägglunds AB* is a leading manufacturer of combat vehicles and all terrain vehicles. Hägglunds has delivered military vehicles to more than 40 countries worldwide. The company is situated in Örnsköldsvik, a town 550 km north of Stockholm. Land Systems Hägglunds employs around 1100 personnel and had in 2004 a turnover of 3 billion Swedish kronor.

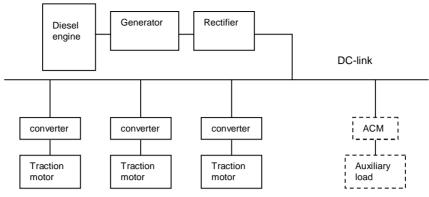

One of Land systems Hägglunds projects for the future is the multi purpose combat vehicle SEP (Swedish abbreviation for "*Splitterskyddad Enhets Plattform*", Modular Armoured Tactical System). The interesting part of SEP from this thesis point of view, is the fact that SEP utilizes a hybrid diesel-electrical drive train (see fig. 1.1-1). From a vehicle point of view this gives advantages like: volume efficiency, fuel efficiency, reduced life cycle costs, reduced environmental impact and increased stealth characteristics. Since the diesel engines are decoupled from the final drives, an increased flexibility in placing of the systems in the vehicle is achieved, as well as an easily installation of two smaller diesel engines instead of one larger. With batteries integrated into the electric drive system, the vehicle is also allowed to be driven silently, with the diesel engines shut down.

There is however a further advantage with the hybrid diesel-electrical drive train. All the mechanical power produced by the diesel engines is transformed into electrical power by generators and rectified before it is transformed back to mechanical power by electrical machines. The central part of this electric transmission is the dc-link and it is here the basic possibility for the purpose of this thesis is provided. Since the generators and the dc-link are dimensioned for the full traction power of the vehicle, they create a possibility of supplying external loads with high power, to the cost of less traction power, at for example stand still of the vehicle. The structure of the drive train of the SEP may be simplified as a dieselelectric UPS (Uninterruptible Power Supply) that feeds the electrical traction motors. If only the first parts of the drive train are considered, the SEP is an UPS.

Figure 1.1-1. Principle diagram of the drive train of SEP.

#### 1.2 Problem

Since the possibility of using the vehicle as an UPS is given, the extension of the usefulness of the SEP it would provide is an advantage that not should be foreseen. Possible loads for the SEP, partly working as an UPS, could be different kinds of internal or external electrical systems and machines, for example electrical tools, motors, PC:s, radios, radar equipment etc.

To make the electrical power useful for an arbitrary load, it needs to be transformed from DC level of the vehicle to a three-phase four-wire 230/400V 50 Hz AC system. To get the most out of the three phase system it should be flexible and stable enough to regulate the output voltage correctly during any load (single-phase load, two-phase load, three-phase load or combinations) less than, or equal to nominal load. The ideal case would be if the three-phase connection could be seen as an ordinary connection to the main grid. This forms the need of three line output terminals and one neutral output terminal, as well as a tight control system for the equipment performing the transformation.

#### 1.3 Purpose

The purpose of this thesis is to examine the possibilities of transforming the dc-link voltage in the vehicle to a four-wire three-phase 230/400V 50 Hz AC system by utilization of a power electronic converter. The converter is from now on referred to as the *ACM (Auxiliary Converter Module)*. This is done by studying existing theory, examine different alternative solutions, building a model, performing

simulations on the model and examine the results. The dimensioning process of the main physical components of the converter is also explained.

For this purpose, one need to investigate the effects of unbalanced three phase loads, how the unbalance affects the voltage regulation, and what countermeasures may be used to reduce their impacts. Understanding of the design process of power electronic converters and their control methods, as well as the behavior and representations of unbalanced three phase systems, are therefore needed.

The main objective of the thesis is to provide this understanding.

### 1.4 Delimitation

Due to the always present lack of time and resources, one has to put limitations to the scope of a work. The theory needed for the understanding of the effects, design, model building etc., mentioned in the section above, is covered. Some limiting simplifications are however made in the model and the simulations:

In the model of the converter the dc link voltage is assumed to be ideal. The voltage is not affected by the load connected to the converter or other loads or sources connected to the dc link. Probably there will be a need for some kind of step-up converter with voltage regulation between the dc link of the vehicle and the dc-link used by the converter described in this thesis.

There are only simulations performed with balanced and unbalanced, resistive and inductive loads connected to the converter.

The control systems of the converter are simulated in Matlab and Simulink. Little is covered about the implementation of the control system in software for a real converter (for example C-code for a DSP).

The project is purely theoretical. The construction of a physical converter is not the target of the project. The most obvious limitation is the lack of a prototype of a physical converter for practical tests and verifications of the results obtained from simulations.

#### 1.5 Outline

The ambition of the thesis is to treat, in a structured way, the problems and issues concerning the design of a power electronic converter, working as a provider of a three phase voltage source. The structured outline involves passing through some theory in the first sections of the thesis that the later sections are depending on. The aim is to present the contents of the thesis in a pedagogical and logical order. The content is now presented in short:

Chapter 1 is the introduction.

Chapter 2 handles the theory and is the major part of the thesis. Section 2.1 concerns the basic theory of three-phase systems, unbalanced voltages and currents, and how to represent them. In section 2.2 different load scenarios and their impacts on the converter are presented. Section 2.3 deals with the basic theory of ordinary three phase converters with three half-bridges and their limitations. Section 2.4 expands the three half-bridge converter with a fourth half-bridge to achieve a four legged converter with a neutral connection. In section 2.5 circuit models of the whole converter, including filters and loads, are presented. Section 2.6 deals with dimensioning issues, for example dc-link voltage, switches, switching frequencies and filters. Section 2.7 finally presents a structured method for the design of the control systems for the converter.

Chapter 3 presents a simulation model of the converter. In section 3.1 the construction of the model, built in Matlab and Simulink is thoroughly explained. In section 3.2 the simulation scenarios, based on the load scenarios from section 2.2, are presented.

Chapter 4 gives a presentation of the results from the simulations in chapter 3.

Chapter 5 concerns implementation of a physical converter. Section 5.1 covers some issues concerning a digital control. Section 5.2 gives a suggestion of what hardware to use.

Chapter 6 is an evaluation of the project, as well as a discussion for the future.

## 2. Theory

#### 2.1 Three-phase systems

The project concerns the transformation of the available DC-link voltage to a threephase 400V AC voltage, including a neutral connection. Commonly used subjects in the thesis are for example: phase representation, sequence representation, vector representation, definition of power, Y- and  $\Delta$ -connections and unbalanced voltages and currents. To clarify the methods and concepts, the thesis is opened with a section providing the theory of the above mentioned subjects in short.

#### 2.1.1 Three-phase systems in phasor representation

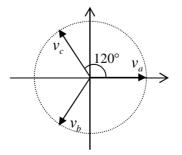

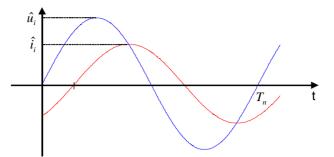

In a three phase system, the three phases are denoted a, b, and c. The frequency f is the same in all three phases. During ideal conditions, the phase components are distributed by  $120^{\circ}$  and their amplitudes are equal. If phase a is taken as reference, phase b lags  $120^{\circ}$  behind phase a. The phasors rotate counterclockwise.

In an ideal situation (like above), the three phase system has equal amplitudes in all three phases and exactly  $120^{\circ}$  phase distribution. The system is then called *symmetric* or *balanced*.

$$\begin{cases} v_a(t) = \hat{V}_a \cos(2pf \cdot t) \\ v_b(t) = \hat{V}_b \cos(2pf \cdot t - 2p/3) \\ v_c(t) = \hat{V}_c \cos(2pf \cdot t - 4p/3) \end{cases}$$

Equation 2.1.1

Figure 2.1-1. Phasor diagram of three-phase system.

#### 2.1.2 Three-phase systems in sequense representation

When phase b lags  $120^{\circ}$  behind phase a, as in eq. 2.1.1, the system is said to have a *positive sequence*. If the rule of ordering the phases in section 2.1.1 is not followed and phase b is taken as the phase lagging  $240^{\circ}$  behind phase a:

$$\begin{cases} v_a(t) = \hat{V}_a \cos(2pf \cdot t) \\ v_b(t) = \hat{V}_b \cos(2pf \cdot t - 4p/3) \\ v_c(t) = \hat{V}_c \cos(2pf \cdot t - 2p/3) \end{cases}$$

Equation 2.1.2

the system is said to have a *negative sequence*. Positive and negative sequence can be visualized as rotating counterclockwise and clockwise, respectively.

An important property of a three phase system with *only* positive sequence, negative sequence, or a sum of both, is that the instantaneous sum of the phase components is zero.

$$v_a(t) + v_b(t) + v_c(t) = 0$$

Equation 2.1.3

If eq. 2.1.3 not holds, the mean value:

$$v_0 = \frac{v_a(t) + v_b(t) + v_c(t)}{3}$$

Equation 2.1.4

is called the *zero sequence* component. The zero sequence component  $v_0$  represents a un-symmetry component which is the same in all three phases. As long as there is no neutral conductor in a three phase system (a three wire system), no zero sequence current is possible. However, in a four wire system the

possibility of zero sequence currents exists.

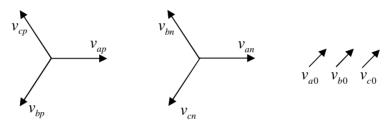

Finally: An un-symmetric, or unbalanced, three phase system can be decomposed into a *positive sequence component*, a *negative sequence component* and a *zero sequence component*:

$$\begin{bmatrix} v_{a}(t) \\ v_{b}(t) \\ v_{c}(t) \end{bmatrix} = \begin{bmatrix} \hat{V}_{a} \cos(2pf \cdot t + r_{a}) \\ \hat{V}_{b} \cos(2pf \cdot t + r_{b}) \\ \hat{V}_{c} \cos(2pf \cdot t + r_{c}) \end{bmatrix} = \begin{bmatrix} \hat{V}_{p} \cos(2pf \cdot t) \\ \hat{V}_{p} \cos(2pf \cdot t - 2p/3) \\ \hat{V}_{p} \cos(2pf \cdot t - 4p/3) \end{bmatrix} + \begin{bmatrix} \hat{V}_{n} \cos(2pf \cdot t) \\ \hat{V}_{n} \cos(2pf \cdot t - 4p/3) \\ \hat{V}_{n} \cos(2pf \cdot t - 2p/3) \end{bmatrix} + \begin{bmatrix} v_{0}(t) \\ v_{0}(t) \\ v_{0}(t) \end{bmatrix}$$

Equation 2.1.5

Where:

$$v_0(t) = \hat{V}_0 \cos(2pf \cdot t + r_0) = \frac{v_a(t) + v_b(t) + v_c(t)}{3}$$

Equation 2.1.6

The decomposition in eq. 2.1.5 is visualized in fig. 2.1-2.

*Figure 2.1-2. Visualization of decomposition in sequences. Positive sequence (left), negative sequence (center), zero sequence (right).*

The transformation between a-b-c components and sequence components is expressed in eq. 2.1.7 and eq. 2.1.8. [2]

| $\begin{bmatrix} X_p \\ X_n \\ X_0 \end{bmatrix} = \frac{1}{3} \begin{bmatrix} 1 & a \\ 1 & a^2 \\ 1 & 1 \end{bmatrix}$ | $\begin{bmatrix} a^{2} \\ a \\ 1 \end{bmatrix} \begin{bmatrix} X_{a} \\ X_{b} \\ X_{c} \end{bmatrix}$ | Equation 2.1.7 |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------|

| $\begin{bmatrix} X_a \\ X_b \\ X_c \end{bmatrix} = \begin{bmatrix} 1 & 1 \\ a^2 & a \\ a & a^2 \end{bmatrix}$           | $1 \begin{bmatrix} X_p \\ X_n \\ 1 \end{bmatrix} \begin{bmatrix} X_0 \end{bmatrix}$                   | Equation 2.1.8 |

Where X may be voltages or currents and  $a = e^{j2p/3}$  is a displacement with  $120^{\circ}$ .

#### 2.1.3 Y- and $\Delta$ -connections

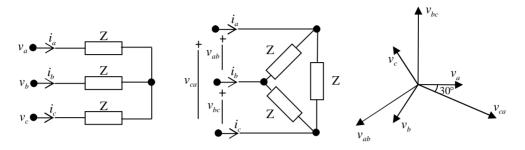

A tree phase load consisting of three impedances  $(Z_1, Z_2, Z_3)$  can be connected in a Y or in a  $\Delta$ , as shown in fig. 2.1-3. Assuming balanced load  $(Z_1=Z_2=Z_3)$ , the voltages can be illustrated as the phasor diagram in fig. 2.1-3 (right).

Figure 2.1-3. Three phase loads. Y connection (left),  $\Delta$  connection, (center), Phasor diagram Y and  $\Delta$  (right).

From the geometry of fig. 2.1-3 (right) it is seen that, compared with the line to neutral voltages (or currents), the line to line voltages (or currents) have their peak values a factor  $\sqrt{3}$  higher and their arguments displaced by 30°. Because of this the total power developed in a three phase load is decreased by a factor 3 when changing the connection from  $\Delta$  to Y. In the following equations  $U_{load}$  is the voltage over *one* of the impedances Z.

#### **Conclusions Y-connection**

$$U_{load} = U_{line-neutral} = U_{line-line} \cdot 1/\sqrt{3}$$

$$I_{load} = I_{line}$$

Equation 2.1.9

$$P_{Y} = 3 \cdot U_{load} \cdot I_{load} \cdot \cos r = \frac{(U_{line-line})^{2}}{|Z|} \cdot \cos r$$

#### Conclusions $\Delta$ -connection

$$U_{load} = U_{line-line}$$

$$I_{load} = I_{line} \cdot 1/\sqrt{3}$$

Equation 2.1.10

$$P_{\Delta} = 3 \cdot U_{load} \cdot I_{load} \cdot \cos r = 3 \cdot \frac{(U_{line-line})^2}{|Z|} \cdot \cos r$$

#### Equivalent Y

During balanced loads, it is of no concern, from the standpoints of dynamics and control, if the load is connected in Y or  $\Delta$ . A  $\Delta$  connected load can be treated as if it were connected in a Y, but with all the impedances reduced to1/3 of the actual values. This is called an *equivalent Y*. [1]

#### 2.1.4 Three-phase systems in vector representation in fixed coordinates

#### The system expressed as a vector in two dimensions

Assuming a balanced three phase three-wire system, following equation holds [2]:

$$X_a(t) + X_b(t) + X_c(t) = 0.$$

Equation 2.1.11

Where X may be voltages or currents.

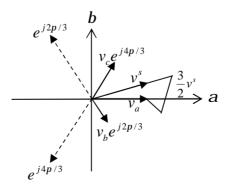

This means that the system is over-determined and that one of the components always can be expressed in the other two. Therefore it's possible to describe the system as equivalent two phase system, with two perpendicular axes, denoted as a and b. These axes are considered to be the real and imaginary axes in a complex plane. The two components, a and b forms a vector  $\overline{X}_{ab}(t)$ . The three phase/two phase transformation is given by eq. 2.1.12:

$$\overline{X}_{ab}(t) = X_{a}(t) + jX_{b}(t) = \frac{2}{3} \left[ X_{a}(t) + e^{j2p/3} X_{b}(t) + e^{j4p/3} X_{c}(t) \right]$$

Equation 2.1.12

Fig. 2.1-4 shows the construction of the vector in a - b -coordinates graphically.

Figure 2.1-4. Construction of the vector in alpha-beta-coordinates.

The transformation between a-b-c coordinates and a - b coordinates is expressed in eq. 2.1.13 and 2.1.14.

$$\begin{bmatrix} X_{a}(t) \\ X_{b}(t) \end{bmatrix} = \begin{bmatrix} 2/3 & -1/3 & -1/3 \\ 0 & 4 & 4/4 \xrightarrow{7}_{1} 4 & 4/4 \xrightarrow{7}_{3} 4 \\ 1/2 & \sqrt{3} & 4 & 4/4 \xrightarrow{7}_{3} 4 \\ 1/2 & \sqrt{3} & 4 & 4/4 \xrightarrow{7}_{3} 4 \\ X_{c}(t) \end{bmatrix} \begin{bmatrix} X_{a}(t) \\ X_{c}(t) \end{bmatrix}$$

Equation 2.1.13

$$\begin{bmatrix} X_{a}(t) \\ X_{b}(t) \\ X_{c}(t) \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -1/2 & \sqrt{3}/2 \\ -1/2 & \sqrt{3}/2 \\ -1/2 & \sqrt{3}/2 \\ T_{1}^{-1} & 4 & T_{2}^{-1} \\ T_{1}^{-1} & 4 & T_{2}^{-1} \\ T_{1}^{-1} & 4 & T_{2}^{-1} \end{bmatrix} \begin{bmatrix} X_{a}(t) \\ X_{b}(t) \end{bmatrix}$$

Equation 2.1.14

#### The system expressed as a vector in three dimensions.

When the three wire system above is extended with a forth neutral wire, the possibility of a zero sequence load current is given. Because of this eq. 1.1.11 does *not* necessarily hold [2].

$$X_{a}(t) + X_{b}(t) + X_{c}(t) \neq 0$$

Equation 2.1.15

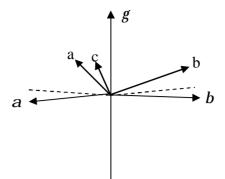

This means that the systems components are truly independent variables and could not be mapped into a two dimensional vector. Instead a *three dimensional* vector, in a three dimensional space with the orthogonal a - b - g-coordinates is used.

$$X_{abg}(t) = X_a(t) + jX_b(t) + kX_g(t)$$

Equation 2.1.16

Fig. 2.1-5 demonstrates how the three phasors in a-b-c may relate to the a - b - g - coordinate system.

*Figure 2.1-5. Relationship between the phasors in a-b-c and the alpha- beta-gamma-coordinate system.*

The transformations between a-b-c coordinates and a - b - g -coordinates are expressed in eq. 2.1.17 and 2.1.18.

$$\begin{bmatrix} X_{a}(t) \\ X_{b}(t) \\ X_{g}(t) \end{bmatrix} = \frac{2}{3} \begin{bmatrix} 1 & -1/2 & -1/2 \\ 0 & \sqrt{3}/2 & -\sqrt{3}/2 \\ 1/2 & 4 & 42 \\ T_{2} & 4 & 44 \\ T_{2} & T_{2} &$$

#### 2.1.5 Vector representation in synchronous coordinates

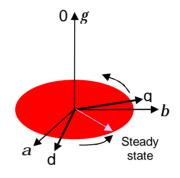

In a system, during steady state, the vector representations above would both be rotating in their a - b or a - b - g-coordinate systems. The controllers for such a system would have constantly oscillating reference signals even at steady state, which would lead to stationary errors in the output signals [2].

To avoid this problem and achieve a stationary DC operating point at steady state (at least in a balanced system, which will be discussed later), the system is transformed into the rotating d-q- or d-q-0-coordinate system. The d-q- or d-q-0-transformation can be regarded as an observation of the rotating vector from a coordinates system that rotates with the same frequency as the fundamental frequency of the vector in the a - b -plane. Since the a - b to d-q transformation

just is a simplification of the a - b - g to d-q-o transformation, only the latter will be dealt with here.

Fig. 2.1-6 demonstrates how the fixed coordinate system in a - b - g relates to the rotating coordinate system in d-q-0. As can be seen, the d and q axes rotate on the a - b plane, while the o axis essentially is the preserved g axis.

Figure 2.1-6. Relationship between the alpha-beta-gamma- and d-q-o-coordinates.

The transformation from a - b - g -coordinates to d-q-0-coordinates is expressed in eq. 2.1.19.

$$\begin{bmatrix} X_{d}(t) \\ X_{q}(t) \\ X_{0}(t) \end{bmatrix} = \begin{bmatrix} \cos(wt) & \sin(wt) & 0 \\ -\sin(wt) & \cos(wt) & 0 \\ \mathbf{1} & \mathbf{4} & \mathbf{4} & \mathbf{4} & \mathbf{2} & \mathbf{4} & \mathbf{4} & \mathbf{4} \\ \mathbf{1} & \mathbf{1} & \mathbf{1} & \mathbf{4} & \mathbf{4}$$

Physically, for a vector in the d-q-0-coordinates, the d-component is the reactive component and the q-component is the active component (voltage or current).

#### Direct transformation a-b-c to d-q-o

Later, in models and simulations, transformations will be made directly from phasor representation in a-b-c to vector representation in d-q-0. This is done by combining  $T_2$  and  $T_3$ , expressed in eq. 2.1.20 and eq. 2.1.21.

Equation 2.1.20

$$\begin{bmatrix} X_{a}(t) \\ X_{b}(t) \\ X_{c}(t) \end{bmatrix} = \begin{bmatrix} \cos(wt) & -\sin(wt) & 1 \\ \cos(wt - \frac{2p}{3}) & -\sin(wt - \frac{2p}{3}) & 1 \\ \cos(wt + \frac{2p}{3}) & -\sin(wt + \frac{2p}{3}) & 1 \\ \cos(wt + \frac{2p}{3}) & -\sin(wt + \frac{2p}{3}) & 1 \\ \mathbf{14444}^{3}\mathbf{442444}^{3}\mathbf{44244}^{3}\mathbf{43} \mathbf{43} \end{bmatrix} \begin{bmatrix} X_{d}(t) \\ X_{q}(t) \\ X_{0}(t) \end{bmatrix}$$

Equation 2.1.21

#### 2.1.6 Unbalanced system

In most cases a converter is designed under the assumption that the load is balanced and an unbalanced load is treated as an abnormal condition. However, in the real world, as well as in the proposed use for the converter in this project, unbalanced loads are expected. Unbalanced loads will result in unbalanced load currents, which in turn, with insufficient control, may cause unbalanced output voltages [2].

Since the load conditions have impacts on the performance and design of the converter, it will now be shown how unbalance appears and behave in different representations, as well as how unbalance can be defined.

#### Unbalance in a-b-c phase representation

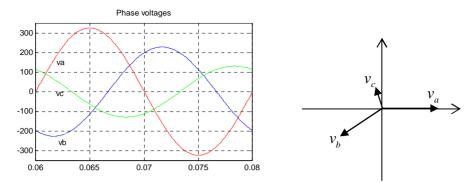

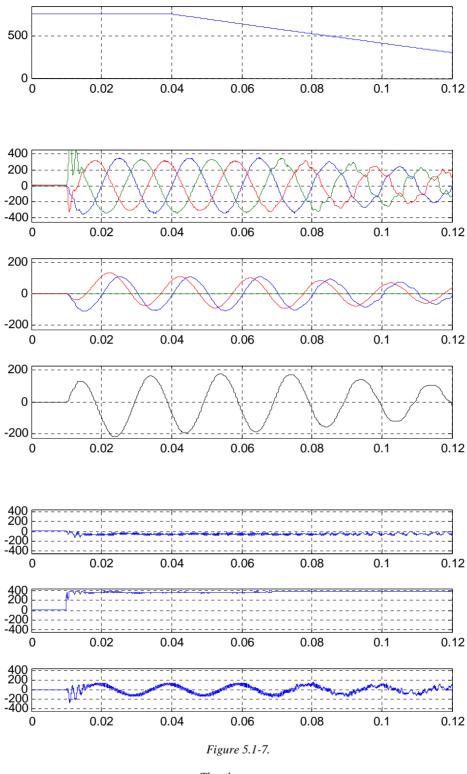

Compared to what was said in section 2.1.1, unbalance or asymmetry in phase representation is characterized by phasors with different peak values and/or phase distributions different from  $120^{\circ}$ . An example of unbalanced phase voltages and phasors is shown in fig. 2.1-7. Compare with fig 2.1-1.

Figure 2.1-7. Phase voltages (left) and phasor diagram (right) of a three-phase unsymmetrical system.

#### Unbalance in sequence representation

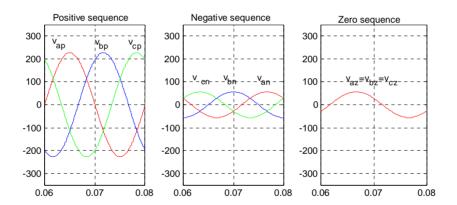

According to section 2.1.2, unbalance or asymmetry will in sequence representation lead to the appearance of negative and/or zero sequences. As an example the phase voltages in fig. 2.1-7 can be split up in a positive, a negative and a zero sequence according to fig. 2.1-8.

Figure 2.1-8. Visualization of decomposition in sequences.

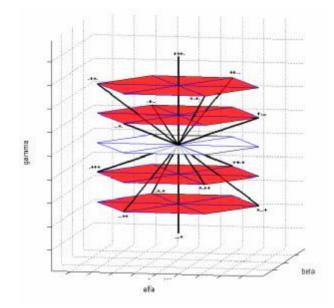

#### Unbalance in a - b - g -coordinate vector representation

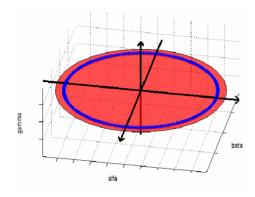

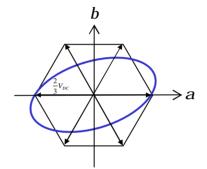

During balanced conditions, the vector described in section 2.1.4, will rotate circularly on the a - b plane. No movement will appear in the g-direction. Fig. 2.1-9a shows the vector trajectory during balanced conditions. Compare it with the sequence representation, where only the positive sequence exists.

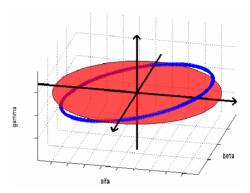

During unbalanced conditions however, if there is a negative sequence, the backwards rotating negative sequence component will be added to the vector as well. The vector will then consist of two components: One part rotating with the fundamental frequency in the positive direction and one superimposed part rotating with the fundamental frequency in the negative direction. This will result in an ellipsoidal vector trajectory on the a - b plane. If there is a zero sequence component, this will appear as a movement with the fundamental frequency in the g-direction. Fig 2.1-9b shows the vector trajectory during unbalanced conditions, assuming that positive, negative, and zero sequences exist. Compare it with the sequence representation during unbalance.

Figure 2.1-9a. Vector trajectory in the stationary coordinate system during balanced conditions.

Figure 2.1-9b. Vector trajectory in the stationary coordinate system during unbalanced condition

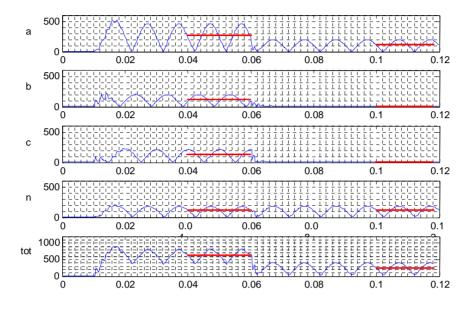

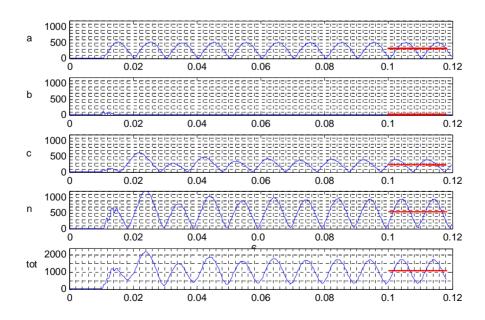

#### Unbalance in d-q-o-coordinate vector representation

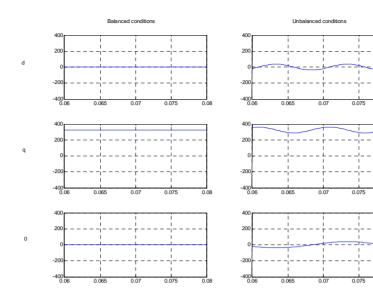

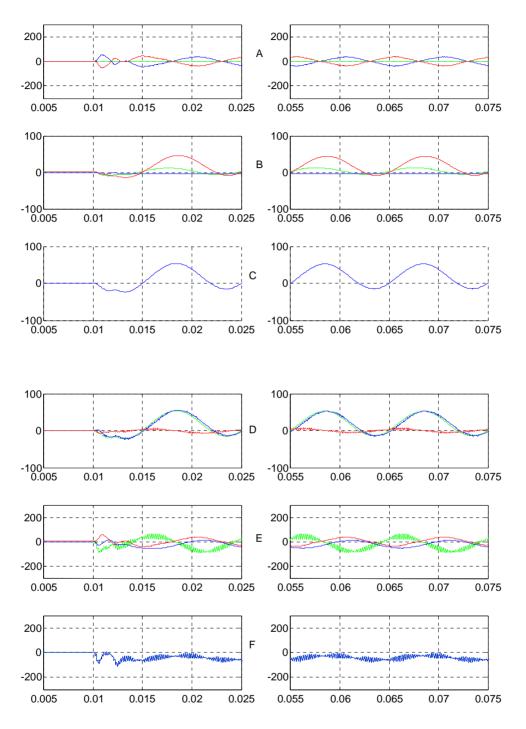

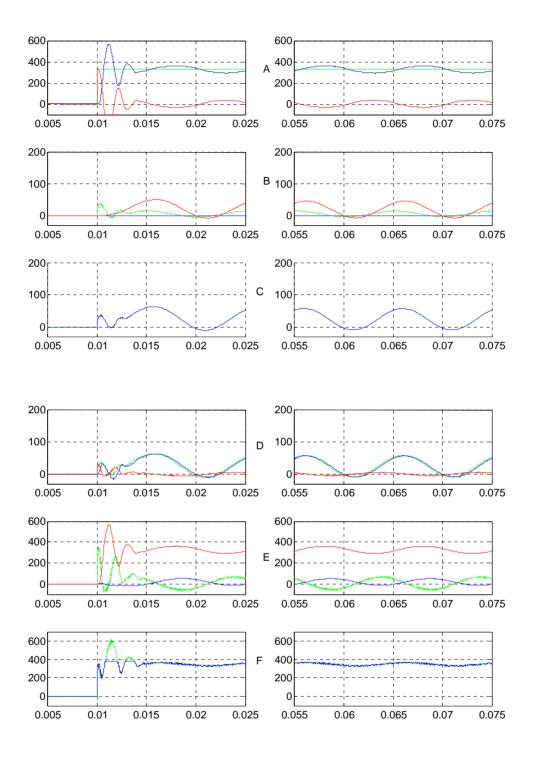

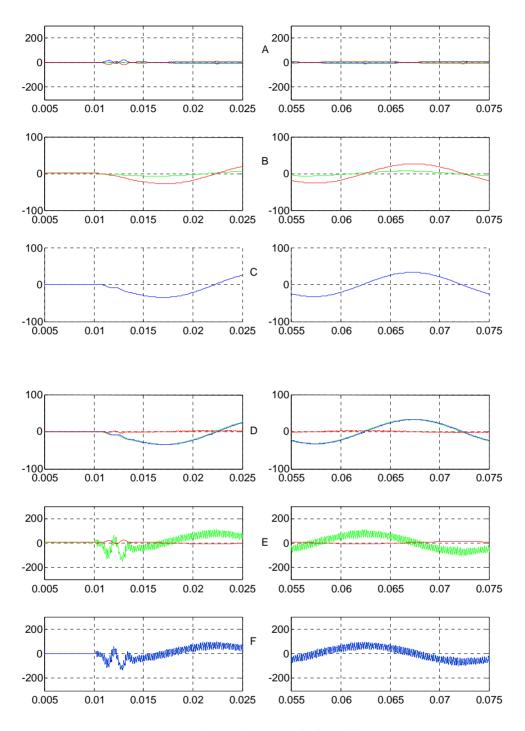

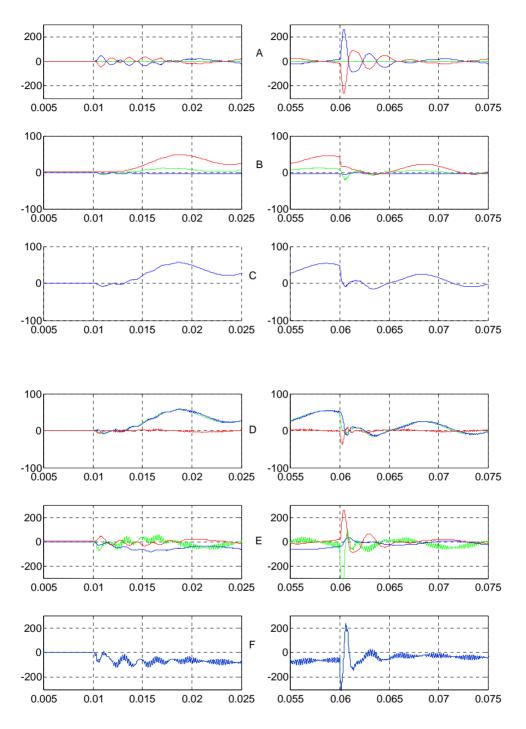

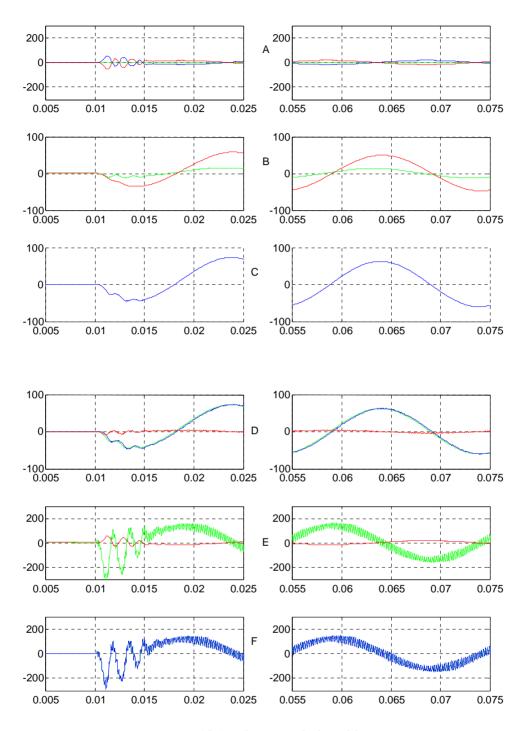

As mentioned in section 2.1.5, the d-q-0-transformation can be regarded as an observation of the rotating vector from a coordinate system that rotates with the same frequency as the fundamental frequency of the vector in the a - b plane. The d and q axis rotate on the a - b plane, while the o axis essentially is the preserved g axis. Thus, unbalance leads to the following behavior of the d-,q- and 0-components of a vector in the d-q-0-coordinate system (see fig 2.1-10b).

Figure 2.1-10a. Behavior of the d- q- and 0components of a vector in the d-q-0coordinate system during balanced conditions.

Figure 2.1-10b. Behavior of the d- q- and 0components of a vector in the d-q-0coordinate system during unbalanced conditions.

Since the added negative sequence causes an ellipsoidal vector trajectory on the a - b plane, both d and q will have a sinusoidal component, at twice the fundamental frequency, added to their stationary DC components.

The zero sequence component will in the 0-direction, as in the g-direction, appear as a sinusoidal component at the fundamental frequency.

#### Definition of unbalance

There are different ways to define unbalanced loads. One way is based on the differences between the maximum per phase load and the minimum per phase load [9]:

$$%UnBal = \frac{Max(per\_phase\_load) - Min(per\_phase\_load)}{Total\_three\_phase\_load} \cdot 100$$

Equation 2.1.22

The drawback of this definition is that no concern is taken of the load power factors. If different phases are connected to loads with different power factors, conditions that very well may have impacts of the converters performance, will not be distinguished [2].

Another way is to base the definition on the sequence representation. According to [2], IEC gives the definition of unbalance in a three phase system as the ratio between the rms values of the negative sequence, or the zero sequence, and the positive sequence.

$$%UnBal_N = \frac{negative\_sequence\_component}{positive\_sequence\_component} \cdot 100 \quad \text{Equation } 2.1.23$$

and

$$%UnBal_0 = \frac{zero\_sequence\_component}{positive\_sequence\_component} \cdot 100 \qquad \text{Equation } 2.1.24$$

In the next chapter, where different load conditions are discussed, both definitions will be used.

#### 2.2 Loads to evaluate

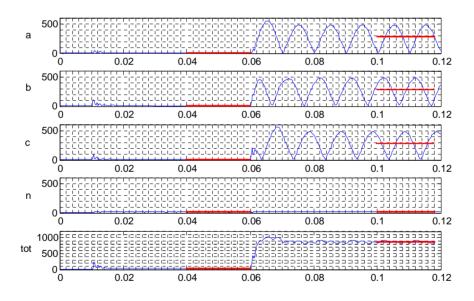

The ultimate goal is to create a balanced three-phase voltage source that, independent of the load condition, always provides the correct voltage. Now, this is more of a target to take aim at, than an in practice achievable goal. The presented simulations of the converter will be limited by a number of different load conditions. To put a limit to the number of experiments, five different load scenarios considered to be reasonable are chosen.

Only resistive and inductive loads, with power factor between 0.2 and 1, are evaluated. Capacitive loads, that are assumed to be rarer, are put on hold for the time being.

Unbalanced loads are assumed to be a common load for the converter and will therefore be carefully examined. The unbalance may be caused by unevenly distributed single-phase loads, or by a combination of single-phase loads and threephase loads.

The converters possibility to regulate voltage during transients is of interest. This will be simulated by sudden steps in the load.

The following scenarios of load conditions will be examined and simulated:

#### Scenario 1

Balanced load with power factor 1 and a step in the load. Starting at low power (approximately no load) and by a step, reach nominal power (50 kVA).

The scenario simulates that the converter starts with no load connected and then is subject to a purely resistive load, corresponding to rated power of the converter.

|              | I <sub>a</sub><br>(current /<br>powerfactor) | I <sub>b</sub><br>(current /<br>powerfactor) | I <sub>c</sub><br>(current /<br>powerfactor) | %unbalance | %neg.seq.<br>unbalance | %zero.seq.<br>unbalance | I <sub>n</sub><br>(current) |

|--------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|------------|------------------------|-------------------------|-----------------------------|

| Before step: | 0 A/ 1                                       | 0 A/ 1                                       | 0 A/ 1                                       | 0 %        | 0 %                    | 0 %                     | 0 A                         |

| After step:  | 72.2 A/ 1                                    | 72.2 A/ 1                                    | 72.2 A/ 1                                    | 0 %        | 0 %                    | 0 %                     | 0 A                         |

Table 2.2-1. Load scenario 1.

#### Scenario 2

Balanced load with power factor 0.2 and a step in the load. Starting at low power (approximately no load) and by a step, reach nominal power (50kVA).

The scenario simulates that the converter starts with no load connected and then is subject to a heavily inductive load, corresponding to rated power of the converter. The interesting part here is to see how well the inverter copes under inductive load conditions.

|              | I <sub>a</sub><br>(current /<br>powerfactor) | I <sub>b</sub><br>(current /<br>powerfactor) | I <sub>c</sub><br>(current /<br>powerfactor) | % unbalance | %neg.seq.<br>unbalance | %zero.seq.<br>unbalance | I <sub>n</sub><br>(current) |

|--------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-------------|------------------------|-------------------------|-----------------------------|

| Before step: | 0 A/ 0.2                                     | 0 A/ 0.2                                     | 0 A/ 0.2                                     | 0 %         | 0 %                    | 0 %                     | 0 A                         |

| After step:  | 72.2 A/ 0.2                                  | 72.2 A/ 0.2                                  | 72.2 A/ 0.2                                  | 0 %         | 0 %                    | 0 %                     | 0 A                         |

Table 2.2-2. Load scenario 2.

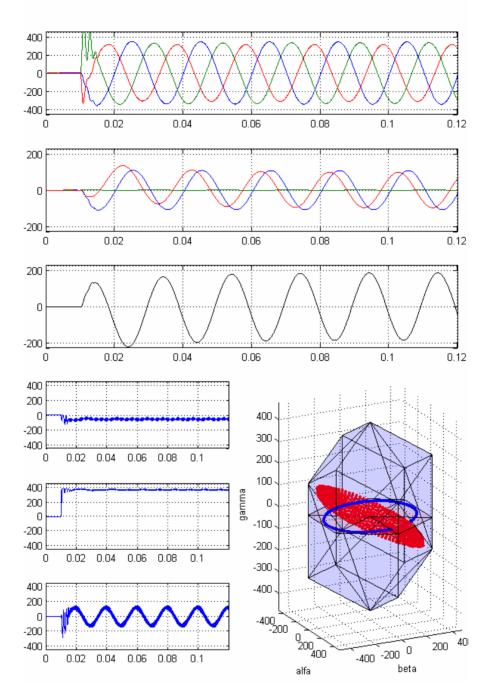

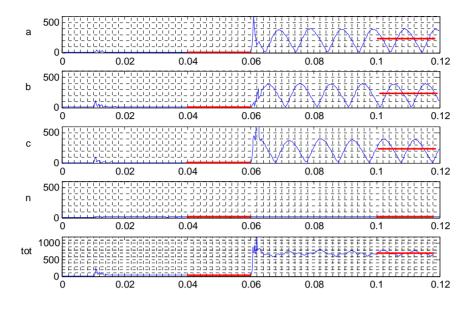

#### Scenario 3

Unbalanced load with power factor 0.8. The phase currents  $I_b$  and  $I_c$  are set equal to 0. The phase current  $I_a$  is set equal to nominal current  $I_n$ .

The scenario simulates that a partly inductive single-phase load is connected to phase a. Phase b and c are not connected. The interesting part here is to see how well the converter copes under unbalanced load conditions.

|         | I <sub>a</sub><br>(current (A)/<br>powerfactor) | I <sub>b</sub><br>(current (A)/<br>powerfactor) | I <sub>c</sub><br>(current (A)/<br>powerfactor) | % unbalance     | % neg.seq.<br>unbalance | % zero.seq.<br>unbalance | I <sub>n</sub><br>(current (A)) |

|---------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-----------------|-------------------------|--------------------------|---------------------------------|

| No step | 72.2 A/ 0.8                                     | 0 A                                             | 0 A                                             | 100 %           | 100 %                   | 100 %                    | 72.2 A                          |

|         |                                                 |                                                 | Table 222 L                                     | ad as an anis 2 |                         |                          |                                 |

Table 2.2-3. Load scenario 3.

#### Scenario 4

A combination of one balanced three-phase load and one single-phase load with a step in the three-phase load. Both loads have a power factor of 0.8. Initially the phase currents  $I_b$  and  $I_c$  are set to  $0.5 \cdot I_{no\min al}$  and the phase current  $I_a$  is set to  $I_{nominal}$ . Then, there is a sudden change in the load so that  $I_b$  and  $I_c$  are set to 0 and  $I_a$  is set to  $0.5 \cdot I_{nominal}$ .

The scenario simulates that one partly inductive three-phase load as well as one partly inductive single-phase load at phase a are connected to the converter. Then the three-phase load is disconnected. The interesting part here is to see how the removal of a quite heavy three-phase load affects the voltage over a simultaneously connected single-phase load.

|              | I <sub>a</sub><br>(current (A)/<br>powerfactor) | I <sub>b</sub><br>(current (A)/<br>powerfactor) | I <sub>c</sub><br>(current (A)/<br>powerfactor) | % unbalance | % neg.seq.<br>unbalance | % zero.seq.<br>unbalance | I <sub>n</sub><br>(current (A)) |

|--------------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------|-------------------------|--------------------------|---------------------------------|

| Before step: | 72.2 A/ 0.8                                     | 36.1 A/ 0.8                                     | 36.1 A/ 0.8                                     | 25 %        | 25 %                    | 25 %                     | 36.1 A                          |

| After step:  | 36.1 A/ 0.8                                     | 0 A                                             | 0 A                                             | 100 %       | 100 %                   | 100 %                    | 36.1 A                          |

Table 2.2-4. Load scenario 4.

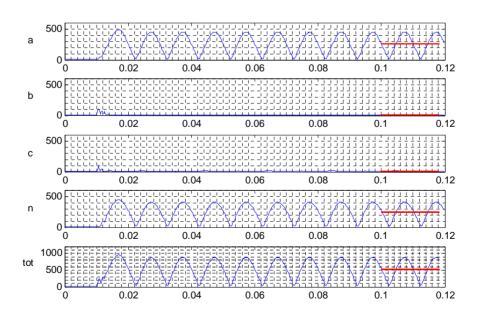

#### Scenario 5

A combination of one heavily inductive single-phase load and one resistive single-phase load. The inductive phase c has a power factor of 0.2.  $I_a$  and  $I_c$  are both set equal to nominal current  $I_{nominal}$ .

The scenario simulates that one heavily inductive single-phase load, as well as one purely resistive single-phase load are connected to the converter. The interesting

part here is to see how the converter behaves under this heavily unbalanced load

|          | I <sub>a</sub><br>(current (A)/<br>powerfactor) | I <sub>b</sub><br>(current (A)/<br>powerfactor) | I <sub>c</sub><br>(current (A)/<br>powerfactor) | % unbalance | % neg.seq.<br>unbalance | % zero.seq.<br>unbalance | I <sub>n</sub><br>(current (A)) |

|----------|-------------------------------------------------|-------------------------------------------------|-------------------------------------------------|-------------|-------------------------|--------------------------|---------------------------------|

| No step: | 72.2 A/ 1                                       | 0 A                                             | 72.2 A/ 0.2                                     | 50 %        | 20 %                    | 120 %                    | 134 A                           |

where the neutral current exceeds the line currents.

#### 2.3 Three leg converters

This section deals with the basic theory of three leg power electronic converters. For this project, as will be shown later, the choice has fallen on the use of a four leg converter. Though, for a start, the three leg converter is examined to demonstrate theory, function and properties of three phase converters.

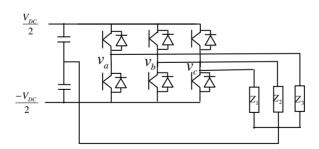

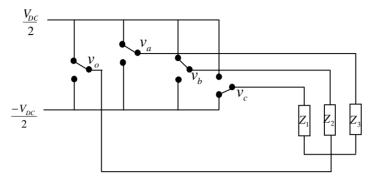

#### 2.3.1 The three leg bridge

The principles for the physical layout of three phase converters, also known as voltage-source converters (VSC:s) are shown in fig. 2.3-1. The bridge is connected to the DC-link, whose voltage is raw material in the creation of the three-phase output voltage. The link voltage is from now on called *dc-link*. The mid potential of the dc-link is defined as neutral.

Figure 2.3-1. Three-phase converter network.

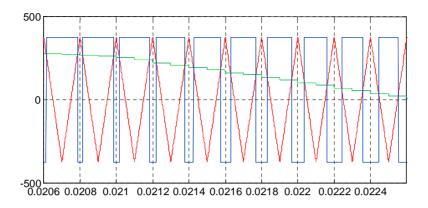

Between the two poles of the dc link, the three half-bridges are connected. Each half-bridge has two power electronic switches. By switching them, between fully conducting and fully blocking, the potentials of each half-bridge ( $v_a$ ,  $v_b$ ,  $v_c$ ), with respect to the mid potential of the dc link, can attain  $\pm V_{DC}/2$ .

The switch states are denoted (a, b, c). With, for example the state (a, b, c) = (+,-,-) (like in fig. 2.3-2 a)  $v_a = V_{DC}/2$  and  $v_b = v_c = -V_{DC}/2$ .

Table 2.2-5. Load scenario 5.

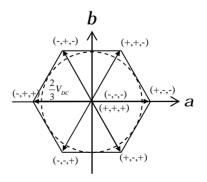

If the potentials  $(v_a, v_b, v_c) = (V_{DC}/2, -V_{DC}/2, -V_{DC}/2)$ , like in the example above, are transformed to a vector in a - b -coordinates (according to eq. 2.1.13), it will attain the value:  $v_a = \frac{2 \cdot V_{DC}}{3}$ ,  $v_b = 0$  (as in fig. 2.3-2 b)

The switch state (a, b, c) can attain the states (+,-,-), (+,+,-), (-,+,+), (-,+,+), (-,-,+) and (+,-,+), who are creating the six possible active values of the voltage vector, and (+,+,+) and (-,-,-), who are creating the zero-vectors, in the *a* - *b* -coordinates according to fig. 2.3-2b.

According to eq. 2.1.13, the output voltage vector  $\mathbf{v}$  in the  $\mathbf{a}$  -  $\mathbf{b}$  -plane can therefore only attain the following values:

$$\begin{split} v_a &= \left\{ 0, \pm \frac{V_{DC}}{3}, \pm \frac{2 \cdot V_{DC}}{3} \right\} \\ v_b &= \left\{ 0, \pm \frac{V_{DC}}{\sqrt{3}} \right\} \end{split} \text{Equation 2.3.1}$$

The maximum modulus of the voltage vector is:

$$|v| = \frac{2 \cdot V_{DC}}{3}$$

Equation 2.3.2

The resulting vector diagram is shown in fig. 2.3-2b.

Figure 2.3-2a. The three phase converter switching network.

Figure 2.3-2b. The attainable voltage vectors.

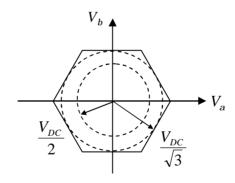

By combining the eight possible switching states, including the zero vectors, using *pulse width modulation* (described below), any voltage vector within the hexagon in fig. 2.3-2b can be generated in average. However, there is an even tighter limitation for the voltage vector to achieve a *linear* modulation, namely the circle that touches the inner sides of the hexagon. The circle has a radius of  $\sqrt{3}/2$  times the maximum modulus of the voltage vector.

Circle radius =

$$V_{\text{base}} = |v|_{\text{max}} \cdot \sqrt{3}/2 = V_{DC}/\sqrt{3}$$

Equation 2.3.3

The radius of the circle is denoted  $V_{\text{base}}$  which is further referred to in the section below.  $\mathbf{v}_{\text{ref}}$  is the desired value of the mean voltage vector.

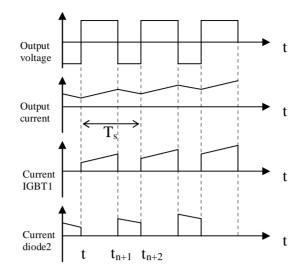

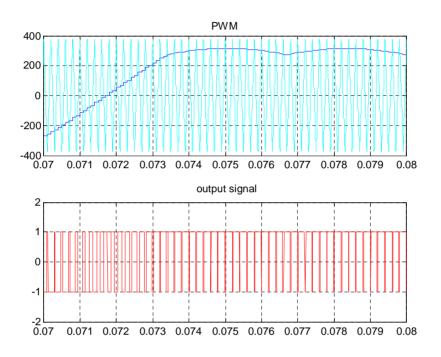

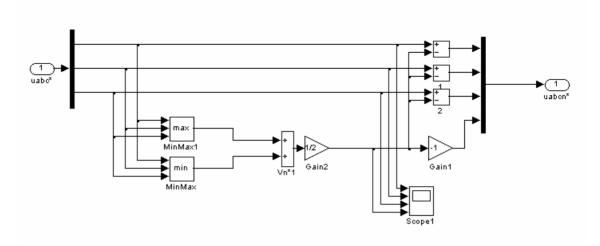

#### 2.3.2 Pulse-width modulation

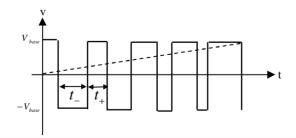

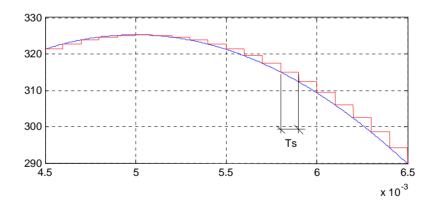

Pulse-width modulation is a way of choosing the sequence of the switch-states above so that the *mean value*  $v_{mean}$ , becomes the desired  $v_{ref}$ . Referring to fig. 2.3-3 the average value can be expressed as:

$$v_{mean} = \frac{1}{T} \left[ t_+ \cdot V_{base} + t_- \cdot \left( -V_{base} \right) \right]$$

Equation 2.3.4

Where *T* is the switch-period and  $t_+$  and  $t_-$  are the periods when the switches, in the current half bridge, are connecting the phase to  $V_{base}$  or  $-V_{base}$  respectively. For example: If  $t_+ = T$ , then  $v_{mean} = V_{base}$ ; if  $t_+ = t_- = T/2$ , then  $v_{mean} = 0$  and if  $t_+ = 0$ ,  $v_{mean} = -V_{base}$ . The resulting voltage waveform is pulse-width modulated and this operation of the inverter is called *pulse-width modulation* (PWM). See fig. 2.3-3.

Figure 2.3-3. Pulse-width modulated waveform and mean value.

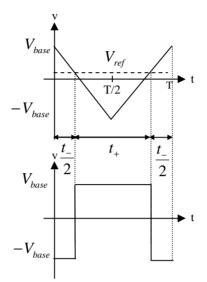

The classical method to generate appropriate switching signals from the reference signal  $v_{ref}$ , is the triangle wave comparison method. The idea is to compare  $v_{ref}$  to a

triangular carrier signal of amplitude  $V_{base}$ . When  $v_{ref}$  is larger than the carrier, the potential of the current half-bridge is set to  $V_{base}$ , and otherwise to  $-V_{base}$ . This is illustrated in fig. 2.3-4. The only difference compared to fig. 2.3-3 is that the switchings are made within the period 0 < t < T and not at the beginning and end of the period.

Figure 2.3-4. Triangle comparison method.

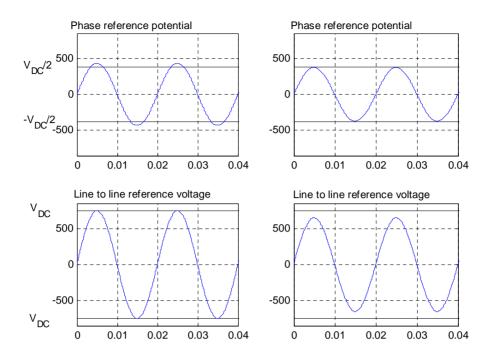

As mentioned above,  $V_{base}$  was originally set to  $V_{base} = V_{DC}/\sqrt{3}$  to achieve a linear modulation. It is proven to be an unreachable voltage with a sinusoidal reference voltage, since only the potentials  $\pm V_{DC}/2$  are available for the potentials delivered from each half-bridge, with respect to the dc-link defined neutral. But, if  $V_{base}$  instead is selected to  $V_{DC}/2$ , it is not possible to utilize all of the available dc link voltage, as shown below.

Since the *line to line* voltage is equal to the line to neutral voltage times  $\sqrt{3}$ ,  $(U_{ab} = U_{an} \cdot \sqrt{3})$ , the maximum line to line voltage from the converter will be (see fig. 6a, b, c):

$$U_{\text{max}\_phase\_phase} = \frac{V_{DC}}{2} \cdot \sqrt{3} = V_{DC} \cdot \sqrt{3}/2 \approx 0.87 \cdot V_{DC}$$

Equation 2.3.5

Since the converter, as later will be seen, will need to deliver as much voltage as possible, this is a drawback.

Figure 2.3-5a. Phase reference potential and line to line reference voltage, compared to available dc link voltage when  $V_{base} = V_{DC sa}/sq.root(3)$

Figure 2.3-5b. Phase reference potential and line to line reference voltage, compared to available dc link voltage when  $V_{base} = V_{DC}/2.$

Figure 2.3-5c.  $V_{base} = V_{DC} / 2$  and  $V_{base} = V_{DC} / sq.root(3)$

A way to achieve full utilization of the dc link voltage, and still have a linear modulation, is to allow some movements of the neutral point. This method is called the *Symmetrized triangle wave comparison method*.

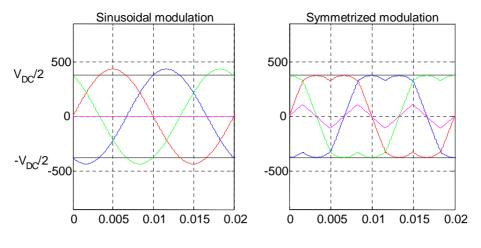

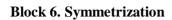

#### 2.3.3 Symmetrized modulation

If the same deviation is added or subtracted from all reference signals ( $v_a$ ,  $v_b$ ,  $v_c$ ), a zero-sequence  $\Delta$  is added. The voltage vector **v** in the *a* - *b* -plane is by that not altered.

By studying the three sinusoidal phase potential waves as a group, one can see that they are moving in an "unsymmetrical way" compared to the center of the triangular wave. For example, when  $v_a$  reaches its maximum value,  $v_b$  and  $v_c$  are at half of their minimum values (See fig. 2.3-6a).

The key to extend the modulation range is to select  $\Delta$  so that:

$$\max(v_a', v_b', v_c') = -\min(v_a', v_b', v_c').$$

Equation 2.3.6

This implies selecting:

$$\Delta = \frac{\max(v_a, v_b, v_c) + \min(v_a, v_b, v_c)}{2}$$

Equation 2.3.7

and

$$(v_a', v_b', v_c') = (v_a, v_b, v_c) - \Delta$$

Equation 2.3.8

where  $(v_a', v_b', v_c')$  are the symmetrized phase voltage references (see fig. 2.3-6b)

Figure 2.3-6a.Sinusoidal modulation. Phase and neutral reference potentials.

By doing this, one can see that the amplitude of the symmetrized phase potential references (fig. 2.3-6b), *compared to the center of the triangular wave*, is less than in the sinusoidal case (2.3-6a). This makes it possible to increase the amplitude of the line to neutral reference voltage by a factor  $2/\sqrt{3}$  and to select  $V_{base} = V_{DC}/\sqrt{3}$ , still using the maximum phase potentials  $\pm V_{DC}/2$ .

Since the line to line voltage is  $U_{ab} = \sqrt{3} \cdot U_{an}$ , the maximum line to line voltage will by this method reach  $\sqrt{3} \cdot V_{DC} / \sqrt{3} = V_{DC}$ , and all of the dc link voltage may be utilized:

$$U_{\text{max}\_phase=phase} = V_{DC}$$

Equation 2.3.9

The line to line voltages will not be affected by the movements in the neutral point. Only the phase potentials and the potential of the neutral, *with respect to the dc link defined neutral point*, is altered.

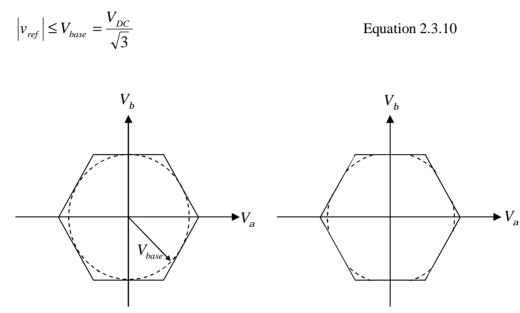

#### 2.3.4 Overmodulation

Using the symmetrized modulation method it is possible, under linear modulation, to reach  $V_{DC}$  as the maximum line to line voltage amplitude and  $V_{DC}/\sqrt{3}$  as the maximum line to neutral voltage amplitude. The limit for reachable output voltages

is thereby set by the dc link. If the reference voltage vector  $\mathbf{v}_{ref}$  reaches outside the limit set by the circle radius  $= V_{DC} / \sqrt{3}$  inside the hexagon in fig. 2.3-7a, the PWM goes into *overmodulation*. Then the output voltage vector will follow the reference vector when the reference vector is inside the hexagon and the hexagon when the reference vector is outside the hexagon (fig. 8b).

In the following simulations, this will be avoided by limiting the reference signal to the linear modulation area:

Figure 2.3-7a. Limit for overmodulation.

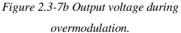

#### 2.3.5 Unbalanced conditions

According to the assumption that the load connected to the converter is balanced, the reference voltage vector will follow a circular trajectory in the a - b-plane. The definition in eq. 2.3.10 for the dc link voltage may then be sufficient for control (see fig. 2.3-8a).

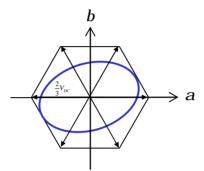

During balanced load conditions, the reference voltage vector will only consist of the positive sequence component (mentioned earlier in section 2.1.6). During unbalanced load however, a negative sequence component will be added to the reference voltage vector as well. This combination of positive and negative sequence voltages will give the trajectory of the reference voltage vector the shape of an ellipse (see fig. 2.3-8b). To be able to control the negative sequence reference

voltage as well as the positive, the major radius of the ellipse must be confined within the inscribed circle of the hexagon, with the radius  $V_{\text{base}}$ .

$$\left|v_{ref\_pos.seq}\right| + \left|v_{ref\_neg.seq}\right| \le V_{base} = \frac{V_{DC}}{\sqrt{3}}$$

Equation 2.3.11

The minimum dc link voltage in the unbalanced case depends on the degree of unbalance of the load. However, a higher dc link voltage will lead to a higher ability of the converter to control the output voltage. This may be even more important if the load is unbalanced.

Figure 2.3-8a.Voltage reference vector trajectory under balanced conditions.

Figure 2.3-8b. Voltage reference vector trajectory under unbalanced conditions.

#### 2.3.6 The creation of a neutral connection

For a three-phase three-wire system, due to the topology, the sum of the three phase currents are zero and the voltage in the neutral point is floating. During balanced load condition this is not a problem. Since the potential in the neutral point during balance always will be zero, the load voltages can be correctly controlled. During unbalanced load conditions however, the line to neutral output voltages will unavoidable become unbalanced as well since the voltage in the neutral point cannot be controlled separately. *The control target of balanced three-phase voltages contradicts with the fact that the zero-sequence current cannot exist* [2]. Only the positive and negative sequence current exists in the system.

In order to make the control target possible, a neutral conductor must be provided so that the zero sequence current can flow through. For a three-phase four-wire system there is a neutral connection that provides current to flow from the neutral point of the load. Here the sum of the three phase currents *and* the neutral current are zero and the voltage in the neutral point may be defined. In this system both positive, negative *and zero* sequence exists.

#### Passive methods

There are passive methods to provide the neutral connection for unbalanced loads [2]:

#### Transformer

The  $\Delta/Y$  transformer is a zero sequence trap. Connecting the  $\Delta$  windings to the inverter and the Y windings to the load, the zero sequence current caused by the load is trapped into the  $\Delta$  windings. Circulating within the transformer winding, it is prevented from traveling back to the inverter and the dc link. Another passive way to provide the neutral connection is to use a zig-zag transformer, which also balances the load to some extent. The zero sequence currents from each phase are shifted at different phase angles, and thus can be canceled with each other.

The problem with the approaches mentioned above, is that they add the transformer to the converter. Transformers for high power are very bulky components.

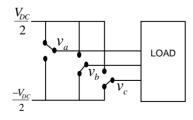

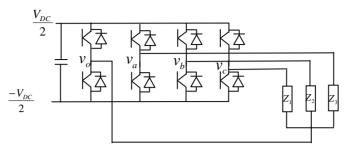

#### Split dc link capacitor

Another passive approach to provide a neutral connection is to use two capacitors to split the dc link and connect the neutral point to the mid-point of the two capacitors (see fig. 2.3-9).

Figure 2.3-9. Split dc link capacitor to provide the neutral point.

There are two problems with this approach. Firstly, the neutral point will be fixed to the middle of the dc link, which will cause poor utilization of the dc link voltage. (The motivation for this is in section 2.3.2, eq. 2.3.5.) Secondly, a huge increase of the capacitance is needed to maintain the dc link voltage ripple at a reasonable level [2].

The ripple will consist of two frequencies, 2w and w. The 2w ripple is caused by the negative sequence load current and the w ripple is caused by the zero sequence load current. The ripple caused by the negative sequence current will occur under unbalanced conditions in any case. The ripple caused by the zero sequence current on the other hand, is directly caused by the connection of the neutral conductor to the split dc link capacitor. See Appendix A for calculations of capacitor size.

#### A fourth leg

By replacing the three leg switching network in fig. 2.3-1 with a four leg switching network, as shown in fig. X10, a four half-bridge power electronic converter is obtained. By tying the neutral connection of the load to the mid point of the fourth half-bridge, the four-legged PWM converter can handle the neutral current caused by an unbalanced load. A balanced output voltage can be achieved with a tightly regulated neutral point.

The method should, compared to the above mentioned approaches, have the advantages of:

- 1. Possibility for high utilization of the dc link voltage.

- 2. No bulky transformers / much smaller dc link capacitors.

Disadvantages are that one more switch pair and one more output filter inductor are added to the design.

This approach seems to be the most preferable and is the one chosen for the project. From now on, when a converter is mentioned, it refers to a four leg converter if nothing else is mentioned.

#### 2.4 The four legged converter

The choice is made to use a converter with a fourth half-bridge to obtain the neutral connection. This converter has much in common with the regular three-phase converter. With the fourth half-bridge, the possibility to connect the neutral is achieved as well. By this a third degree of freedom is added. Instead of using the a - b coordinates, one have to add yet another dimension and work in the a - b - g-coordinate system.

#### 2.4.1 The four leg bridge

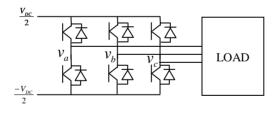

The layout of a four legged three phase converter is shown in fig. 2.4-1.

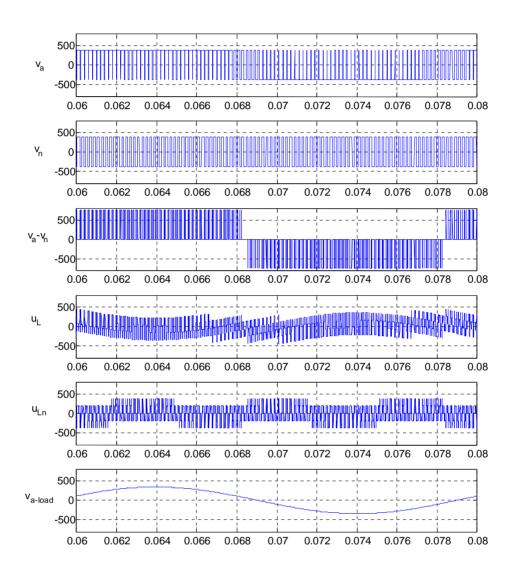

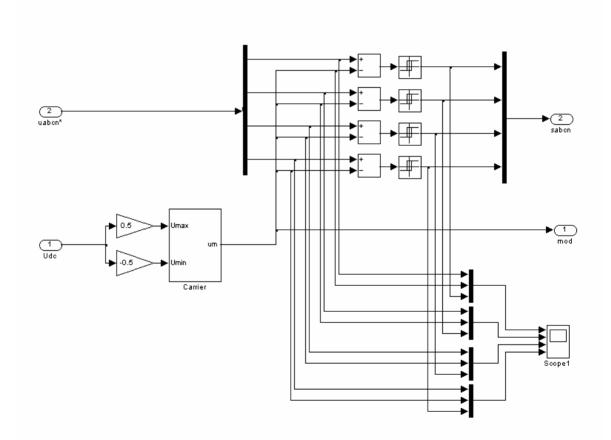

Figure 2.4-1. Four-legged converter network.

Each half-bridge has two power electronic switches. By switching them between fully conducting and fully blocking, the potentials of each half-bridge ( $v_a$ ,  $v_b$ ,  $v_c$ ,  $v_n$ ) can all attain  $\pm V_{DC}/2$ , with respect to the neutral point defined as the mid potential of the dc link. This means that the voltages ( $v_{an}$ ,  $v_{bn}$ ,  $v_{cn}$ ), can attain  $\pm V_{DC}$ .

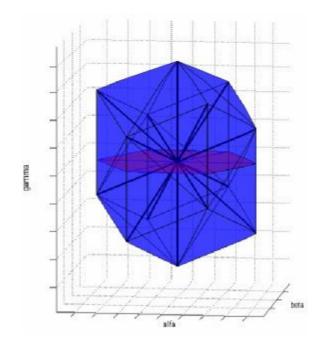

The switch states are now denoted (a, b, c, n), (see fig. 2.4-2). Compared to the 8 switch states in the three half-bridge case, the converter with four half-bridges can attain 16 switch states. Since a third degree of freedom is added with the neutral half-bridge and its possibility of a neutral current, the a - b -coordinate system needs an extension to the a - b - g -coordinate system.

If the output voltage components ( $v_{an}$ ,  $v_{bn}$ ,  $v_{cn}$ ), according to the 16 possible switch states of (a, b, c, n), are transformed (using eq. 2.1.17) into a output voltage vector **v** in the *a* - *b* - *g* -coordinates, it can attain the following values:

$$\begin{aligned} v_a &= \left\{ 0, \pm \frac{V_{DC}}{3}, \pm \frac{2 \cdot V_{DC}}{3} \right\} \\ v_b &= \left\{ 0, \pm \frac{V_{DC}}{\sqrt{3}} \right\} \\ v_g &= \left\{ 0, \pm \frac{V_{DC}}{3}, \pm \frac{2 \cdot V_{DC}}{3} \right\} \end{aligned}$$

Equation 2.4.1

The resulting vector diagram containing all attainable vectors is shown in fig. 2.4-3.

Figure 2.4-2. The four legged converter switching network.

Figure 2.4-3. The output voltage vectors in alfa-beta-gamma coordinates.

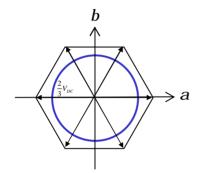

By combining the 16 possible switching states, using *pulse width modulation*, any voltage vector within the *polygon* in fig. 2.4-4 can be generated in average. Compare this with the hexagon in the three half-bridge converter case.

*Figure 2.4-4. The polygon limiting the output voltage vector (reference voltage vector) in the four leg converter case.*

### 2.4.2 Over modulation

The phenomenon is similar to the case with a three leg converter. If the reference voltage vector  $\mathbf{v}_{ref}$  reaches outside the limit set by the polygon in fig. 2.4-4, the PWM goes into *overmodulation*. The output voltage vector will then follow the reference vector when the reference vector is inside the polygon and the surface of the polygon when the reference vector is outside the sphere.

### 2.4.3 Unbalanced conditions

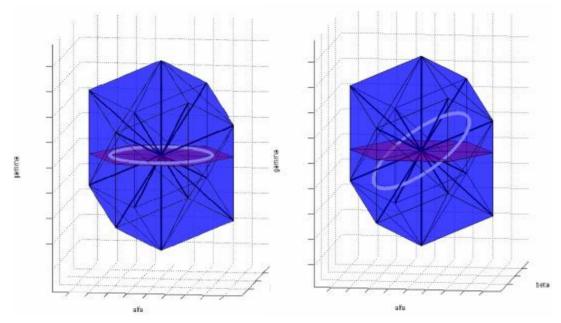

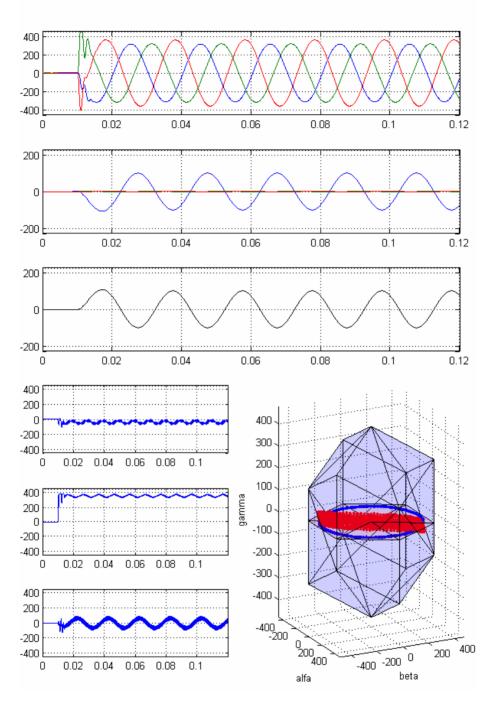

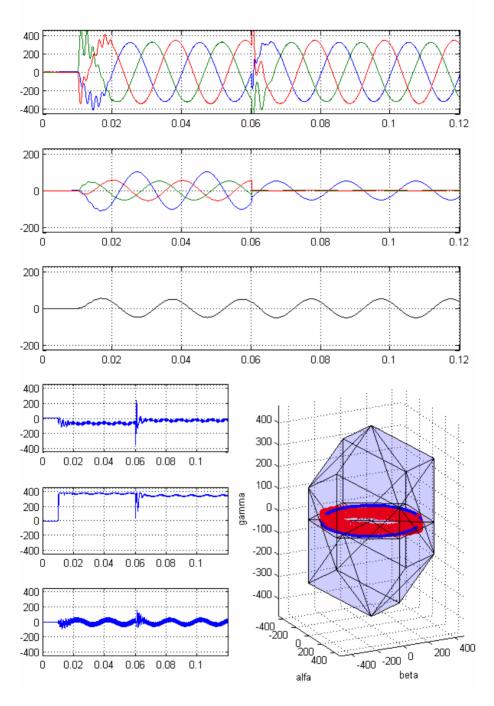

During balanced load conditions, the reference voltage will only consist of the positive sequence component (mentioned earlier in 2.1.6). It will therefore follow a circular trajectory in the a - b -plane (see fig. 2.4-5a).

During unbalanced load however, the reference voltage will not only consist of the positive sequence component, but both negative and zero sequence components may be added as well. The combination of positive, negative and zero sequence voltages will give the trajectory of the reference voltage vector the shape of a skewed ellipse (see fig. 2.4-5b).

Figure 2.4-5a. The reference voltage vector trajectory during balance and the polygon limiting the reference voltage vector in the four leg converter case.

Figure 2.4-5b.The reference voltage vector trajectory during unbalance and the polygon limiting the reference voltage vector in the four leg converter case.

To be able to create both the positive, negative and zero sequences of the reference voltage vector, the major radius of the ellipse must be confined within the polygon, according to fig. 2.4-5b. Obvious, a higher dc link voltage will lead to a higher ability of the converter to control the output voltage. This may be especially important during unbalanced load conditions.

## 2.5 Circuit model of the system

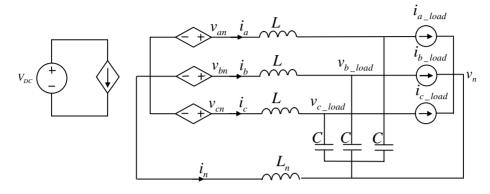

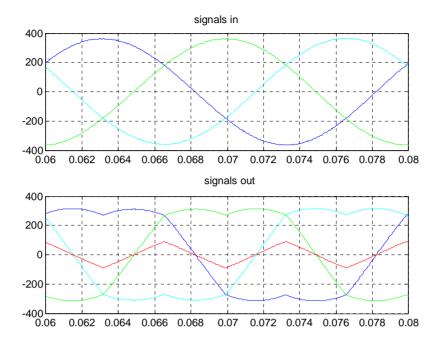

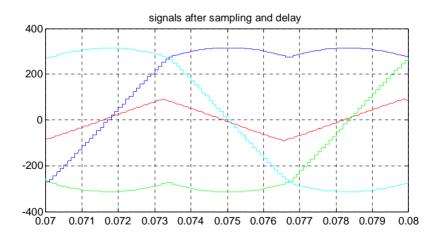

The following section deals with the system in overall. The system consists of the filter inductors, the filter capacitors, the load, and the control voltage sources, which are the voltages from the converter. The model assumes that the switching frequency is very high compared to the fundamental frequency, so that voltage and current ripple are negligible. In this way the switching model can be approximated as an average circuit model. The system is first modeled as the "real" system in a-b-c–coordinates. Then the model is transformed, for control-purposes, to the corresponding system in d-q-0-coordinates.

### 2.5.1 The system in abc-coordinates

The average circuit model of the system is modeled according to fig. 2.5-1.

Figure 2.5-1. The average circuit model in a-b-c-coordinates.

Assuming the dc link voltage to be an ideal voltage source  $V_{DC}$ , the control voltage sources  $(v_{an}, v_{bn}, v_{cn})$  can be expressed as:

$$\begin{bmatrix} v_{an} \\ v_{bn} \\ v_{cn} \end{bmatrix} = \begin{bmatrix} v_a - v_n \\ v_b - v_n \\ v_c - v_n \end{bmatrix} = V_{DC} \begin{bmatrix} d_{an} \\ d_{bn} \\ d_{cn} \end{bmatrix}$$

Equation 2.5.1

$(d_{an}, d_{bn}, d_{cn})$  are the phase to neutral duty ratios of the converter.

The differential equations describing the system are expressed as:

$$\frac{d}{dt}\begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = \frac{L_{n}}{L} \cdot \frac{d}{dt}\begin{bmatrix} i_{n} \\ i_{n} \\ i_{n} \end{bmatrix} + \frac{V_{DC}}{L} \cdot \begin{bmatrix} d_{an} \\ d_{bn} \\ d_{cn} \end{bmatrix} - \frac{1}{L}\begin{bmatrix} v_{a\_load} \\ v_{b\_load} \\ v_{c\_load} \end{bmatrix}$$

Equation 2.5.2

$i_a + i_b + i_c + i_n = 0$  Equation 2.5.3

$$\frac{d}{dt} \begin{bmatrix} v_{a\_load} \\ v_{b\_load} \\ v_{c\_load} \end{bmatrix} = \frac{1}{C} \left( \begin{bmatrix} i_a \\ i_b \\ i_c \end{bmatrix} - \begin{bmatrix} i_{a\_load} \\ i_{b\_load} \\ i_{c\_load} \end{bmatrix} \right)$$

Equation 2.5.4

Where  $(i_a, i_b, i_c)$  are the inductor currents (the converter currents),  $(v_{a\_load}, v_{b\_load}, v_{c\_load})$  are the output capacitor voltages (the load voltages) and  $(i_{a\_load}, i_{b\_load}, i_{c\_load})$  are the load currents.

It can be seen that the system is a second order system with  $V_{DC} \cdot (d_{an}, d_{bn}, d_{cn})^T$  as the input signals, the inductor currents  $(i_a, i_b, i_c)$ , as states and the capacitor voltages  $(v_{a\_load}, v_{b\_load}, v_{c\_load})$  as states as well as output signals.

The phase load currents will in turn depend on the output capacitor voltages and the load impedances as:

$$\begin{bmatrix} i_{a\_load} \\ i_{b\_load} \\ i_{c\_load} \end{bmatrix} = \begin{bmatrix} v_{a\_load} \\ v_{b\_load} \\ v_{c\_load} \end{bmatrix} \cdot \begin{bmatrix} Z_a & Z_b & Z_c \end{bmatrix}$$

Equation 2.5.5

There are problems controlling such a system. The steady state solutions for all the variables are sinusoidal. Due to the time varying nature of the model in a-bc-coordinates, there is no DC operation point for the system. The controllers for a system like this would have sinusoidal reference signals even at steady state, which would lead to constantly stationary errors in the output signals. The control methods for a system like this would also suffer from poor performance due to conflicts among the three phase controllers [2].

To avoid the problems above and achieve a DC operating point at steady state, the system is transformed into the rotating d-q-0-coordinate system

#### 2.5.2 The system in d-q-0-coordinates

In section 2.1.5 its shown how variables, represented in the a-b-c-coordinates, are transformed into representation in d-q-0-coordinates. This is what will be done next to the whole system described in section 2.5.1. [2]

The systems average circuit model in d-q-0-coordinates can be obtained by applying the coordinate transformation matrix  $T_4$  (from section 2.1.5) to both sides of eq. 2.5.2 and eq. 2.5.4. To make the transformations easier, the following expressions may be used:

$$T_{4}\begin{bmatrix} i_{n}\\ i_{n}\\ i_{n} \end{bmatrix} = \begin{bmatrix} 0\\ 0\\ -3 \cdot i_{o} \end{bmatrix}$$

Equation 2.5.6

$$T_4 \frac{dX_{abc}}{dt} = T_4 \frac{dT_4^{-1}}{dt} X_{dq0} + \frac{dX_{dq0}}{dt}$$

Equation 2.5.7

and

$$T_4 \frac{dT_4^{-1}}{dt} = \begin{bmatrix} 0 & -w & 0 \\ w & 0 & 0 \\ 0 & 0 & 0 \end{bmatrix}$$

Equation 2.5.8

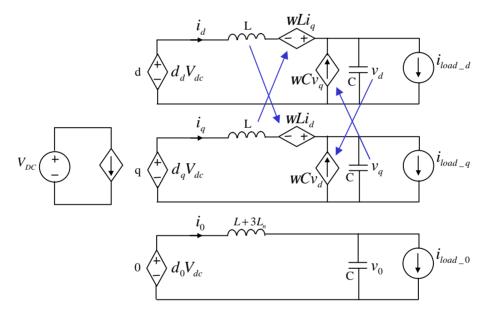

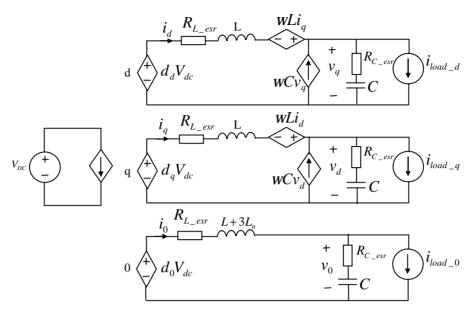

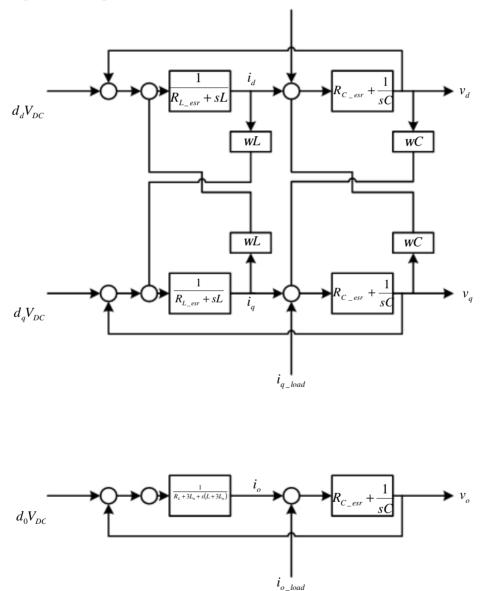

By using them on equation 2.5.2, and 2.5.4, the resulting circuit model in d-q-0-coordinates is expressed according to:

$$\frac{d}{dt} \begin{bmatrix} i_d \\ i_q \\ i_0 \end{bmatrix} = V_{DC} \begin{bmatrix} 1/L & 0 & 0 \\ 0 & 1/L & 0 \\ 0 & 0 & 1/(L+3 \cdot L_n) \end{bmatrix} \begin{bmatrix} d_d \\ d_q \\ d_0 \end{bmatrix} - \begin{bmatrix} 1/L & 0 & 0 \\ 0 & 1/L & 0 \\ 0 & 0 & 1/(L+3 \cdot L_n) \end{bmatrix} \begin{bmatrix} v_d \\ v_q \\ v_0 \end{bmatrix} + W \begin{bmatrix} i_q \\ -i_d \\ 0 \end{bmatrix}$$

Equation 2.5.9

and

$$\frac{d}{dt} \begin{bmatrix} v_d \\ v_q \\ v_0 \end{bmatrix} = \frac{1}{C} \left( \begin{bmatrix} i_d \\ i_q \\ i_0 \end{bmatrix} - \begin{bmatrix} i_{d-load} \\ i_{q-load} \\ i_{0-load} \end{bmatrix} \right) + W \begin{bmatrix} v_q \\ -v_d \\ 0 \end{bmatrix}$$

Equation 2.5.10

Where  $(i_d, i_q, i_0)$  is the inductor current (the converter current),  $(d_d, d_q, d_0)$  is the duty ratios of the converter,  $(v_d, v_q, v_0)$  is the output capacitor voltage

(the load voltage) and  $(i_{d_{load}}, i_{q_{load}}, i_{0_{load}})$  is the load current, now expressed as vectors in the d-q-0-coordinates.

In d-q-0-coordinates, the second order system has  $V_{DC} \cdot (d_d, d_q, d_0)^T$  as the input signals, the inductor currents  $(d_d, d_q, d_0)$ , as states and the capacitor voltages  $(v_d, v_q, v_0)$  as states as well as output signals.

The equivalent circuit model, expressed by eq. 2.5.9 and eq. 2.5.10 is shown in fig. 2.5-2. Note the cross coupling terms between d and q caused by the last terms in eq. 2.5.9 and eq. 2.5.10.

Figure 2.5-2. The average circuit model in d-q-0-coordinates.

If concern is taken to the equivalent series resistances (ESR:s) in the inductors and capacitors, they should be modeled like in fig. 2.5-3 [7].

Figure 2.5-3. The average circuit model in d-q-0-coordinates, with ESR: s.

This is the model later used in the control of the converter.

## 2.6 Dimensioning

This section deals with the choices concerning: Dc link voltage, switching frequencies and parameters of the components in the system. For example how different choices of components affect the properties of the converter, what trade offs have to be made between different characteristics, and some definite specifications and limitations.

#### 2.6.1 Dc-link voltage

The selection of dc link voltage is a trade-off between power switch voltage stress and control margin for transients and unbalanced load conditions. It is of course also limited, unless the use of some step-up converter, by the available dc voltage.

Assuming balanced load conditions and that the wanted line to neutral output voltage is 230VAC, the voltage reference vector is needed to be at least  $230 \cdot \sqrt{2} \approx 325V$ . The dc link voltage would then, according to eq. 2.3.10, need to be at least  $230 \cdot \sqrt{2} \cdot \sqrt{3} \approx 564V$ . There will however be voltage drops during heavy load in the ESR:s (parasitic resistances) in the

output filters. There is also a need for some control margin. A reasonable dc link voltage would therefore be something like 700-750 V.

Under unbalanced conditions however, according to eq. 2.3.11 and fig. 2.6-1, the demand on the dc link voltage is higher than in the balanced case. If the voltage reference vector reference extends outside the circle with  $V_{base}$  as radius, the converter has no possibility to correct all of the control error.

Figure 2.6-1. Example of voltage reference vector trajectory under unbalanced conditions.

#### 2.6.2 Power electronic switches

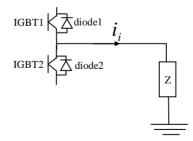

The power electronic switches of the converter need to, under a specified maximum operating temperature, withstand the voltages and current applied to them. They must also, for control issues, be able to switch at a certain rate at reasonable losses. The choice has fallen on using IGBT:s (Isolated Gate Bipolar Transistors). The IGBT:s compromises the abilities of withstanding high voltage and high current density, with the possibility of short switch intervals and low on-state voltage drop [5].

The voltage the IGBT:s needs to withstand is the maximal dc link voltage. For commercial IGBT:s there are different standardized voltage levels. In this case the voltage levels 600V, 1200V and 1700V may be of interest.

On the phase half bridges, the current the IGBT:s has to withstand is the maximal line current during full load. Assuming a nominal 3-phase load for the converter of  $S_n$ , the nominal line current  $I_{line}$  will be:

$$I_{line} = \frac{S_n}{3 \cdot U_{line-neutral}} = \frac{S_n}{\sqrt{3} \cdot U_{line-line}}$$

Equation 2.6.1

On the neutral half bridge, the current the IGBT has to withstand depends on both the maximal load *and* the assumed worst case of unbalanced load. Assuming balanced condition, no current passes trough the neutral half bridge. Assuming 33% zero sequence unbalance (see section 2.1.6), the current trough the neutral half bridge will be equal to the rated per phase current.

### 2.6.3 Switching frequency and converter losses

The switching frequency is a trade-off between thermal losses and control bandwidth.

From a control point of view, the switching frequency should be selected as high as possible. The higher the frequency is, the more often the control signals can be updated. The switching frequency thereby has a direct connection to the possible control bandwidth of the converter.

The temperature normally sets the limitation for the switching frequency when the heat, caused by the losses, no longer can be sufficiently removed by cooling devises. Another limitation may be when the efficiency of the converter is assumed to be too low. In converters for high power, like in this case, most probably cooling issues will be the limiting factor for the switching frequency.

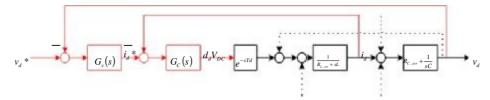

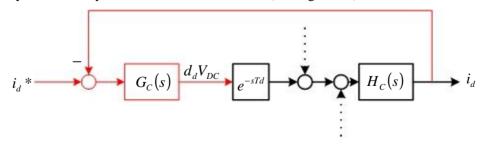

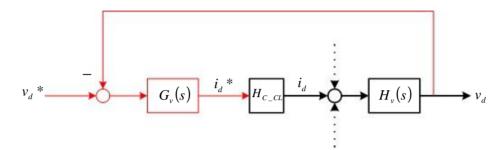

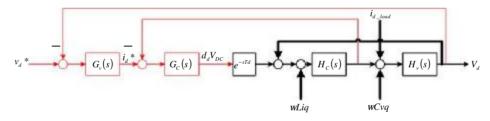

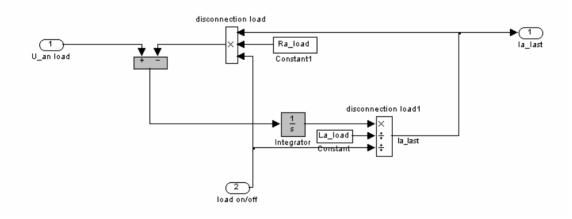

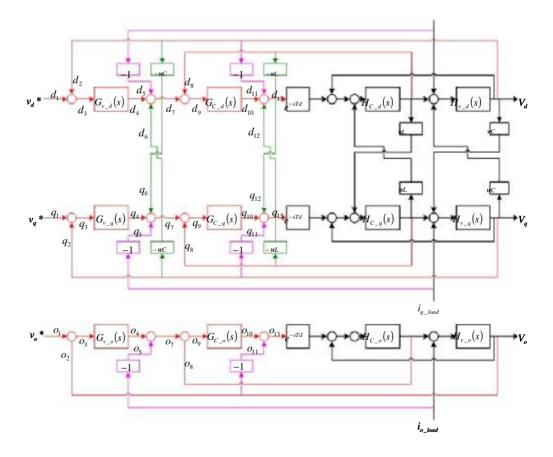

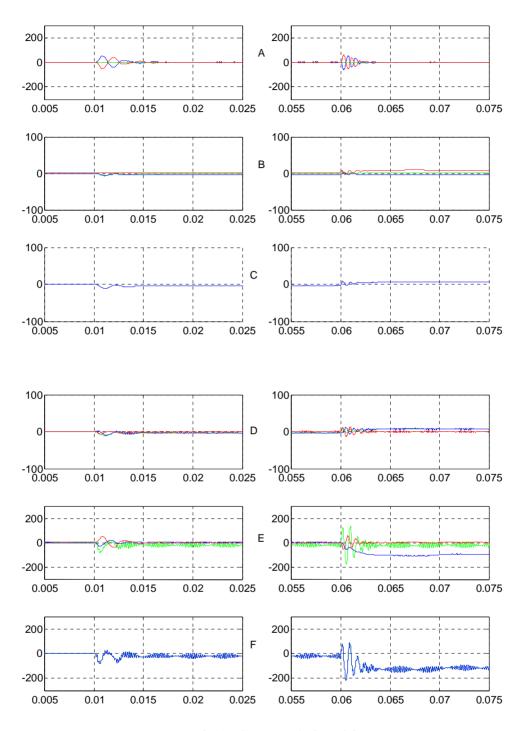

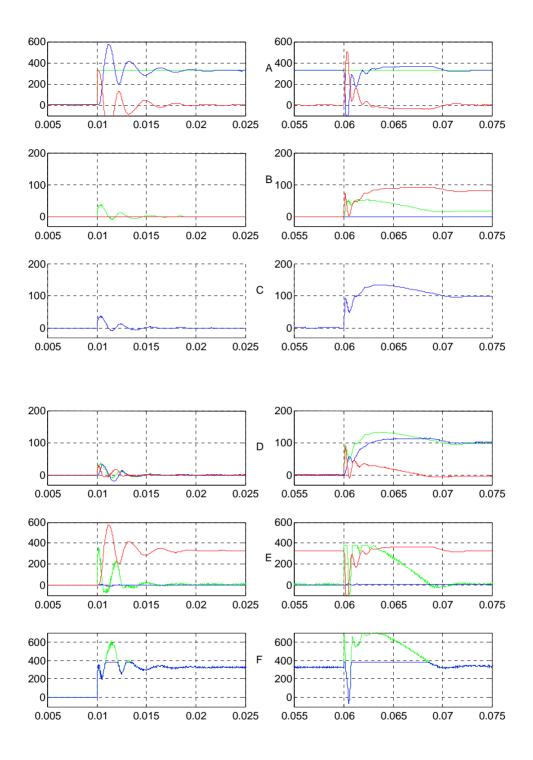

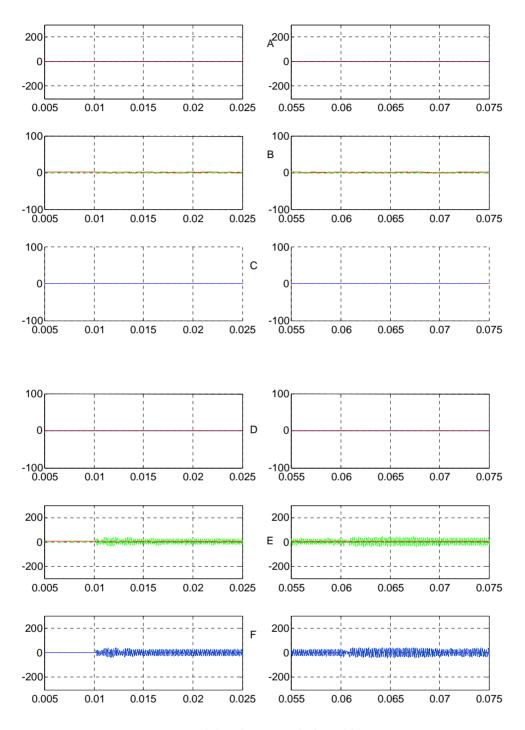

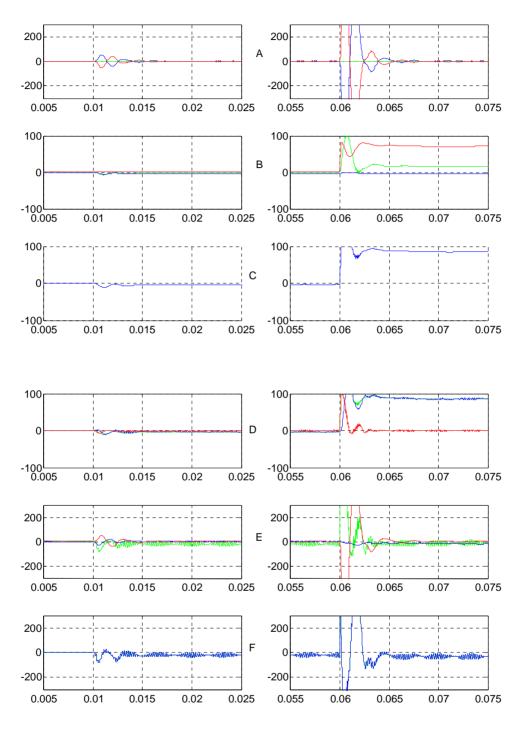

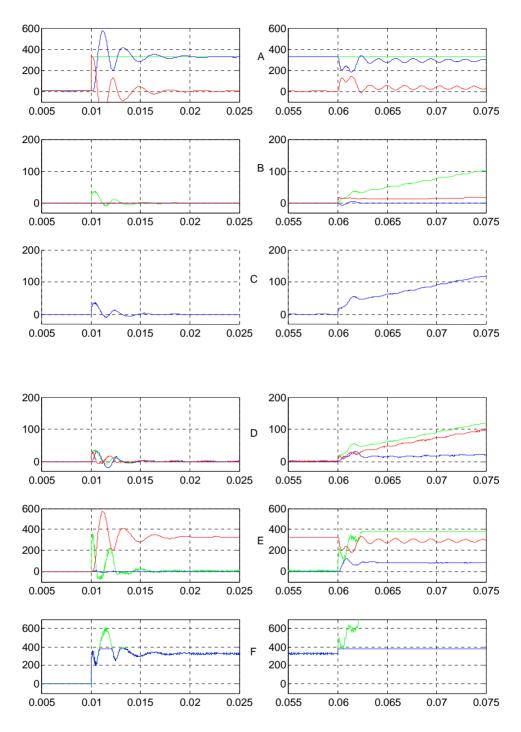

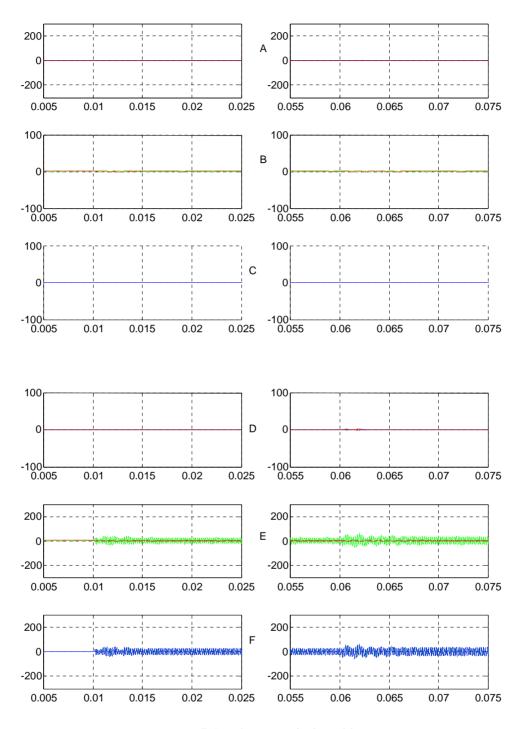

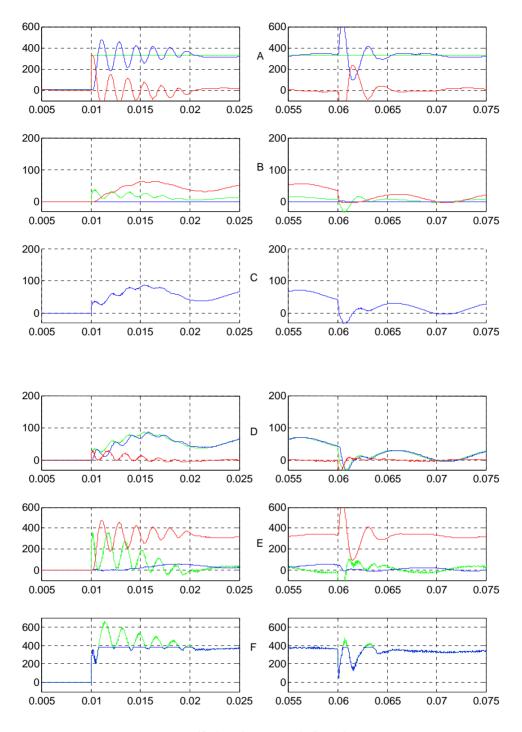

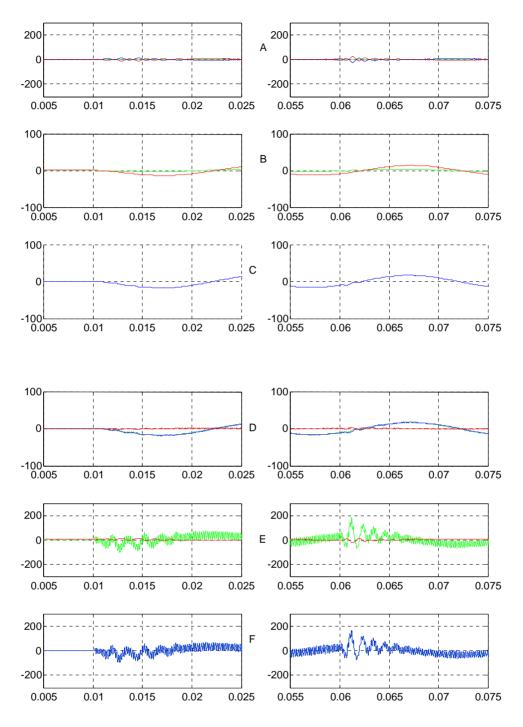

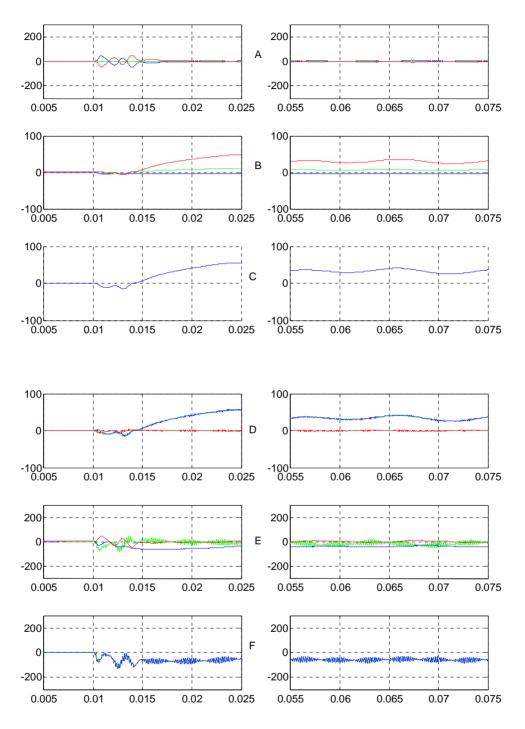

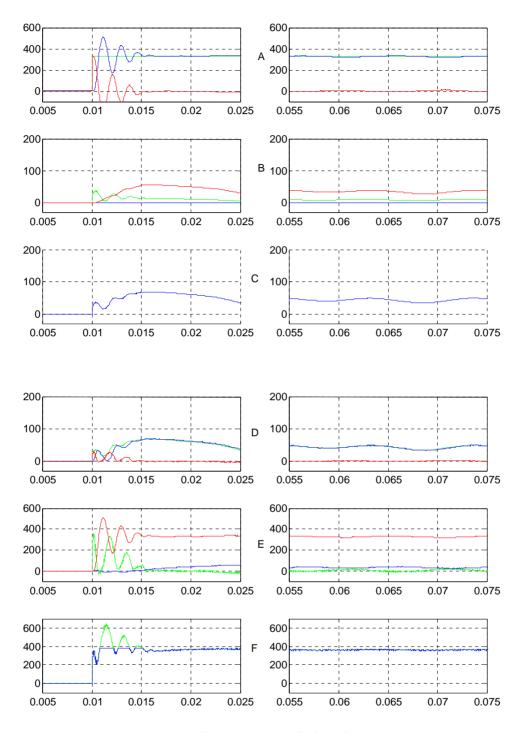

#### Loss calculations